安裝交叉編譯工具鏈?

a. 為什么安裝

因為arm公司的指令集在不斷迭代升級,指令集日益增多,而架構是基于指令集研發的,所以架構不一樣,指令集也不一樣

eg:arm架構使用的是arm指令集?

x86架構使用的是x86指令集

而我們日常開發環境中linux的架構為x86架構? 而開發板子的架構為arm架構他們兩者的架構不一樣,指令集不一樣所以需要交叉編譯工具鏈開彌補這個問題,使不同的架構環境下可以去開發板子

b. 步驟

1.~目錄下創建一個文件夾

2.壓縮包放到這個文件夾中

3.然后解壓到這個文件夾中

4.配置環境變量(四種方法? ?使用當前用戶有效的那種方法 sudo? vi? ~/.bashrc,path后添加:/路徑?)

5.source重啟環境變量? ?source?~/.bashrc

6.查看自己是否完成安裝 (環境變量下路徑名字 -v)

c. 版本gcc-7.5.0

ARM相關概念

a. 匯編指令

編輯器將匯編指令生成代碼,占用代碼段空間

b. 指令集

很多的匯編指令的集合

eg:

特殊寄存器操作(msr/mrs)

跳轉操作指令(b/bl)

偽指令(ldr)

數據搬移指令(mov/mvn)

移動操作指令(lsl/lsr/ror/asr)

位運算指令(add/adc/sub/sbc/mul)

比較指令(cmp)

c. 架構

arm公司隨指令集的不斷迭代,會根據不同的指令集設計出不同的架構,因此架構不一樣對應的指令集不一樣

d. 內核

arm公司會根據不同的架構來設計內核

eg:

stm32mp157aaa=cortex-A7核*2+cortex-M4核

e. SoC

soc又稱片上系統,大家一般喜歡叫做芯片,arm公司其實不生產芯片,而是將內核生產并授權給各個合作的廠商,廠商將這個內核加上一些外設之類的附加控制器(外設),進行二次開發就是所說的芯片了

RISC和CISC指令集區別

RISC精簡指令集(arm架構)

對復雜指令集進行提取一些簡單且常用指令且指令寬度和指令周期是固定的

指令寬度:指令編譯器形成機器碼所占空間大小

指令周期:執行一條指令所需要的時間

驗證

arm-linux-gnueablinf-gcc -marm test.c

arm-linux-gnueabinf-objdump -D a.out > a.dis

vi a.dis

我們會發現從main函數入口后開始 地址偏移的大小都是4

CISC復雜指令集(x86架構)

對著指令的性能有著較高的要求而指令寬度和指令周期沒有固定的要求

驗證:

arm-linux-gnueablinf-gcc ?test.c

arm-linux-gnueabinf-objdump -D a.out > a.dis

vi a.dis

我們會發現從main函數入口后開始 地址偏移大小都不一樣

ARMv7架構和ARMv8架構區別

ARMv7架構是32位架構,而ARMv8架構是64位架構且向下兼容ARMv7架構

ARMv7架構是尋址地址是2^32大小,ARMv8架構尋址地址是2^64大小

ARMv7和ARMv8生成一條匯編指令的大小都是4字節

ARM處理器工作模式

ARM處理器首先分為特權模式和非特權模式

而非特權模式只有user模式

特權模式則又分為異常模式和非異常模式

其中非異常模式只有system模式

而其中異常模式又分為:

FIQ

IRQ

undef模式

SVC模式

data abort模式

prefech adbort模式

而cortex處理器多一個monitor模式(安全監測模式)

以上模式都可以通過軟件和硬件的方式進行切換

且cortex處理器比arm處理器多一個monitor安全檢測模式

寄存器

a. 位置

arm公司會根據不同的指令集設計不同的架構,而根據不同的軟件架構生產不同的內核

而寄存器就存在于內核之中的儲存器之中

訪問 寄存器通過加關鍵詞register進行訪問,只可以用寄存器編號進行,地址不可以

b. 特點

短暫存儲數據,運算速度極快,每個模式都有對應的寄存器,user和system模式公用一個寄存器?

c. 特殊功能寄存器

i. sp

棧指針寄存器,數據入棧和數據出棧時候需要移動棧指針(數據初始化)

ii. lr

鏈接寄存器,用于保存返回地址

iii. pc

程序計數寄存器,用于記錄下一條指令運行的位置

iv. cpsr

用于保存當前程序狀態的寄存器

v. spsr

用于保存cpsr寄存器的數值

d. cpsr寄存器中高4位,低8位作用

n[31]:是否負數標志位

z[30]:是否為0標志位

c[29]:是否進位標志位

v[28]:是否溢出標志位

為1都是確認

I[7]:是否屏蔽IRQ

F[6]:是否屏蔽FIQ

T[5]:狀態位

M[4:0]:模式位

匯編指令格式

數據操作指令

a. 數據搬移指令mov mvn ldr

mov :將立即數,有效數(取反為立即數),寄存器放入目標寄存器中

mvn:取反后放入目標寄存器中

ldr:偽指令,因為大部分的數不是一個有效數和立即數,需要賦值的話可以借助ldr偽指令來實現

b. 移位操作指令lsl lsr asr ror

lsl:邏輯左移,移出補0

lsr:邏輯右移,移出補0

asr:循環右移,低位移出,高位補0?

ror:算術右移,低位移出,高位補符號位

c. 位運算操作指令and orr bic eor

and:與運算, 與0為0 ,與1不變

orr:或運算,或0不變,或1為1?

eor:異或運算,異或0不變,異或1取反

bic:按位清除

d. 算數運算操作指令add adc sub sbc mul

add:相加不考慮進位

adc:相加考慮進位

sub:相減不考慮借位

sbc:相減考慮借位

mul:相乘

e. 比較指令cmp

本質上就是做相減運算,比較兩個數大小關系

跳轉指令 b bl

b:有去無回

bl:有去有回

回的表現在lr寄存器會不會記錄返回地址

特殊功能寄存器操作指令 mrs msr

mrs:向cpsr的值讀到目標寄存器中

msr:向目標寄存器的值寫入目標寄存器中

內存操作指令

a. 單寄存器操作指令ldr str

ldr rd,[rm]向rm值讀入rd中

str rd,[rm]將rd的值寫入rm中

b. 多寄存器操作指令ldm stm

ldm rd,{r0-r5}:將rd的值讀到r0-r5

stm rd,{r0-r5}:將r0-r5的值寫到rd中

c. 棧指針操作指令ldmfd stmfd

棧指針操作指令??

ldmfd sp!,{寄存器列表} :將棧指針寄存器sp中的值讀到寄存器列表中

stmfd sp!,{寄存器列表}:將寄存器列表中的值依次寫入sp寄存器中

混合編程

a. ATPCS規范

ATPCS是Arm?Thumb?Produce Call? standard

arm默認使用的是滿減棧

傳參時默認使用r0-r3寄存器,參數最好不要超過4個

返回值使用r0進行返回

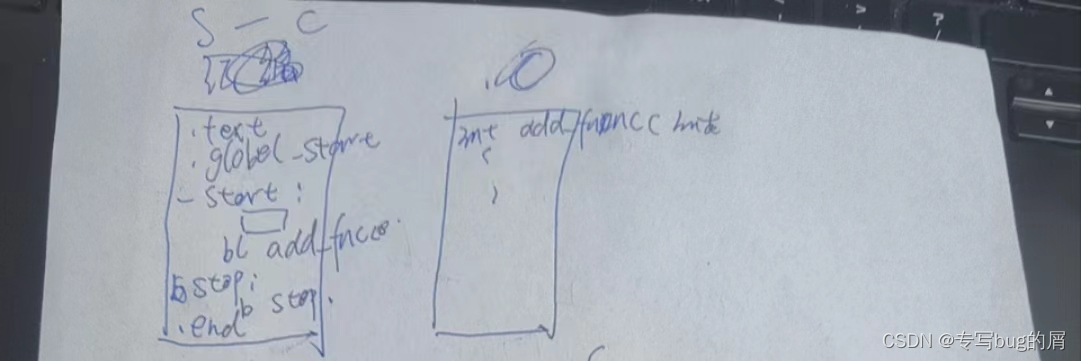

b. 匯編調用C

c. C調用匯編

d. 內聯匯編

Cortex-A7核LED燈實驗

a. 分析硬件電路圖

b. 分析框圖

c. 分析RCC章節

d. 分析GPIO章節

e. 編寫程序

f. 通過串口工具下載程序,觀察實驗現象

如何封裝函數,實現LED燈點亮 PE10 PF10 PE8

a. GPIO引腳初始化函數

b. GPIO引腳操作函數

Cortex-A7核UART實驗

a. 總線概念

b. 連接方式(ST-LINK仿真器)

c. 配置信息

d. 協議

e. 分析框圖

f. 分析RCC章節

g. 分析GPIO章節

h. 分析UART章節

i. 使用串口做過實驗

異常處理流程

a. 異常源

b. 異常源和異常模式之間對應關系

c. 異常處理流程

d. 異常向量表

e. 軟中斷指令

f. 編寫異常處理流程代碼 ?

17. Cortex-A7核中斷實驗

a. 分析電路圖: 操作的對應引腳編號

b. 分析框圖: 分析芯片手冊章節

c. 分析芯片手冊:

i. 分析RCC章節: 使能對應組控制器

ii. 分析GPIO章節: 設置引腳為輸入模式

iii. 分析EXTI章節: 設置引腳觸發方式

iv. 分析GIC章節

d. 編寫代碼

e. 下載調試

18. Cortex-A7核IIC實驗

a. 同步串行半雙工總線:

i. SCL時鐘線

ii. 只有一根雙向的數據線SDA

iii. 按位進行數據傳輸(先發送高位,在發送低位)

b. 外接兩個上拉電阻,作用:在總線為空閑狀態時,總線默認為高電平狀態

c. 單主機多從機模式,在總線上,每一個從機都有自己唯一的7位從機地址

d. 發送器、接收器、主機、從機

e. 時序:起始信號、停止信號、數據傳輸信號、應答/非應答信號

f. 協議:

i. 主機給從機發送一個字節

ii. 主機給從機發送多個連續的字節

iii. 從機給主機發送一個字節

iv. 從機給主機發送多個連續的字節

g. 分析溫濕度傳感器芯片si7006

h. 編寫采集程序:

i. 時序:起始信號、停止信號、數據傳輸信號、應答/非應答信號

ii. 協議:

1. 初始化si7006芯片

2. 采集溫濕度傳感器協議

iii. 通過公式,完成數字量到模擬量之間轉換

19. Cortex-A7核SPI實驗

a. 同步串行全雙工三線/四線總線

b. 主機產生時鐘信號,作用給從機完成數據收發同步

c. 2根單向數據信號線(MOSI / MISO)

d. 單主機多從機模式

e. 四線制單主機多從機:

i. NSS

ii. SCL

iii. MOSI

iv. MISO

f. 三線制單主機單從機

g. SPI總線協議/通信模式: SPI總線邊沿觸發,邊沿采樣

h. IIC總線和SPI總線相同點/不同點

i. 分析M74HC595芯片:

i. 移位寄存器: 移位寄存器時鐘源(上升沿)

ii. 鎖存器: 鎖存時鐘源(上升沿)

iii. 串行一位一位寫入到移位寄存器=>鎖存器=>并行數據輸出

20. Cortex-A7核PWM實驗

a. PWM相關概念:脈沖、周期、頻率、占空比

b. 分析框圖(rcc / gpio / tim4)

c. RCC章節:使能對應組控制器

d. GPIO章節:設置復用功能模式,以及對應復用功能

e. TIM章節:方波信號

和重寫(Override)的區別。重載的方法能否根據返回類型進行區分?)

的性能(來自OpenAI DevDay 會議))

![劍指offer》15--二進制中1的個數[C++]](http://pic.xiahunao.cn/劍指offer》15--二進制中1的個數[C++])

)