引言

DFT是ASIC芯片設計流程中不可或缺的環節。其主要目的是在芯片前端設計驗證完成后插入一些諸如寄存器鏈等可供測試的邏輯,算是IC后端設計的范疇。主要是在ASIC芯片流片完成后,通過這些已插入的邏輯,檢測流片得到的芯片的制造質量。檢測一些固定故障等。

學習參考

- 數字系統測試和可測試性設計。【美】賽納拉伯丁 - 納瓦比 著。原本和譯本。

- 修真院講解視頻。

- E課網 DFT 課程。

- 華中科技大學IC設計中心 陳新武 講稿《集成電路測試方法研究》。

- Design-for-Test: Scan and ATPG Training?Student Workbook ,Copyright ?Mentor Graphics。

簡單理解DFT

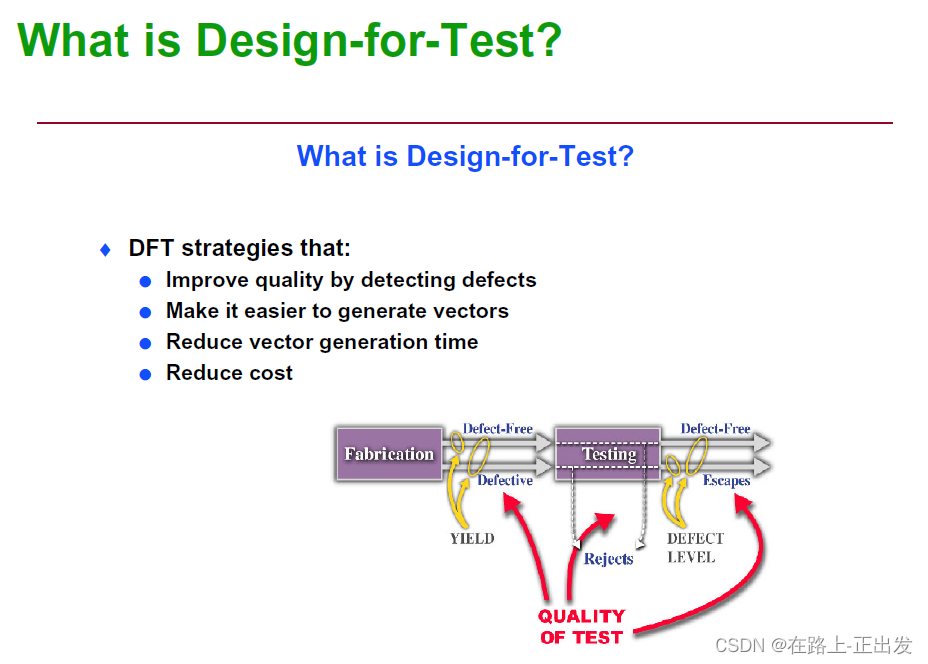

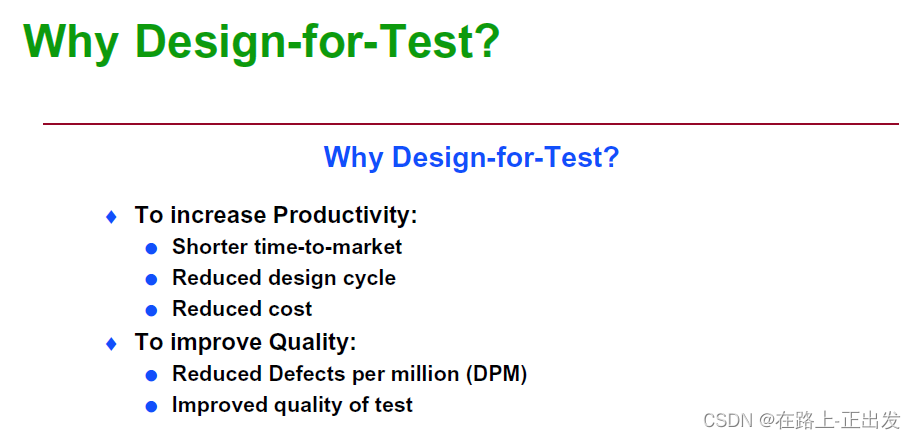

增加一些硬件開銷來實現一些輔助性測試設計。需要產生一些高效的測試向量用于測試。DFT不只是插入一些設計的邏輯還包括具體的測試向量產生、測試結果分析等。

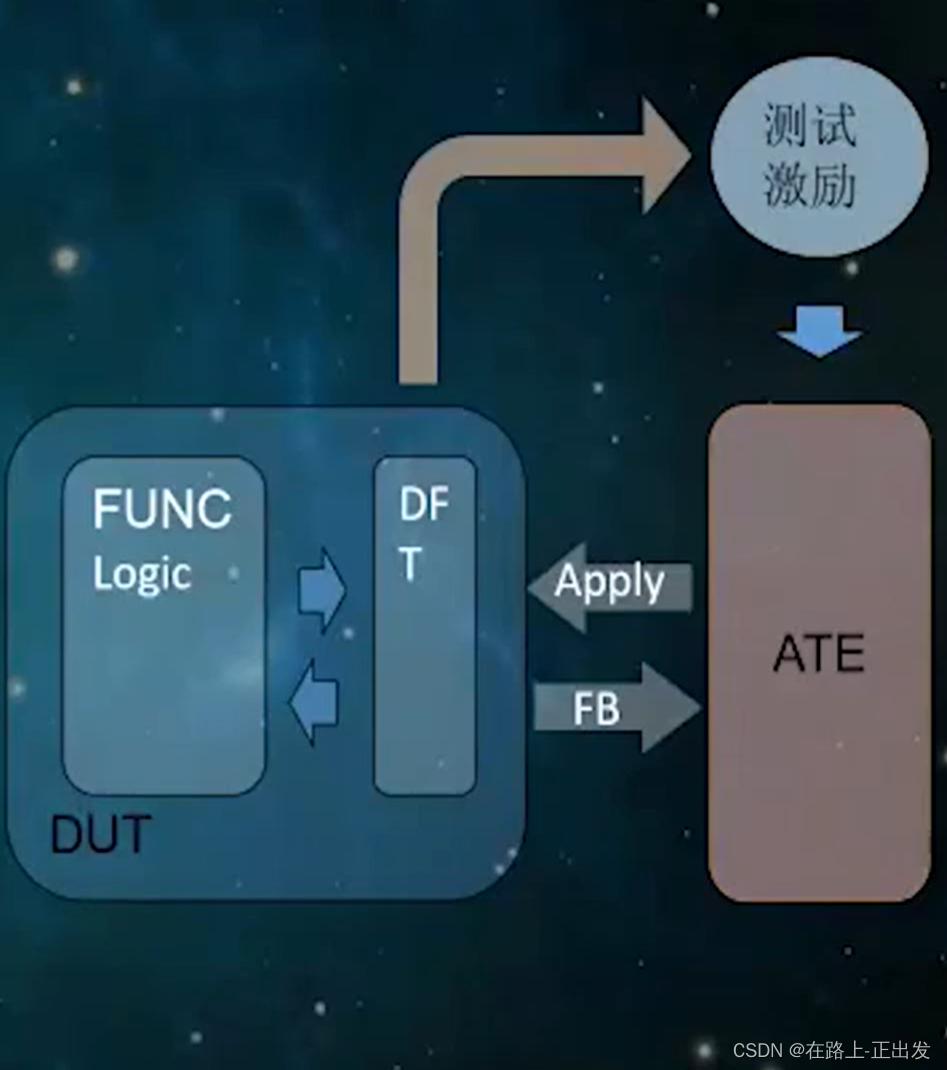

?ATE是自動測試機,將測試向量通過ATE激勵DUT,DUT的反饋給到ATE,ATE比對收到的響應和期望的響應是否一致,完成對DUT的測試。

DFT策略

可測試性電路示例

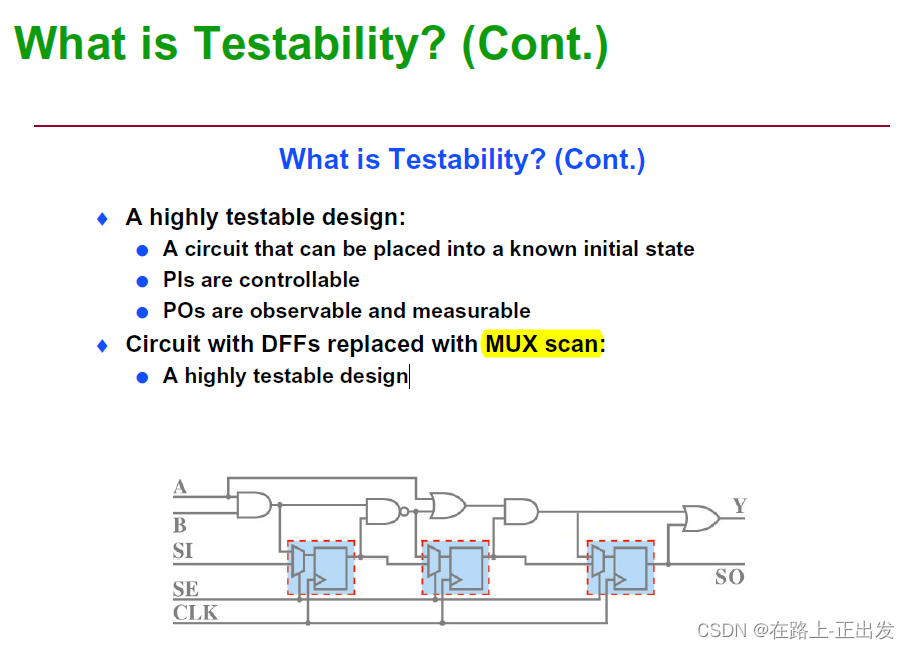

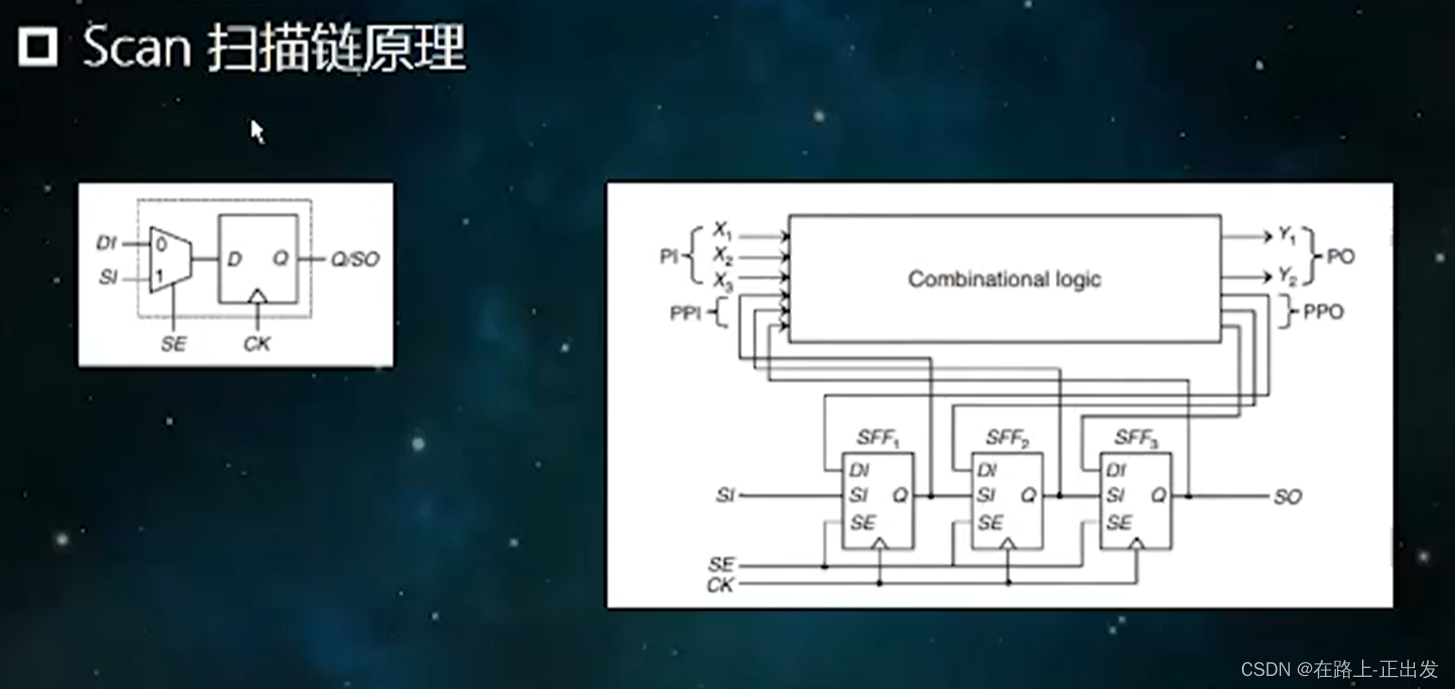

寄存器會被替換為帶有MUX的寄存器鏈,當SE為1時,各個寄存器首尾相接連接成一條寄存器鏈將測試輸出的數據串行輸出。?

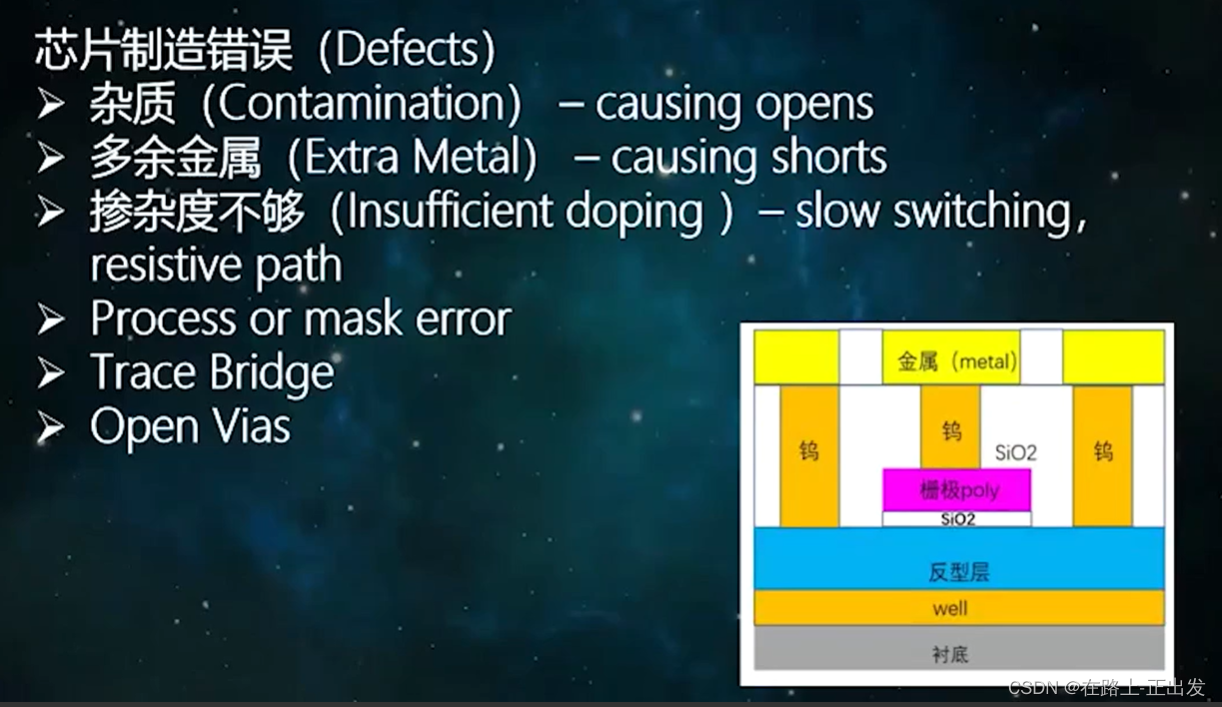

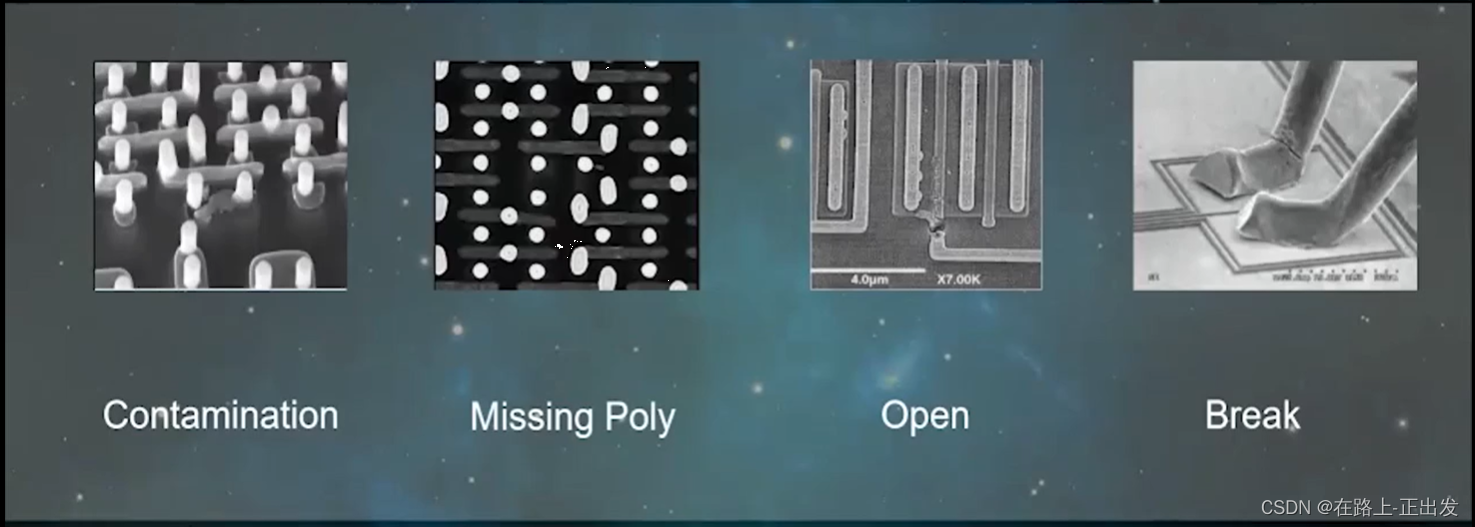

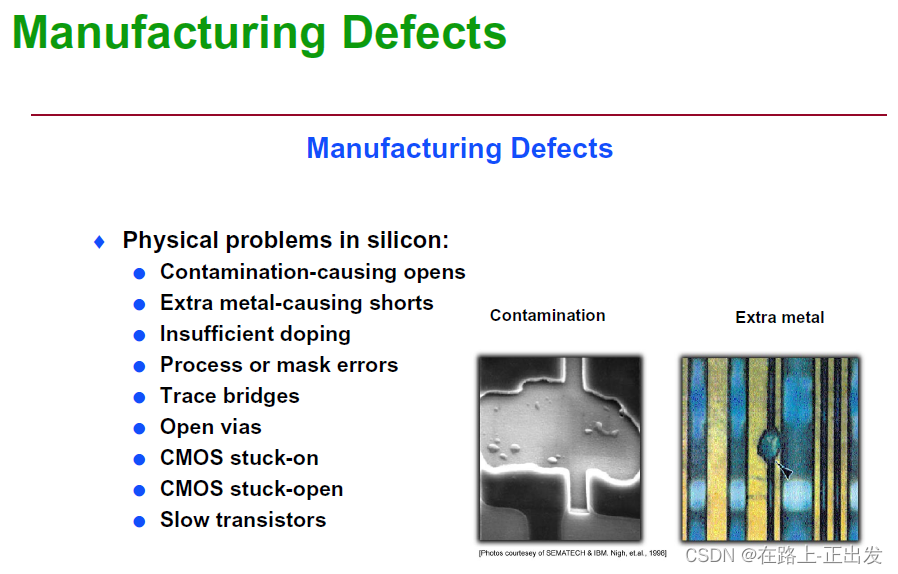

?芯片制造故障

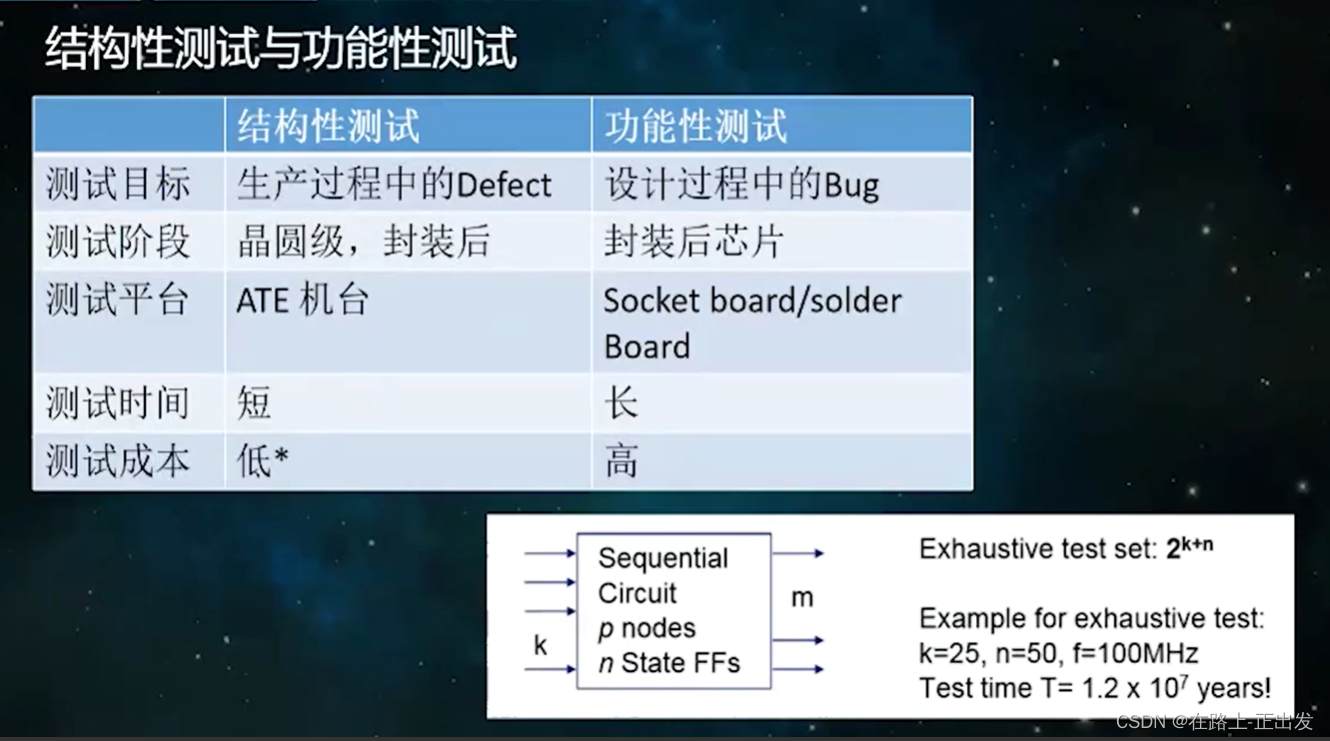

結構性測試與功能性測試

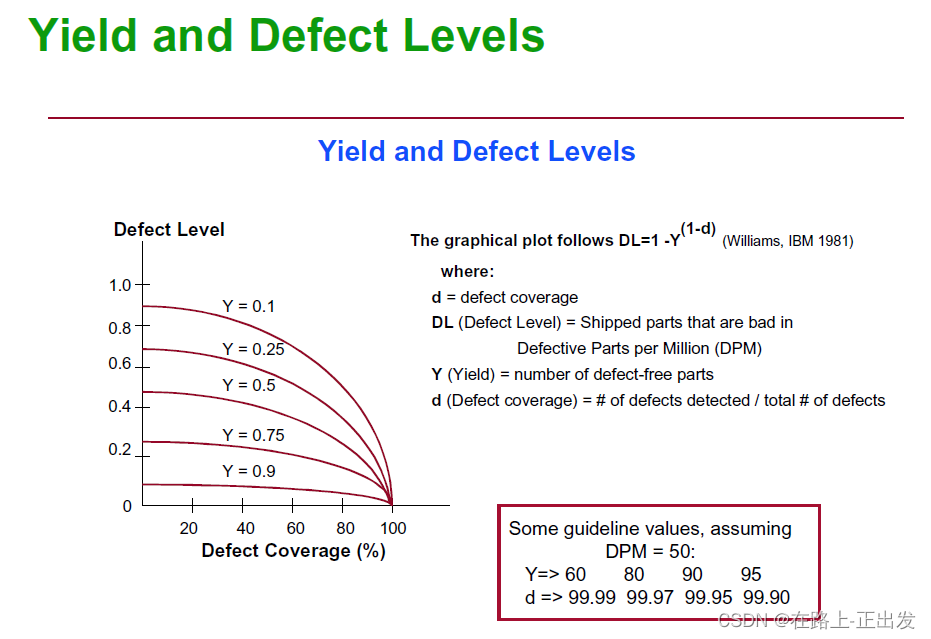

成品率和質量的關系

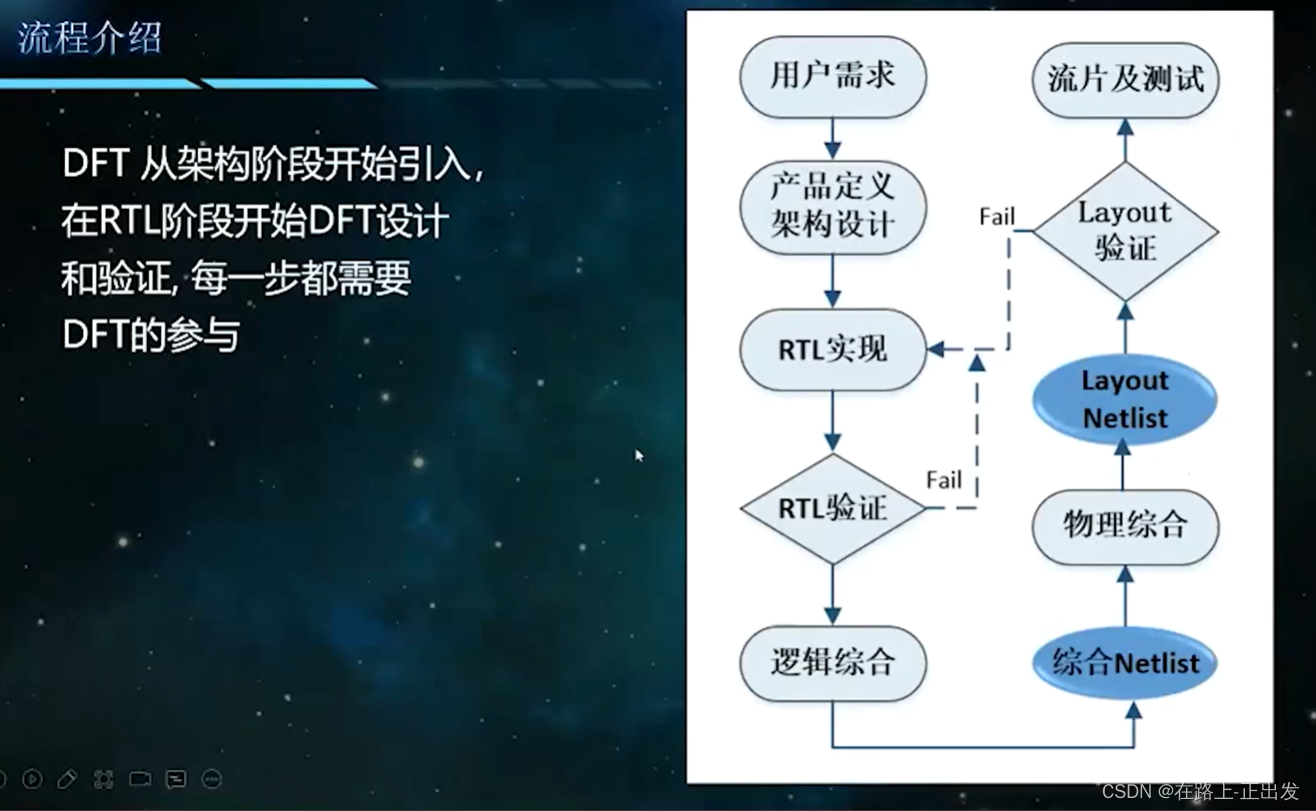

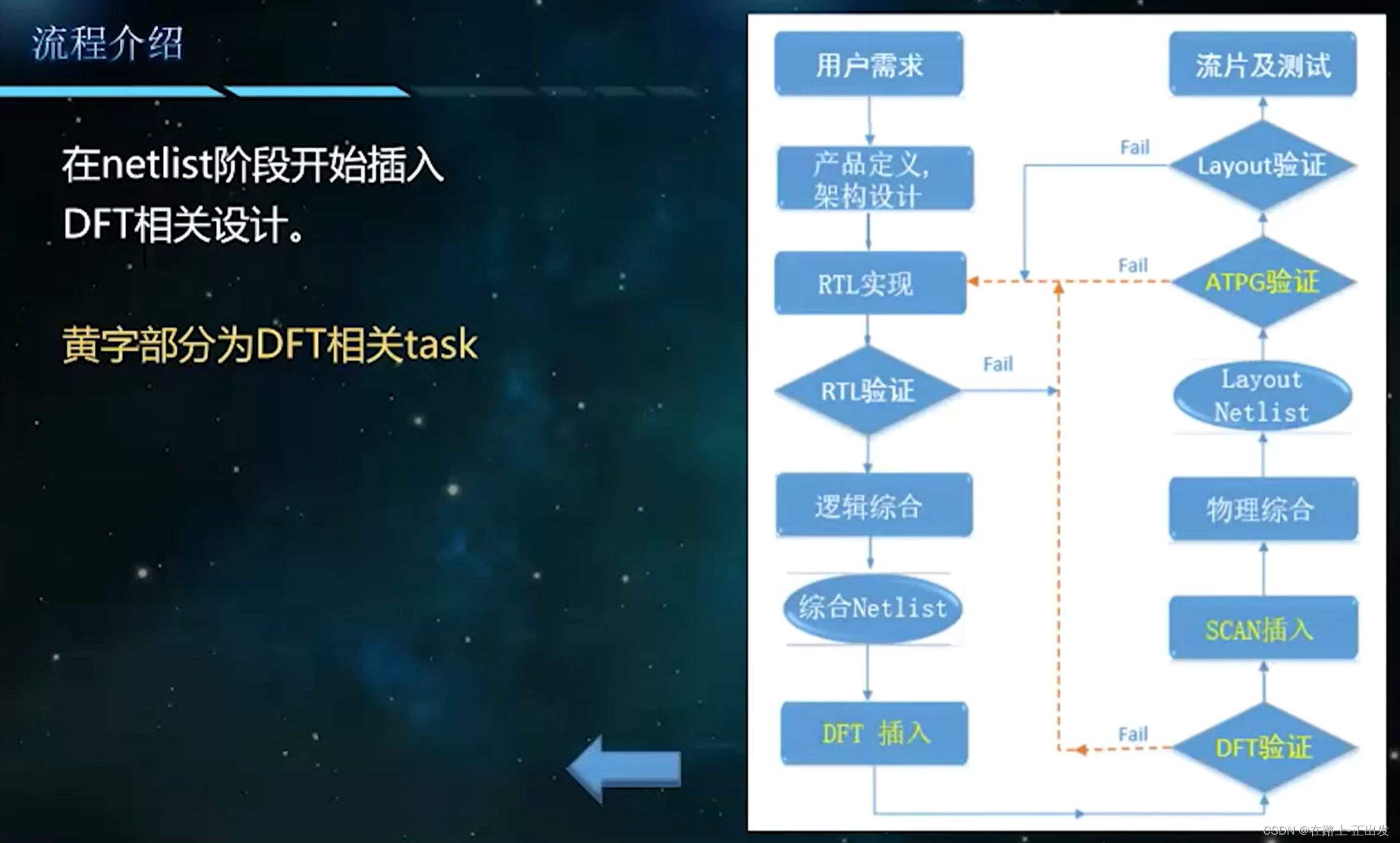

設計流程

DFT全程參與:

?DFT后期參與:

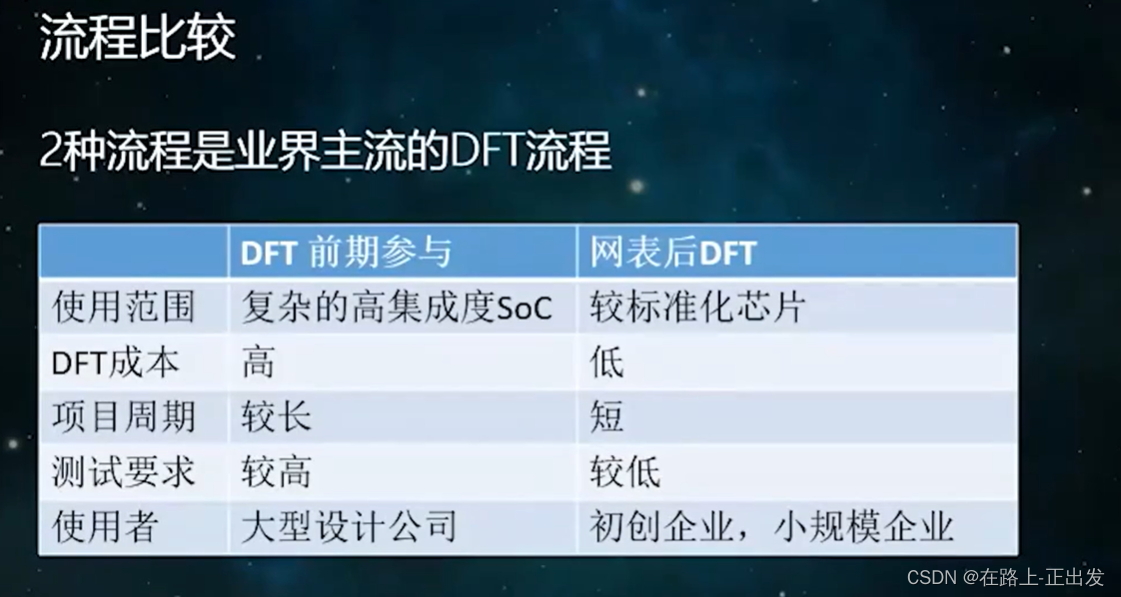

二者比較:?

測試方式

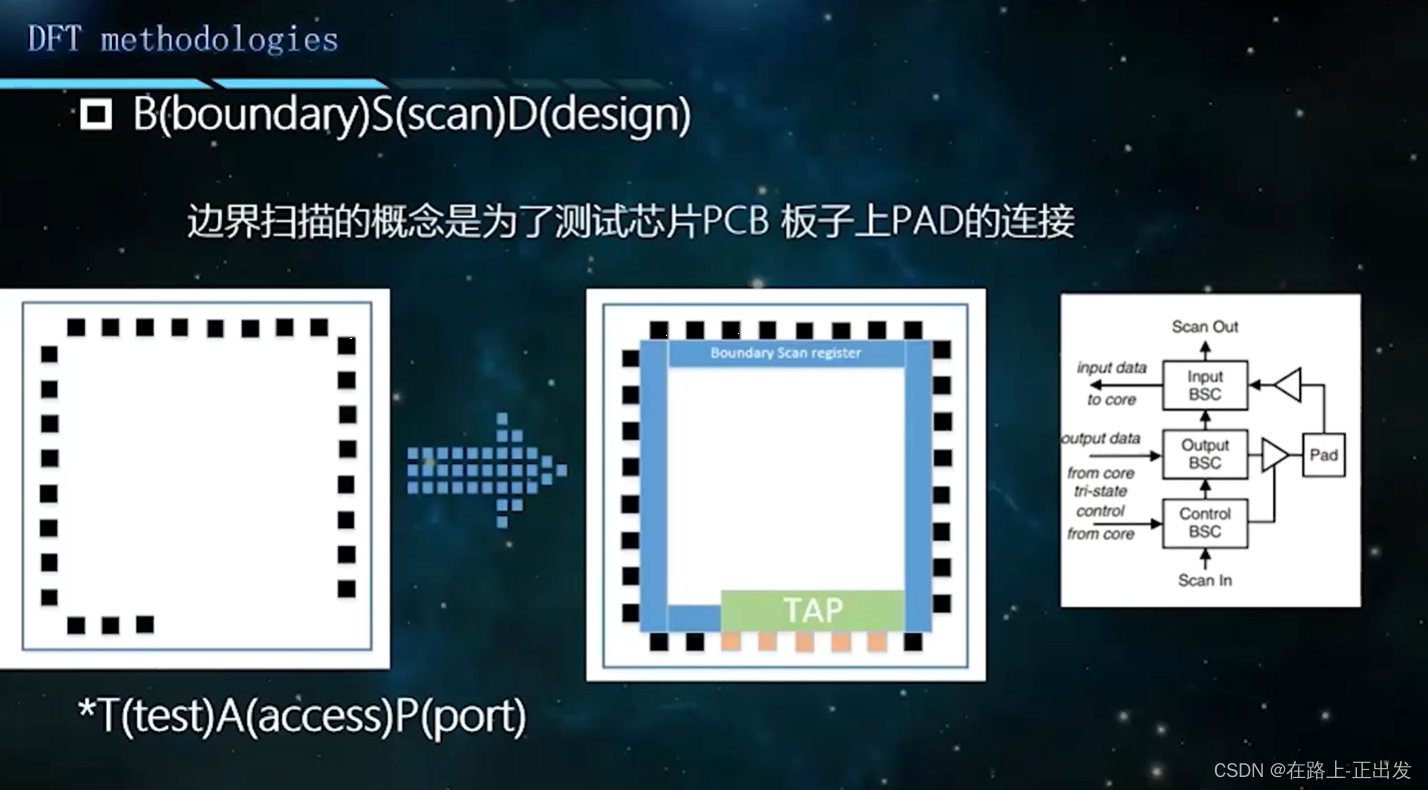

邊界掃描:

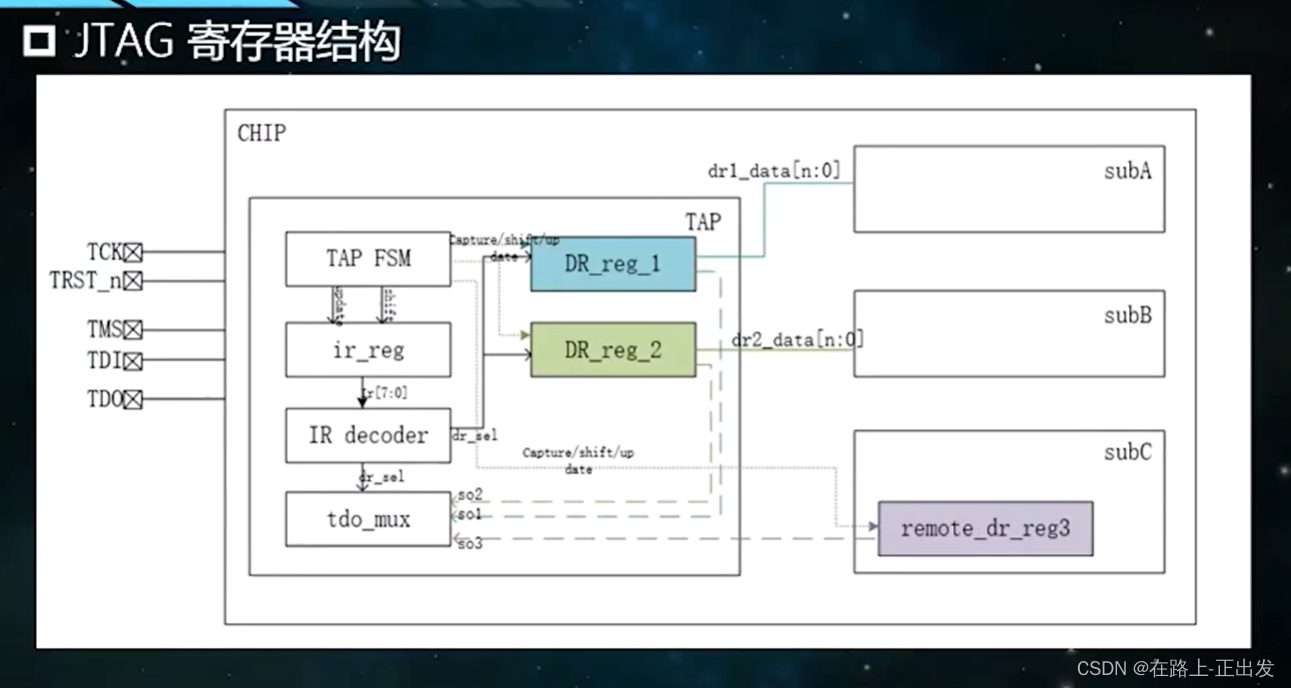

?JTAG寄存器結構

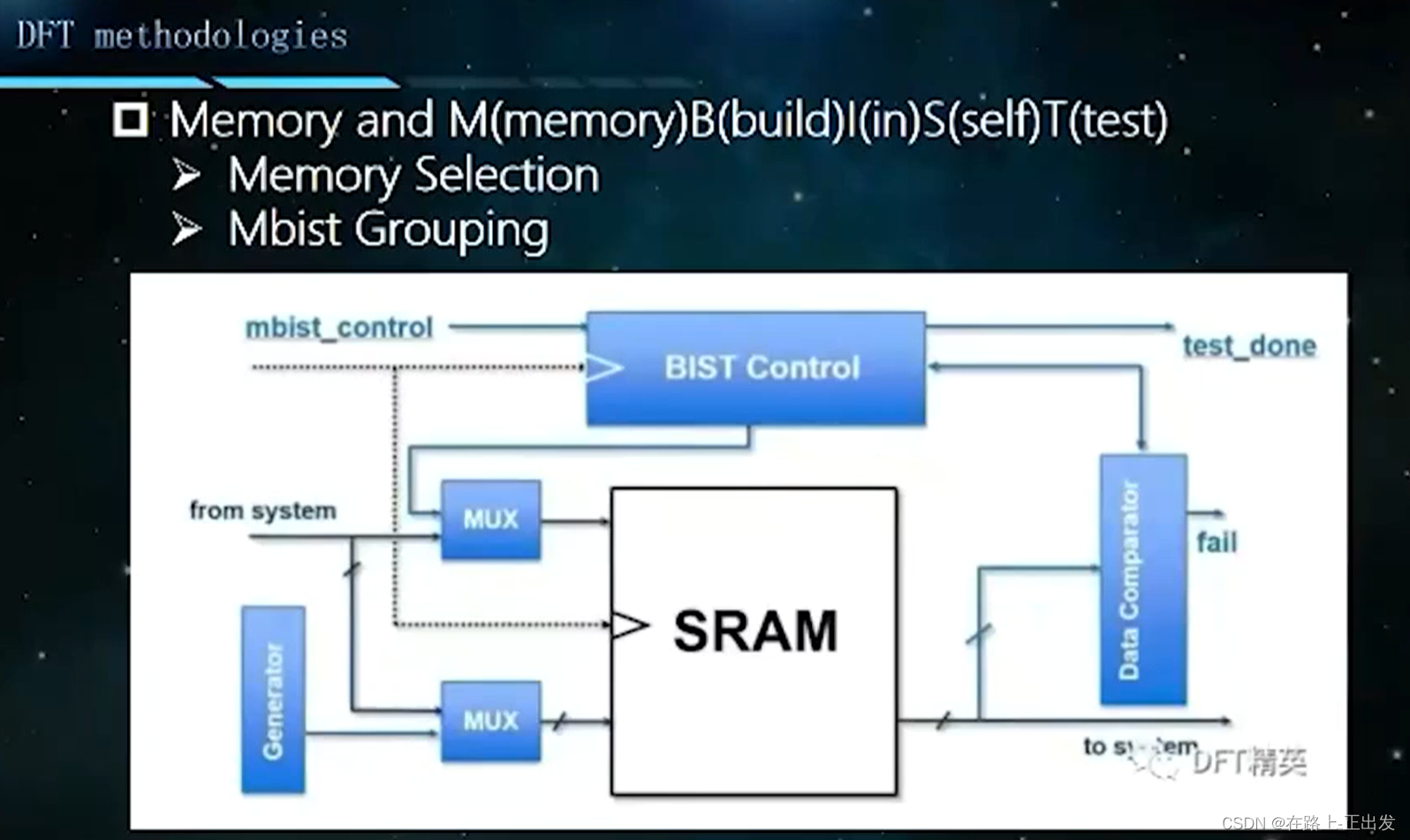

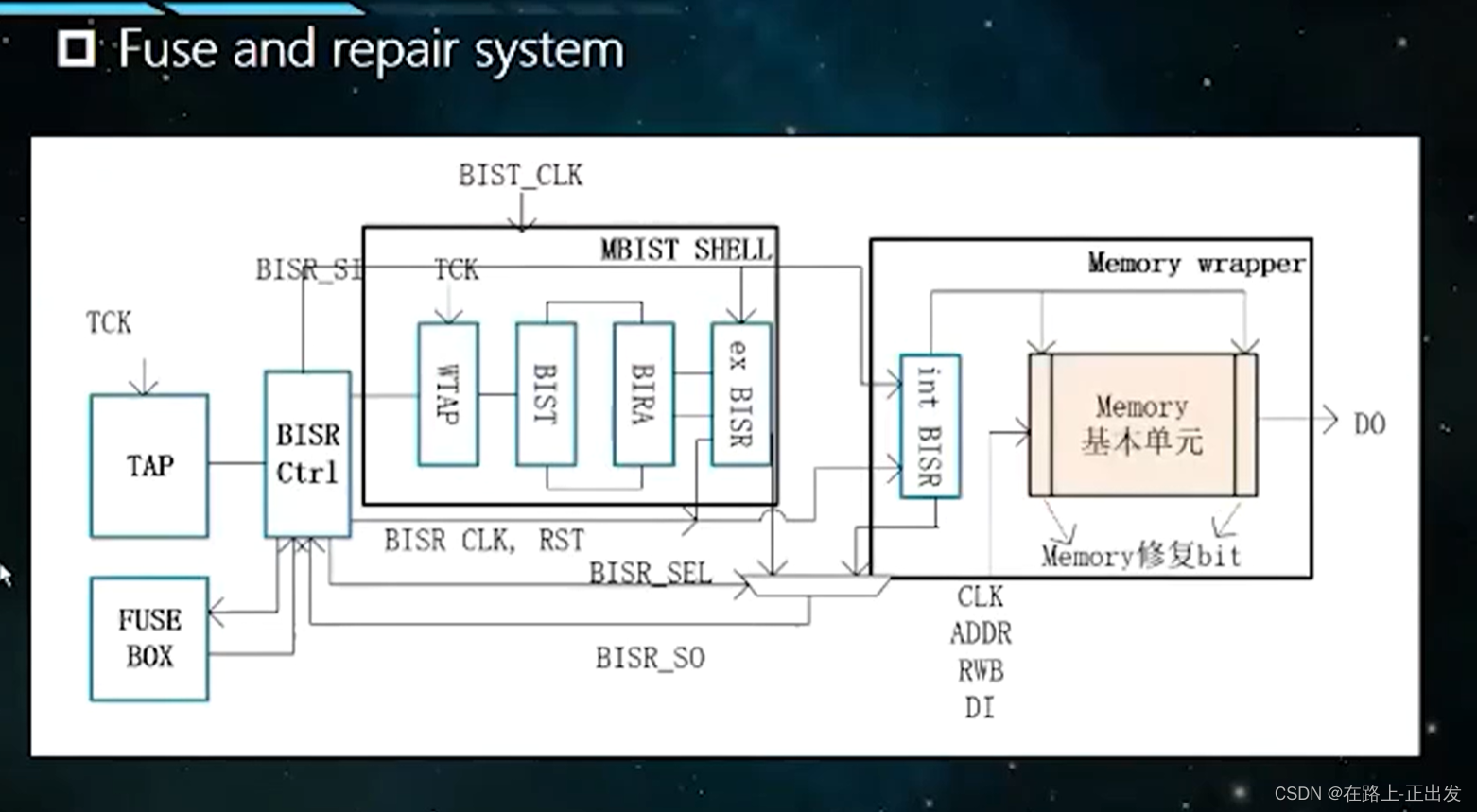

?MBIST測試結構:

?

掃描鏈

將普通的D觸發器替換為帶有MUX的D觸發器,實現掃描鏈的電路功能。

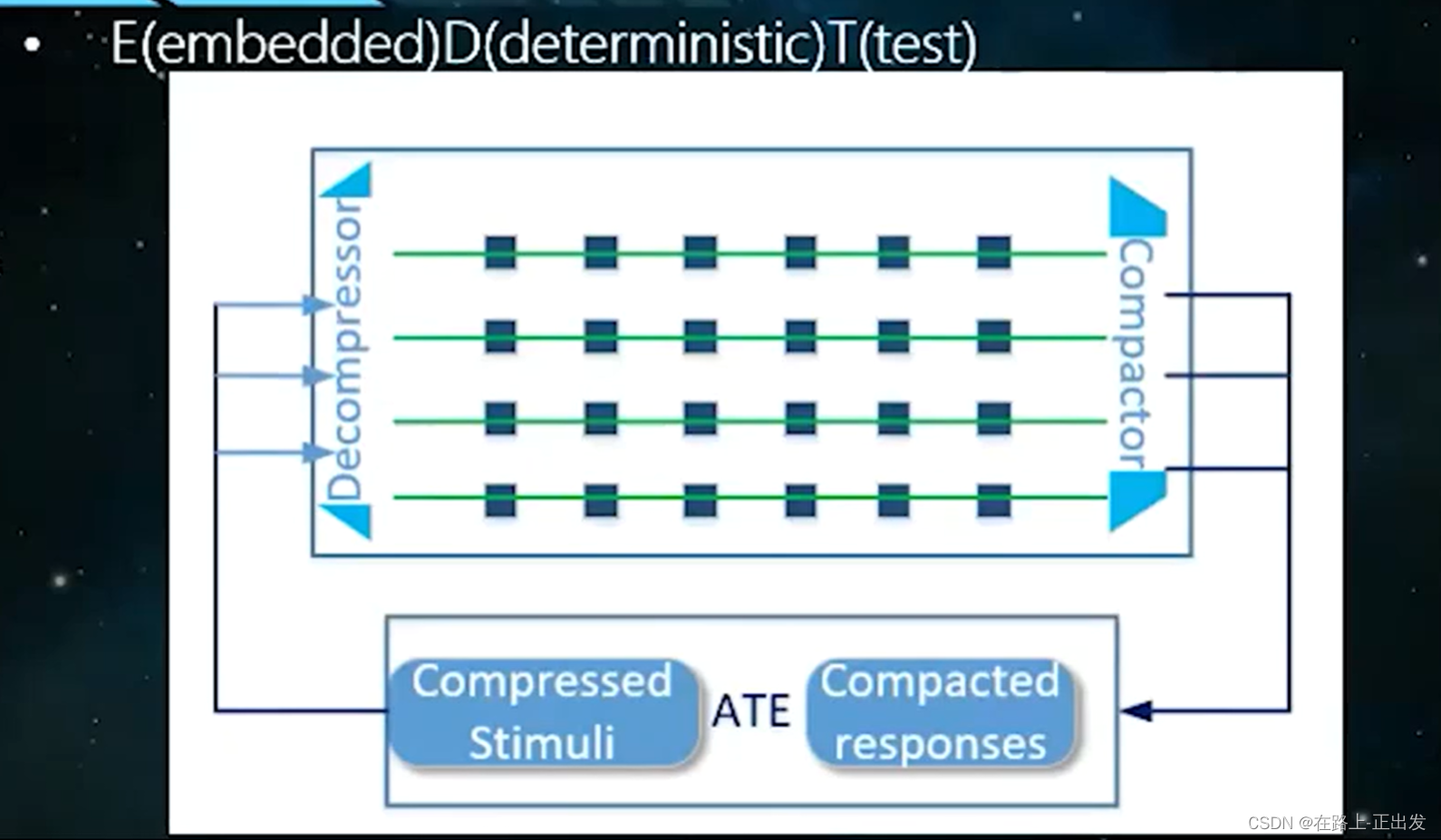

壓縮激勵/響應?

在大型的集成電路中,需要測試的功能有很多,但是可以供使用的IO很少,或者內部的掃描連很長,導致測試時間成本很大。

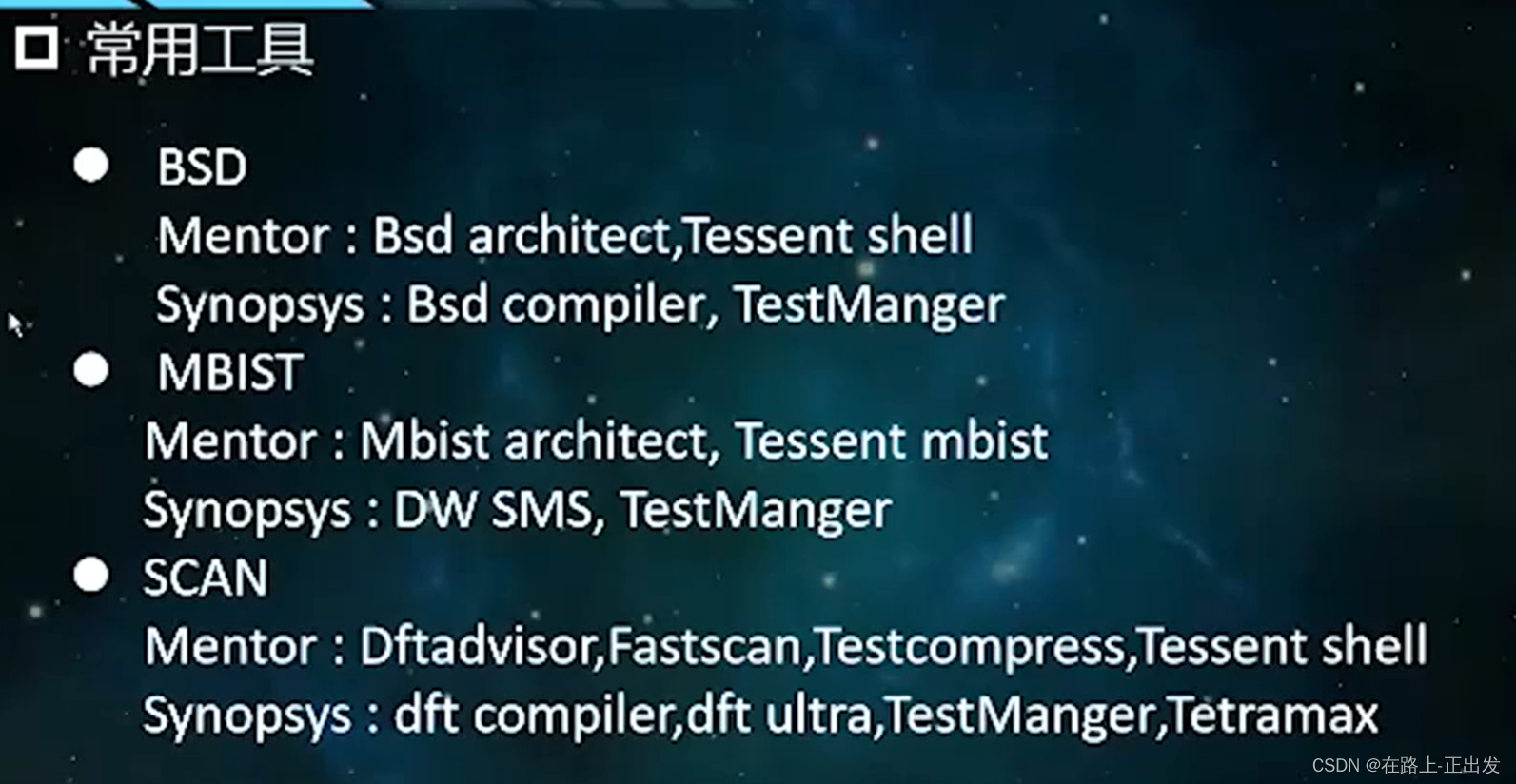

常用工具

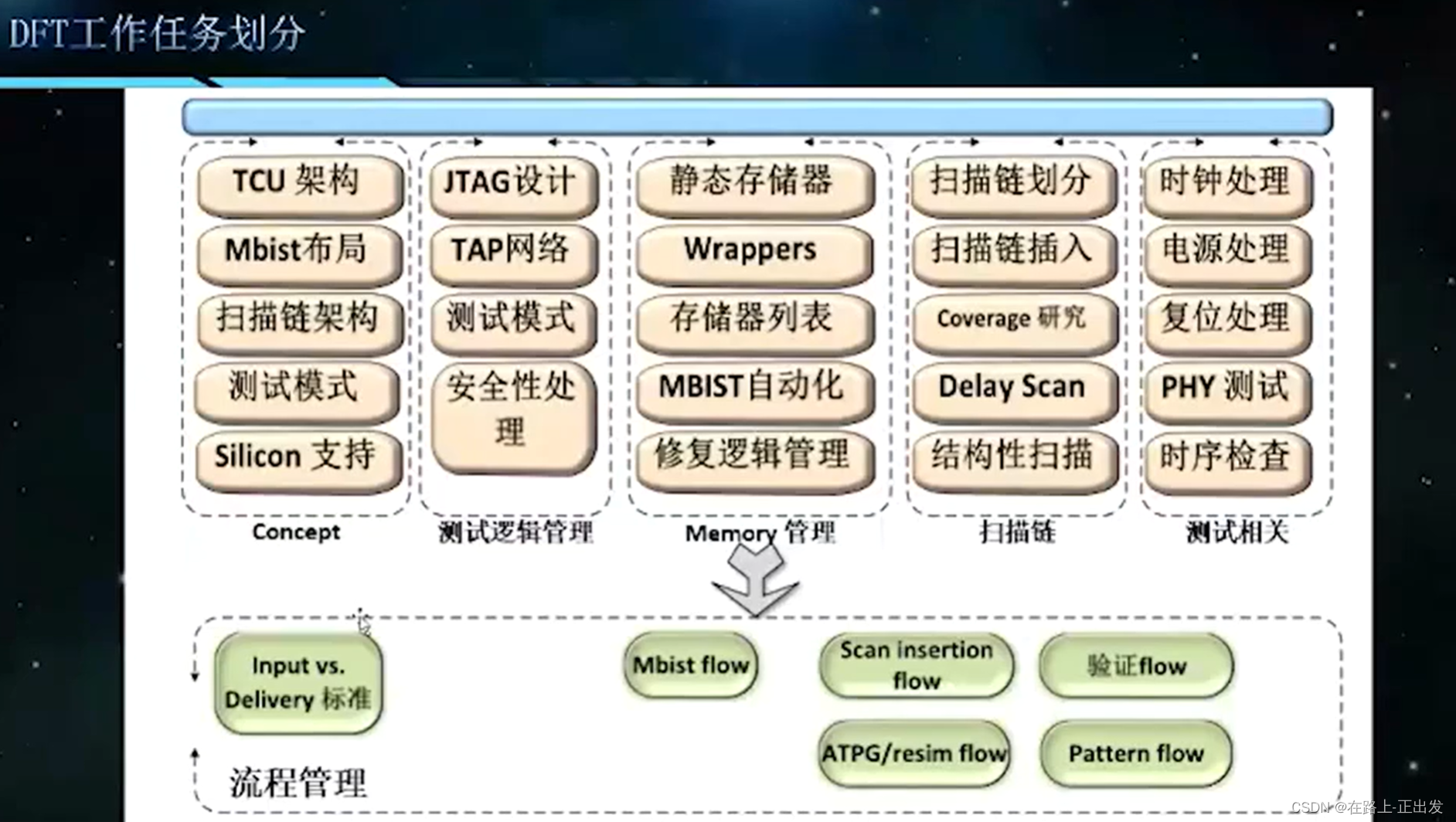

任務分配?

?

?

?

?

?

![Java并發編程(四)線程同步 中 [AQS/Lock]](http://pic.xiahunao.cn/Java并發編程(四)線程同步 中 [AQS/Lock])

)

)

函數詳解,PHP截取字符串。)

)