時鐘域就是同一個時鐘的區域,體現在laways語句邊緣觸發語句中,設計規模增大就會導致時鐘不同步,有時差,就要設計多時鐘域。

?會經過與門的延時產生的新時鐘域,這種其實不推薦使用,但在ascl里面很常見

在處理時鐘域的信號傳遞,一般會有故障具有隨機性,不同工藝出現問題的可能性不同,對于亞穩態的檢測很少,故障很難被發現,要設計中要注意。

?

?要經過組合延時,就會起沖突,間隔不夠

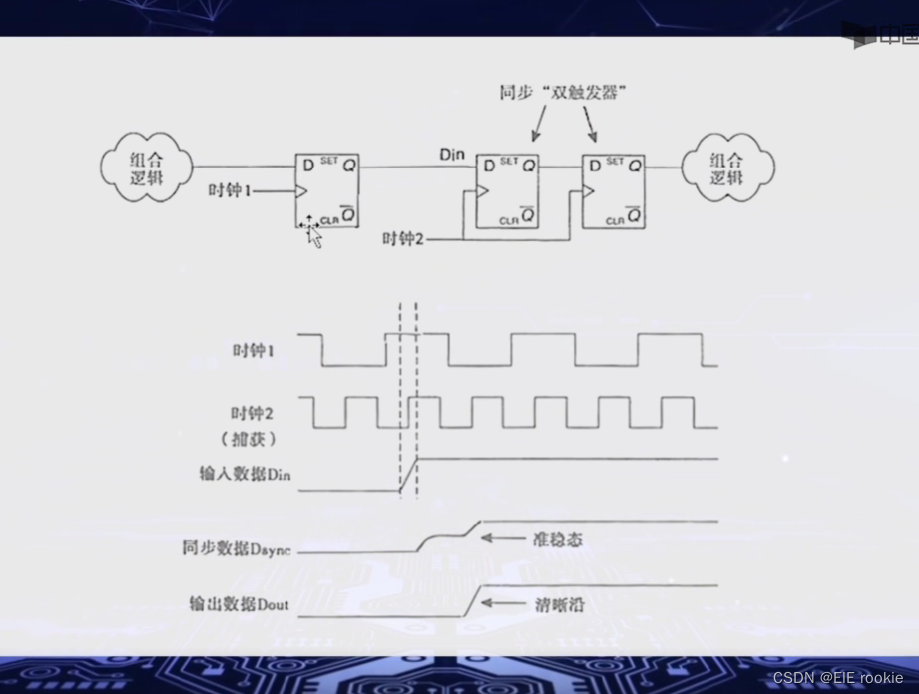

?數據要保證建立時間和保持時間才有效,RTL級無法分析亞穩態的,在門級都很難,提高設計本身的設計!,通過DLL或者PLL控制相位,來達到相位匹配,消除亞穩態。要保持時鐘具有整數倍關系

若兩個時鐘毫無關系,或者FPGA為兩個系統提供接口時候,很難使用相位控制

?

?用打兩拍的方法,解決單bit的亞穩態問題

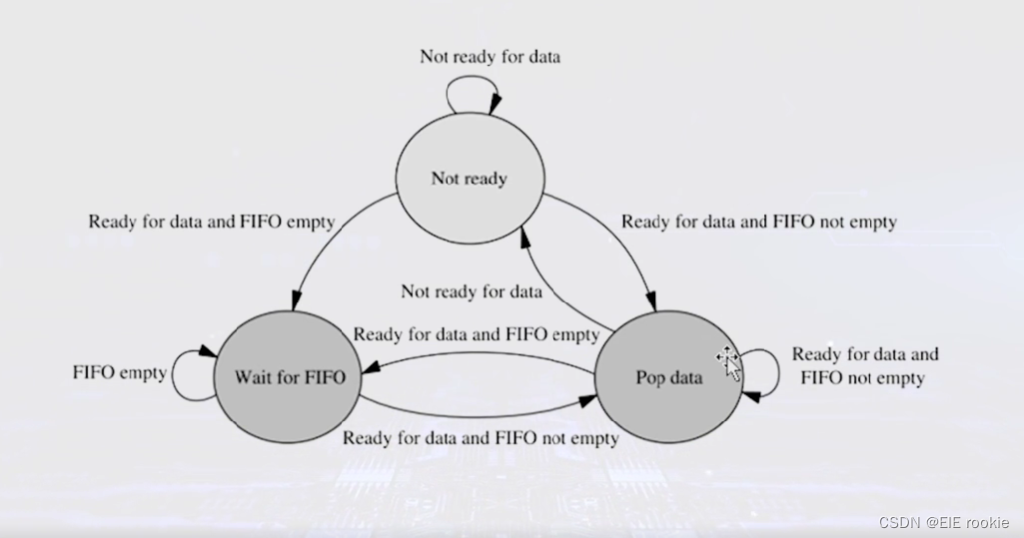

FIFO先入先出結構解決多bit數據

?

用fifo存儲數據,然后根據時鐘2調整推出數據,要注意防止溢出,要有效握手控制,滿標志通知發送端已經滿了,空標志通知接收端已經沒有數據可以抓取了,

?

讀狀態機的示意圖,寫狀態機類似。?

)

【系統架構設計師】)

)

)