一、簡述

靜態時序分析是檢查系統時序是否滿足要求的主要手段。以往時序的驗證依賴于仿真,采用仿真的方法,覆蓋率跟所施加的激勵有關,有些時序違例會被忽略。此外,仿真方法效率非常的低,會大大延長產品的開發周期。靜態時序分析工具很好地解決了這兩個問題。它不需要激勵向量,可以報出系統中所有的時序違例,并且速度很快。但并沒有進行系統功能上的驗證。

上圖我們可以看到靜態時序分析在整個芯片設計流程中的位置,可以發現STA幾乎涉及后端的全部階段,是sign off的重要工具。。通過靜態時序分析,可以檢查設計中的關鍵路徑分布;檢查電路中的路徑延時是否會導致setup違例;檢查電路中是否由于時鐘偏移過大導致hold違例;檢查時鐘樹的偏移和延時等情況。此外靜態時序分析工具還可以與信號完整性工具結合在一起分析串擾問題。常用的靜態時序工具是PrimeTime。其主要輸入輸出為:

相對于動態仿真,我們可以得出下表:

二、基本概念

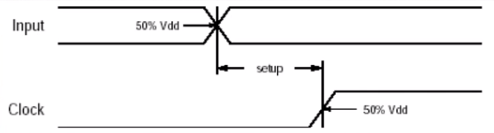

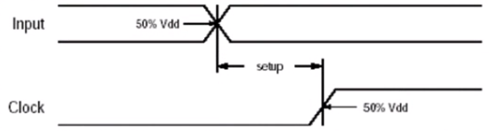

1.建立時間(setup time)

觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間不夠,數據將不能在這個時鐘上升沿被打入觸發器

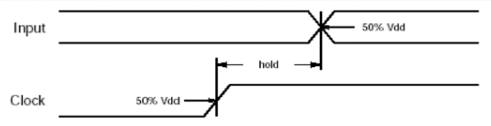

2.保持時間(hold time)

觸發器的時鐘信號上升沿到來以后,數據穩定不變的時間,如果保持時間不夠,數據將不能被打入觸發器。?

3.時間裕量(time slack)

傳輸中的信號的真實時間于需求時間之間的差值。通常用來表示設計是否滿足時序要求。

Setup slack = Data Required Time(setup)?- Data Arrival Time

Hold slack = Data Arrival Time - Data Required Time?(hold)

4.時鐘抖動(clock jitter)

指時鐘邊沿變化不確定的時間。

5.時鐘偏斜(clock skew)

時鐘和其它信號的傳輸一樣會有延時的。下圖中,時鐘信號從時鐘源傳輸到源寄存器的延時定義為Tc2s ,傳輸到目標寄存器的延時定義為 Tc2d。

時鐘偏斜是指時鐘源到達源寄存器和目的寄存器的時間偏移。其計算公式為:Tskew = Tc2d?–?Tc2s。

6.時序分析起點(launch edge)

第一級寄存器數據變化的時鐘邊沿,也是靜態時序分析的起點。

7.時序分析終點(latch edge)

數據鎖存的時鐘邊沿,也是靜態時序分析的終點。

8.數據輸出延時(Clock-to-Output Delay)

這個時間指的是當時鐘有效沿變化后,數據從輸入端到輸出端的最小時間間隔。

9.數據到達時間(data arrival time)

輸入數據在有效時鐘沿后到達所需要的時間。主要分為三部分:時鐘到達源寄存器時間(Tc2s),寄存器輸出的延時(Tco)和源寄存器到目的寄存器數據傳輸的延時(Tr2r),如下圖:

因此,Data Arrival Time = launch edge + Tc2s + Tco + Tr2r

10.數據需求時間(Data Required Time)

在時鐘鎖存的建立時間和保持時間之間數據必須穩定,從源時鐘起點達到這種穩定狀態需要的時間即為數據需求時間。如下圖:

因此,(建立)Data Required Time = latch edge + Tc2d?–?Tsu;

(保持)Data Required Time = latch edge + Tc2d + Th;

而習慣用Clock Arrival Time (時鐘到達時間)= latch edge + Tc2d

三、基本流程

STA主要分為以下三步:

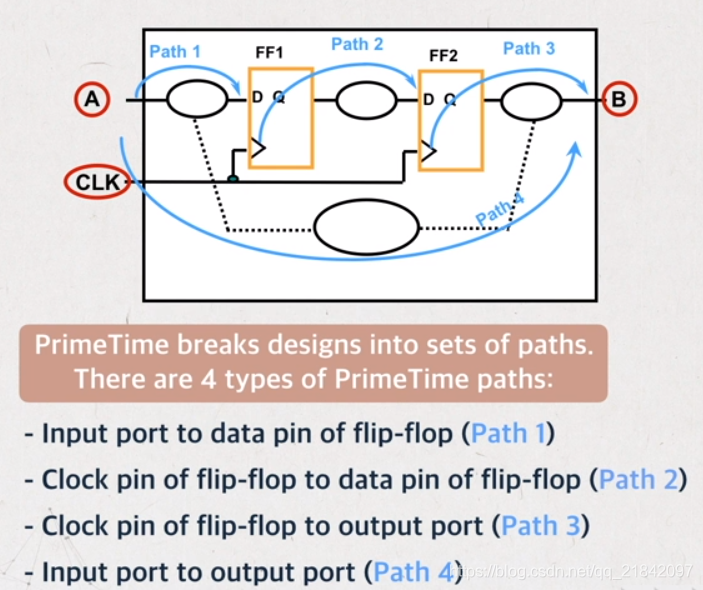

1、將整個電路設計分割成不同的時序路徑

2、計算每一條時序路徑的邏輯延時

3、檢查時序路徑是否滿足其時序約束

時序路徑可分為以下四種:

)

![[Luogu1821][USACO07FEB]銀牛派對Silver Cow Party](http://pic.xiahunao.cn/[Luogu1821][USACO07FEB]銀牛派對Silver Cow Party)

限定某個目錄禁止解析php、限制user_agent和PHP相關配置)

![[轉載]IIS7報500.23錯誤的解決方法](http://pic.xiahunao.cn/[轉載]IIS7報500.23錯誤的解決方法)