OCV(on-chip variation)是指在同一個芯片上, 由于制造工藝和環境等原因導致芯片上各部分特征不能完全一樣,從而造成偏差,對時序分析造成影響。這些偏差對互聯線和cell的延時都是有影響的。

由于OCV對延時有影響,那么我們在進行時序分析時需要將這些OCV效應考慮進來。在STA中,通過對不同的時序路徑添加derate系數,來完成對OCV的建模,將OCV效應納入分析。

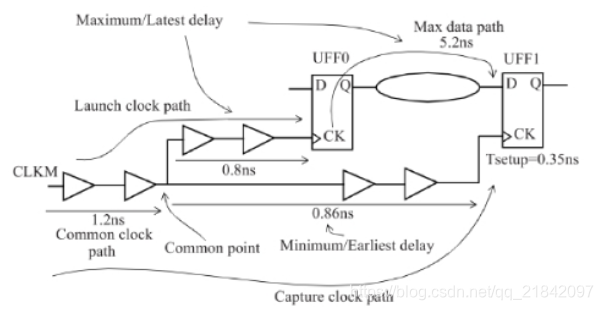

我們以下圖電路為例進行說明:

進行setup check時,最差的情況為:launch clock path 和data path由于OCV的原因,延遲增加到最大;于此同時,capture clock path 由于OCV的原因,延遲減小到最小。此時,對建立時間的檢查最為嚴苛。

如過我們不考慮OCV的影響,進行setup check,則情況如下:

arrival time = 1.2+0.8+5.2=7.2ns

required time = 1.2+0.86-0.35+clock_period=1.71+clock_period

那么由于required time-arrival time>=0則clock_period>=5.49,即最小時鐘周期為5.49ns。

接下來我們將OCV納入考慮,為路徑和cell設置不同的derate系數。

我們可以通過set_timing_derate來設置derate系數

set_timing_derate -early 0.9 set_timing_derate -late 0.9 set_timing_derate -cell_delay -late 0.9 set_timing_derate -net_delay -late 0.9長路徑延時如setup check 中的launch clock path和data path,hold check中的capture?clock path可以使用-late選項來設置

短路徑延時如setup check 中的capture clock path,hold check中的launch clock path和data path可以使用-early選項來設置

使用-net_delay和-cell_delay來設置線網和cell的延時

為launch clock path和max data path增加系數1.2,為UFF1增加系數1.1,為capture clock path 增加系數0.9,這樣,我們再看看setup check:

arrival time = (1.2+0.8+5.2)*1.2=8.64ns

required time = (1.2+0.86)*0.9-0.35*1.1+clock_period=1.469+clock_period

那么由于required time-arrival time>=0則clock_period>=7.171,即最小時鐘周期為7.171ns。可以看到,在加入最差情況的OCV后,電路能運行的時鐘頻率明顯下降了。

? ? ? ? 但是在上面的計算中,我們還是可以發現一個問題,即common clock path即屬于launch clock path,也屬于capture clock path,所以在計算中,我們對其使用了不同的derate系數進行計算:在計算arrival time中,系數為1.2;在計算required time中,系數為0.9,這樣會讓我們的分析更為悲觀,電路性能更差。而在真實的情況中,common?clock path的PVT只有一個,不可能同時有兩個derate系數,所以我們會進行CPPR操作。

CPPR(Clock Path Pessimism Removal)或者CRPR(Clock Reconvergence Pessimism Removal),中文名“共同路徑悲觀去除”。它的作用是去除clock path上的相同路徑上的悲觀計算量,即我們上面提到的問題。我們將common point定義為時鐘樹上共同部分最后一個cell的output pin。則定義CPP因子為:

CPP=LatestArrivalTime@CommonPoint-EarliestArrivalTime@CommonPoint

我們進行CPPR后再來進行一次計算:

LatestArrivalTime@CommonPoint=1.2*1.2=1.44ns

EarliestArrivalTime@CommonPoint=1.2*0.9=1.08ns

CPP=1.44-1.08=0.36ns

則clock_period=7.171-0.36=6.811ns

可以看到,電路的運行時鐘頻率變好了一點,但對于未考慮OCV來說,整個運行時鐘頻率還是降低了。

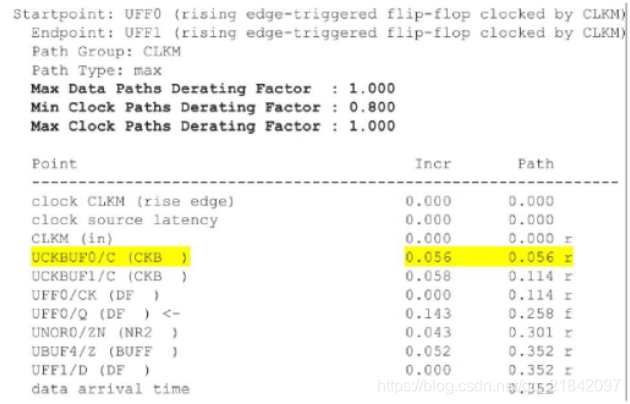

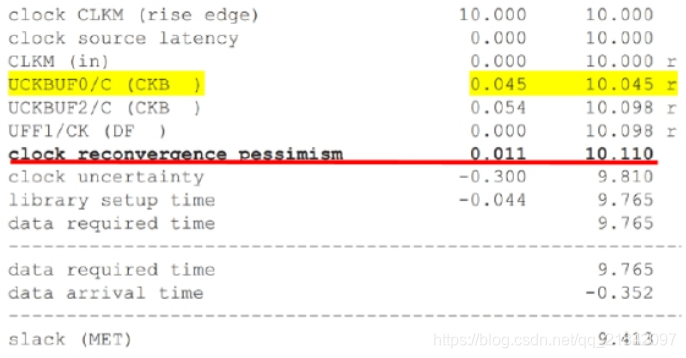

我們可以來看看時序報告

? ? ??

?

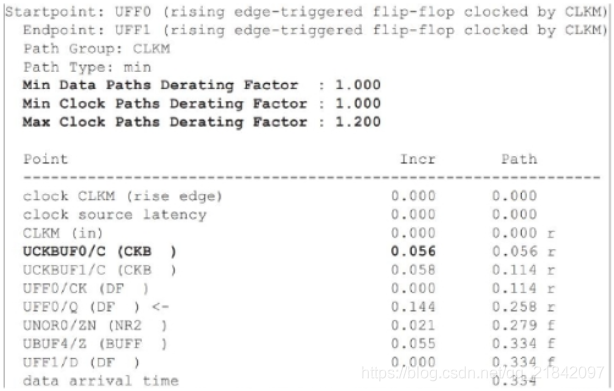

說完setup check,我們來看看OCV對hold check的影響。

進行hold check時,最差的情況為:launch clock path 和data path由于OCV的原因,延遲減小到最小;于此同時,capture clock path 由于OCV的原因,延遲增加到最大。此時,對保持時間的檢查最為嚴苛。我們進行同樣的分析,可以看到基本相同的結果。

其時序報告如下:

???

![[轉載]IIS7報500.23錯誤的解決方法](http://pic.xiahunao.cn/[轉載]IIS7報500.23錯誤的解決方法)

)

)

Hibernate高級配置)