一、多周期 multicycle paths

在一些情況下,如下圖所示,兩個寄存器之間的組合電路傳輸的邏輯延時超過一個時鐘周期。在這樣的情況下,這個組合路徑被定義為多周期路徑(multicycle path)。盡管后一個寄存器會在每一個的時鐘的上升沿嘗試捕獲(capture)數據,但我們會在STA中指定個時鐘周期后的上升沿(relevant capture edge)去捕獲數據。

以上圖為例,組合路徑的延時為三個周期,那么三個時鐘周期的多周期setup check可以用以下語句進行約束

cerate_clock -name CLKM -period 10 [get_ports CLKM] // 設置時鐘源

set_multicycle_path 3 -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D] //multicycle這樣,我們就達成了下面的圖的效果,在第三個時鐘沿進行建立時間的檢查。

由于工具一般會在建立時間檢查時鐘沿(capture edge)的前一個時鐘沿進行保持時間檢查,而在多周期的情況下,這樣進行保持時間檢查較為嚴苛,以上圖為例,在2nd時鐘沿進行保持時間檢查,那么,數據需要保持到2nd時鐘之后才能變化。所以,在多時鐘周期的情況下,我們如果在N個周期后進行簡歷時間檢查,那么我們會將簡歷時間檢查提前N-1個時鐘周期。

同樣以上面的的電路為例,多周期hold check可以用以下語句進行約束:

cerate_clock -name CLKM -period 10 [get_ports CLKM] // 設置時鐘源

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D] //multicycle

?

二、半周期 half-cycle paths

如果一個電路設計中同時存在正時鐘沿觸發和負時鐘沿觸發的觸發器,那么在這種電路中需要進行半周期的檢查。

我們以下面的電路為例:

對其進行建立時間檢查,那么其檢查的時鐘沿如下圖:

其時序報告如下:

? ?

與一般的時序報告不同的是,需要注意startpoint和endpoint,其注明的觸發沿是不同的。

由于時序路徑中僅有半個時鐘周期用來進行建立時間檢查,那么我們有額外的半個時鐘周期來進行保持時間檢查,如下圖:

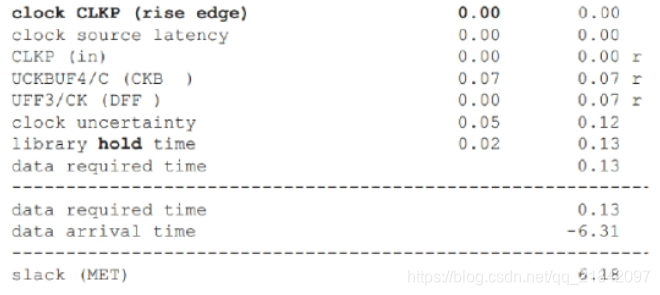

其保持時間檢查時序報告如下:

? ?

三、偽路徑 false paths

某些情況下,一些時序路徑可能在電路設計的真實功能中并不存在,我們會在STA中將將這些路徑設置為偽路徑,這樣,工具(prime time)會忽略這些路徑,不對其進行時序分析。

一般需要進行偽路徑的處理情況有:

1.? 從邏輯上考慮,與電路正常工作不相關的那些路徑,比如測試邏輯,靜態或準靜態邏輯。

2.? 從時序上考慮,我們在綜合時不需要分析的那些路徑,比如跨越異步時鐘域的路徑。

設置偽路徑可以減少工具的分析工作,讓工具更專注于分析真實的時序路徑,而且能減少分析時間。但是,設置過多的偽路徑會降低分析的效率,反而使分析速度減慢。

我們有以下幾種方法來設置偽路徑約束:

set_flase_path -from [get_clocks SCAN_CLK] -to [get_clocks CORE_CLK]

//任何從SCAN_CLK時鐘域到CORE_CLK時鐘域的時序路徑都是偽路徑set_false_path -through [get_pins UMUX0/S]

//所有通過這個pin的時序路徑都是偽路徑建議減少使用-through,因為through命令會增加分析復雜度。

![[轉載]IIS7報500.23錯誤的解決方法](http://pic.xiahunao.cn/[轉載]IIS7報500.23錯誤的解決方法)

)

)