Design Compiler時一個約束驅動(constraint-driven)的綜合工具,它的結果與設計者施加的約束條件密切相關。

一、面積約束

? 進行面積的約束,也就是告訴DC綜合的電路面積要在多少以內。在介紹約束命令之前,先了解一下面積的單位。面積的單位可以是:

- 2輸入與非門(2-input-NAND-gate)

- 晶體管數目(Transistors)

- 平方微米(Square microns)

? 此外,我們往往看到一個芯片是多少多少門,這多少門的數字就是拿芯片的總面積,除以2輸入與非門的面積得到的數值。用report_lib命令不可顯示面積的單位,我們要詢問半導體廠商面積的單位是什么。或者用以下方法得到:

? 如果不設置面積的約束,Design Compiler將做最小限度的面積優化。設置了面積的約束后,DC將在達到面積約束目標時退出的面積優化。如果設置面積的約束為“0" , DC將為面積做優化直到再繼續優化也不能有大的效果。這時,DC將中止優化。注意,對于很大(如百萬門電路)的設計,如將面積的約束設置為“0" , DC可能要花很長的時間為設計做面積優化。綜合時,運行的時間很長。

? 在超深亞微米(deep sub-micro)工藝中,一般說來,面積并不是設計的主要目標,對設計的成本影響不大。因此,我們在初次優化時,可以不設置面積的約束。優化后,檢查得到的設計面積,然后將其乘上一個百分數(例如8500),將其結果作為設計的面積約束。再為設計做增量編輯,運行“compile -inc”命令,為面積做較快的優化。這樣做,既可以優化面積,又可以縮短運行時間。

最后我們用set_max_area命令為設計作面積的約束。例如:

set_max_area ?10000

當設計不是很大的時候,根據上面的描述,我們就可以使用下面的命令進行面積約束:

set_max_area ?0

讓DC做最大的面積優化約束。

二、時序約束

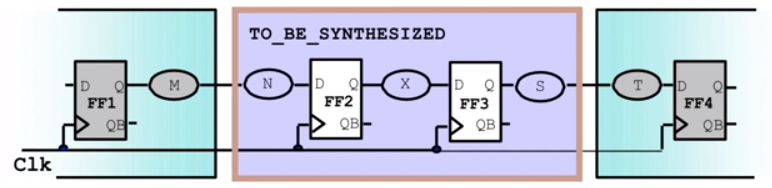

關于時序約束,我們要做的是約束電路中的所有時序路徑。這些時序路徑可以分為四類(具體可見靜態時序分析系列):輸入到寄存器的路徑、寄存器到寄存器之間的路徑、寄存器到輸出的路徑、輸入直接到輸出的路徑。

我們以常見的同步電路為例:

在電路綜合過程中,所有時序電路以及組合電路的優化都是以時鐘為基準來計算路徑延遲的,因此,要在綜合時候指定時鐘,作為估計路徑延遲的基準。

1、定義時鐘

- 用戶必須定義的值:colck source(pin or port)

- 用戶可能需要定義的值:duty cycle、offset/skew、clock name

create_clock -period 10 [get_ports Clk]

set_dont_touch_network [get_clocks Clk]

對所有定義的時鐘網絡設置為dont_touch,即綜合時候不對Clk信號進行優化。這是為什么呢?

實際的電路設計中,時鐘樹的綜合(CTS)有自己的方法,它需要考慮到實際布線后的物理信息,所以DC不需要在這里對時鐘樹進行處理。

我們使用create_clock后,情況如下:

這里我們需要定義IO相對于時鐘的一些時序。

2、定義輸入延遲

我們要定義的輸入延遲是指被綜合模塊外的寄存器觸發的信號在到達被綜合模塊之前的延時。即下圖中的Tclk-q和M電路的延時之和。

當Tclk-q和TM(Path M的延時)確定之后,由于時鐘也是確定的,則TN(Path N的延時)也將會確定。

我們用set_input_delay命令定義輸入延遲。

set_input_delay -max 4 -clock Clk [get_ports A]

由于輸入延遲是相對于時鐘的,所以需要注明時鐘域。

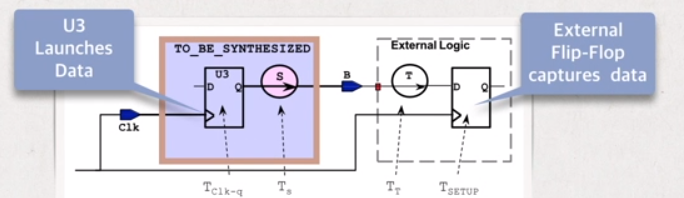

3、定義輸出延遲

信號在被綜合模塊的觸發器里被觸發,被外圍的一個觸發器接收,對外圍電路而言,它有一個T電路延時和外圍觸發器的建立時間要求。

由于時鐘是確定的,當T電路延時和外圍觸發器的建立時間要求確定之后,被綜合模塊內部的輸出路徑延時范圍也確定了下來。

我們用set_output_delay命令定義輸出延遲。

set_output_delay -max 4 -clock Clk [get_ports B]

三、DRC約束

常見的DRC約束有三種

- set_max_transition?約束設計中的信號、端口、net的transition time。net的transition time取決于net的負載(fan-out),負載越大,transition time越大。

- set_max_fanout 對design、net、output port進行操作,設定的不是具體的電容值。扇出負載值用來表示與單元輸入引腳相對的負載的數目,并不表示真正的電容負載,而是個無量綱的數字。

- set_max_capacitance 基于工藝庫的信息設定

四、環境約束

之前的約束對待綜合電路進行了許多條件限制,但還有許多方面未提及,如環境溫度、供電電壓、外圍負載等,我們在這一節進行說明。

1、設置負載

為了更加準確地估計模塊輸出的時序,除了知道輸出延時外,還需要知道輸出負載情況,負載越大,output port的transition time越大,影響時序。

由于DC默認輸出負載為0,即相當于不接負載,則這樣綜合的電路時序過于樂觀,不能反映真實工作情況。

常用指令如下

set_load 5 [get_ports OUT]? //直接設置

set_load [load_of my_lib/and2a0/A]?[get_ports OUT] //使用工藝庫中現有的單元的load值來進行代替

set_load expr[[load_of my_lib/and2a0/A*3]]?[get_ports OUT]

2、設置驅動

除了知道輸出延時、輸出負載情況外,DC還需要知道input port 的transition time。同樣地,默認情況下,DC默認外部信號transition time為0。

set_driving_cell允許用戶自行定義一個實際的外部驅動cell,同樣地,可以用工藝庫現有的單元的值來代替。

set_driving_cell -lib_cell and2a0 \[get_ports IN]

set_driving_cell??-lib_cell ?FD1 ?-pin ?Q ?[get_potrs ?IN]

set_drive以電阻值為計量,0表示最大驅動強度,通常為時鐘端口.

3、設置工作條件

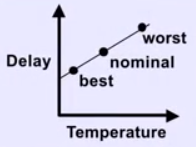

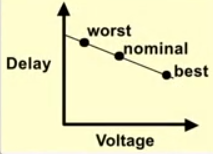

Foundry提供的工藝庫里,各個單元的延時實在一個標準的條件下得到的。在考慮延時時,還需要考慮工藝制程、電壓、溫度(PVT)的影響。

上圖可以看到PVT對延時的影響。因此,工藝庫中提供了幾種工作條件的模型(operating condition model)供設計者選擇,我們可以用:report_lib ?libname命令把廠商提供的所有工作條件列出來。一般綜合只考慮最好和最差兩種情況:最差情況用于建立時間的時序分析,最好情況用于保持時間的時序分析。

set_operating_conditions??-max $OPERA_CONDITION ?-max_library ?$LIB_NAME

4、設置連線延時

在計算時序路徑延遲時,除了需要知道門單元延遲外,還需要知道連線的延遲。

連線的延遲目前一般用(連)線負載模型( Wire ?Load ?Model,簡稱WLM)估算。WLM是廠商根據多種已經生產出來芯片的統計結果,在同樣的工藝下,計算出在某個設計規模范圍內(例如門數為0~43478.00、門數為43478.00~86956.00,等等)負載扇出為1的連線的平均長度,負載扇出為2的連線的平均長度,負載扇出為3的連線的平均長度等等。

WLM是根據連線的扇出進行估算連線的RC寄生參數,一般情況下,由半導體廠商建立。廠商根據已生產出來的其他設計統計出該工藝的連線寄生參數。半導體廠商提供的工藝庫中包括了線負載模型。通常在一個綜合庫里面有多種線負載模型,不同的模型模擬不同規模的的模塊內的線上負載情況。用戶也可以自己創建自己的線負載模型去更精確地模擬設計內的線上負載。

連線延時模型如下圖:

如果要查看工藝庫中的WLM,可以使用命令:report_lib ?$lib_name,進行綜合時,綜合工具會默認根據設計面積和節點處的負載自動選擇合適的連線負載模型,如果要關掉自動選擇WLM,那么可以使用命令:

set ?auto_wire_load_selection ?false

然后手動選擇線負載模型的命令是:

set_wire_load_model??-name ?$WIRE_LOAD_MODEL ?-library ?$LIB_NAME

如果連線穿越層次邊界,連接兩個不同的模塊,那么有三種方式對這種跨模塊線連接的類型進行建模,set_wire_load_mode命令用于設置連線負載模型的模式。有三種模式供選擇:top、segmented和enclosed。

- enclosed:連接B1和B2的連線負載模型用圍繞它們的模塊的負載模型代替,即用SUB的負載模型代替。

- top:連接B1和B2的連線負載模型用頂層模塊的負載模型代替,即用TOP的負載模型代替。

- segmented:分別用穿過的三段的模型相加得到。

set_wire_load_mode top

5、檢查

在設置完環境約束之后,可以用以下指令來檢查約束是否添加成功。

- check_timing:檢查設計是否有路徑未加入約束

- check_design:檢查設計中是否有懸空管腳或者輸出短接的情況

- write_script:將施加的約束和屬性寫到一個文件中,檢查該文件看看是否正確。

五、實例

下面是一個實際的tcl腳本。

![[Codevs] 1004 四子連棋](http://pic.xiahunao.cn/[Codevs] 1004 四子連棋)

方法)

)

:Path結合屬性動畫, 讓圖標動起來!)