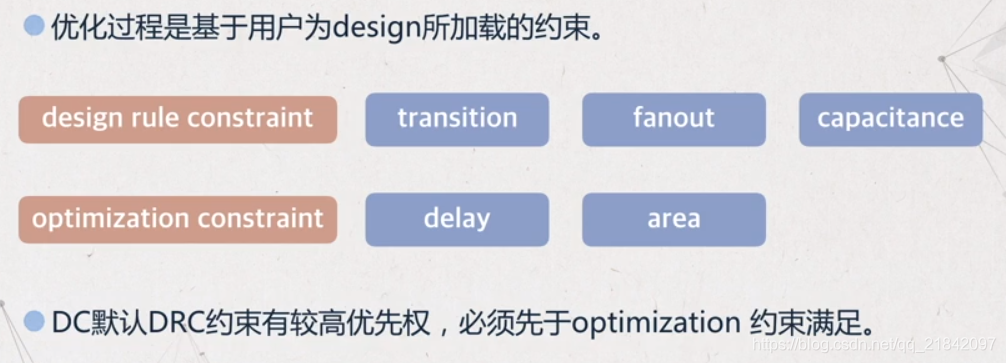

對進行時序路徑、工作環境、設計規則等進行約束完成之后,DC就可以進行綜合、優化時序了,DC在優化過程中主要的策略將在下面進行說明。然而,當普通模式下不能進行優化的,就需要我們進行編寫腳本來改進DC的優化來達到時序要求。

DC進行優化的目的是權衡timing和area約束,滿足用戶對功能、時序和面積的要求。

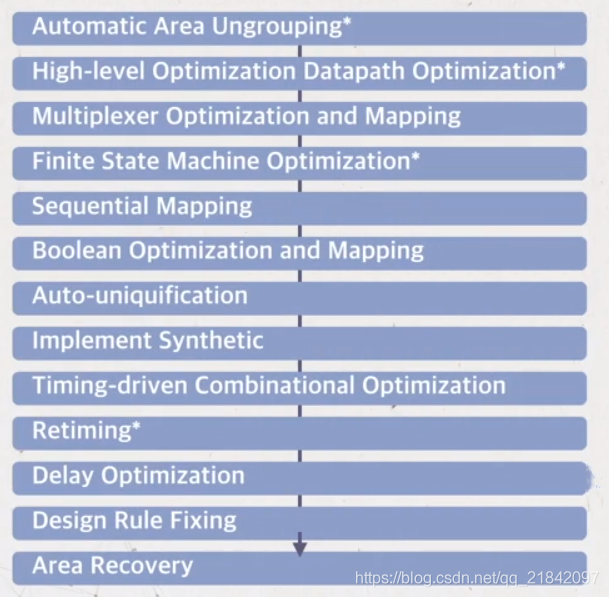

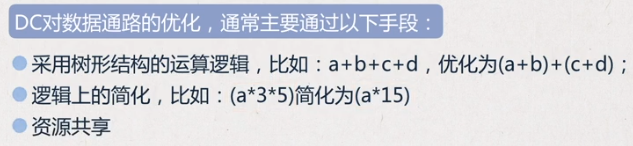

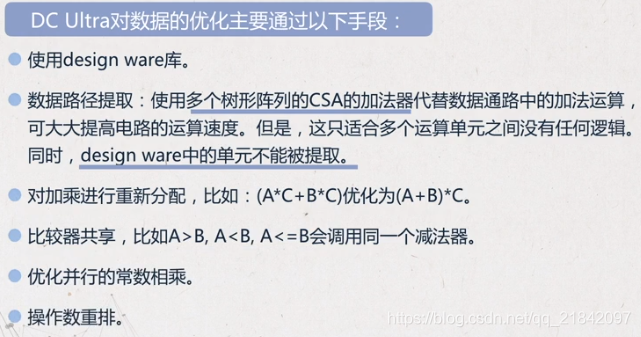

DC優化有很多策略,包括對數據通道的優化,對狀態機的優化,對布爾邏輯的優化等。

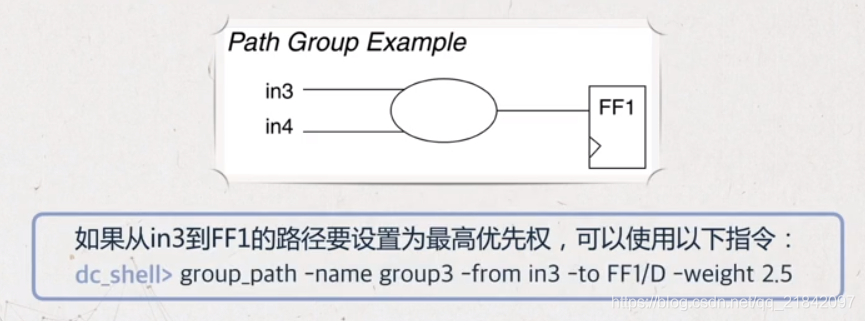

一、creating group path

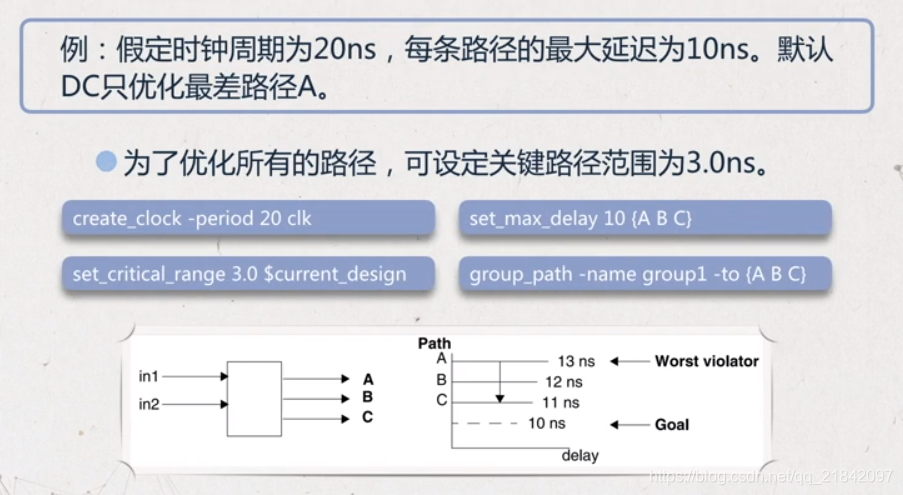

默認情況下,DC根據不同的時鐘劃分path group。但如果設計中存在復雜的時鐘,復雜的時序要求或者復雜的約束,用戶可以將所關心的幾條關鍵路徑劃分為一個path group,指定DC專注于改組路徑的優化。也可以對不同的路徑組設置不同的權重,權重值從0到100。

默認情況下,DC只優化關鍵路徑,即負SLACK最差的路徑,如果在關鍵路徑附近指定一個范圍,那么DC會優化指定范圍內的路徑。由于優化的路徑越多,DC運行時間越長。一般范圍設定為時鐘周期的10%。

二、high-effort compile

high-effort compile能夠讓DC更加努力地達到所約束地目標,該措施在關鍵路徑上進行重新綜合,同時對關鍵路徑周圍地邏輯進行了restructure和remap。

high-effort指令有兩種:

- compile ultra command:附帶兩個option,這兩個option分別包含一些腳本,提供額外地時序和面積地優化。option為:area_high_effort_script option和timing_high_effort_script option。

- compile command:附帶一個option,map_effort -high option。

High effort對關鍵路徑地優化包括邏輯復制(Logic Duplication)和映射為大扇入的門單元(Mapping to Wide_Fanin Gates)。

此外,incremental指令也可以提高電路優化的性能。如果電路在compile之后不滿足約束,通過incremental也許能夠達到要求的結果。incremental指令只進行門級的優化,而不是邏輯功能級,會導致大量的計算時間,但是對于將最差的負slack減為0,這是最有效的辦法。?

為了在使用incremental指令時,減少DC的運算時間,可以將滿足時序要求的模塊設置為dont_touch屬性。

dont_touch noncritical_blocks

對于有很多違例邏輯模塊的設計,通常incremental最有效。

compile -map_effort high -incremental_mapping

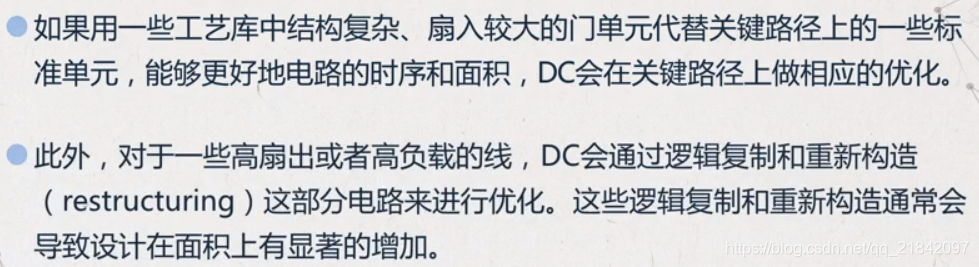

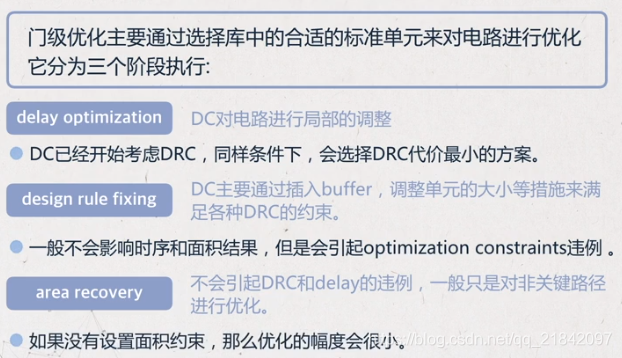

? 三、gate-level optimizations

?

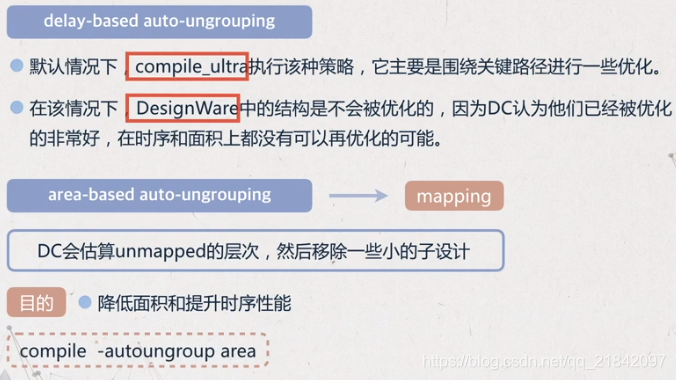

四、Automatic Ungrouping

Ungrouping 取消設計中的層次,移除層次的邊界,并且允許DC Ultra通過減少邏輯級數改進時序,以及用過共享資源減小面積。常見指令如下:compile_ultra,compile -auto_ungroup。

compile會提供兩種策略,包括:delay-based auto-ungrouping,?area-based auto-ungrouping。

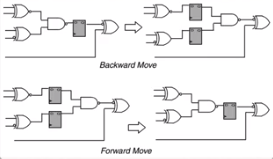

五、adaptive retiming

如果在邏輯綜合過程中發現設計的流水線劃分不平衡,就可以使用retiming策略,在時序路徑上前后移動寄存器,以提高電路的時序性能。

由上圖所示,retiming可能會對面積產生影響,則如果有違例的路徑,則調整寄存器的位置;如果沒有違例的路徑,則可以用來減少寄存器的數量。

DC在移動寄存器的優化中,只能對有相同約束的寄存器進行調整,如果兩個寄存器約束不同,則不能一起移動。移動后的寄存器在網表中的名字通常帶有一個R的前綴和一個系列號。

retiming的策略不能和compile_ultra的以下option一起使用:-incremental -top -only_design_rule

六、High-level optimization and datapath optimization

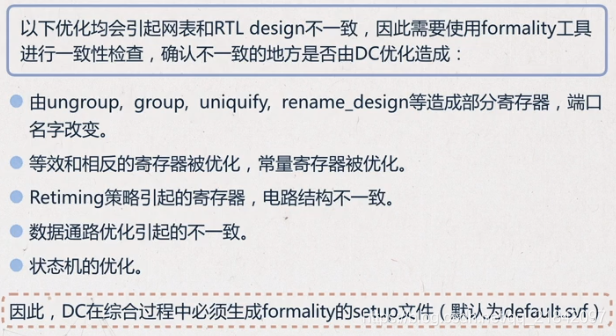

七、verifying functional equivalence

?

?

?

方法)

)

:Path結合屬性動畫, 讓圖標動起來!)

![[LeetCode_5] Longest Palindromic Substring](http://pic.xiahunao.cn/[LeetCode_5] Longest Palindromic Substring)