SLVS summarize

一、概述

?????? SLVS-EC高速串行接口技術,在CIS和DSP(數字信號處理器)之間實現了高幀率的寬帶像素數據傳輸。

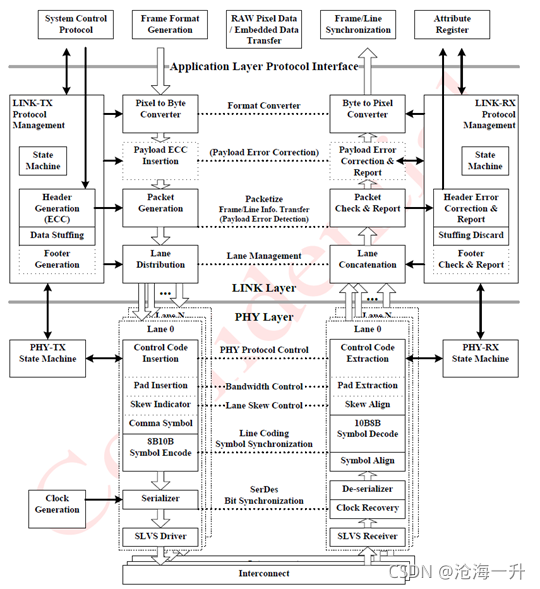

????????SLVS-EC引入了一個優化的數據包格式和控制協議,幾乎沒有冗余,而且結構簡單,僅由兩層組成:

- LINK層,利用并行結構實現寬帶數據的格式處理;

- PHY層,能夠以低功耗提供高速數據傳輸。

????????同時SLVS-EC也引入了一個可擴展的FEC(前向糾錯)功能,作為數據傳輸錯誤的控制協議,而數據傳輸錯誤是高速串行接口的主要影響因素。這實現了高度可靠的數據傳輸,并根據應用將冗余度降至最低,且延遲較低。

????????此外,發射器和接收器的推薦電氣特性被指定為CIS和DSP之間的接口。這樣就能以高速、低功耗、小面積的PHY電路實現高性能。

二、定義與縮寫

| Lane | 一個單向的點對點差分串行連接,包括一個TX-PHY和一個RX-PHY,以及一個與差分傳輸線的互連。 |

| Symbol | 8B/10B編碼產生的一個10位數據 |

| Comma Symbol | 用于symbol之間對齊的特殊symbol |

| Control Code | 控制PHY協議序列的控制碼 |

三、架構

1、系統拓撲

?????? SLVS-EC提供可擴展的配置,以支持CIS和DSP之間的各種系統拓撲結構。

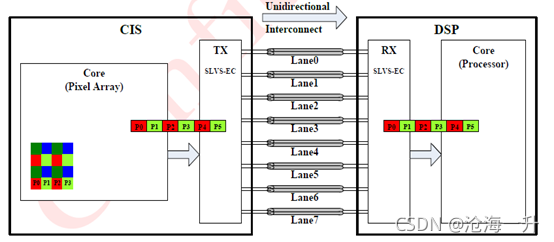

?????? 像素數據通過一對SLVS-EC的發射器(TX)和接收器(RX)從一個CIS傳輸到一個DSP。SLVS-EC只提供從CIS到DSP的單向數據傳輸。每個SLVS-EC的TX和RX所支持的Lane的最大數量應是8個Lane。

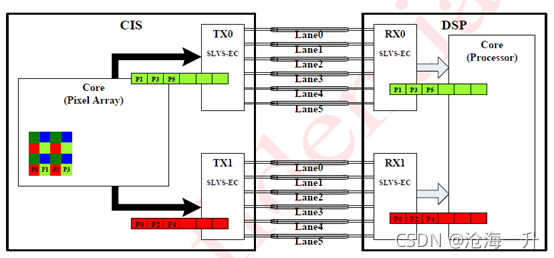

?????? 如果需要超過8個Lanes的帶寬,那么可以使用多個SLVS-EC接口。

?????? 此外,SLVS-EC也支持多個CIS傳輸到一個DSP的情形。

2、層次結構

四、應用層

?????? 應用層(CIS和DSP)括從CIS輸入或輸出到DSP的數據格式,以指定應用層的定義和約束,還包括SLVS-EC接口使用的幀格式和LINK/PHY協議的必要規范。

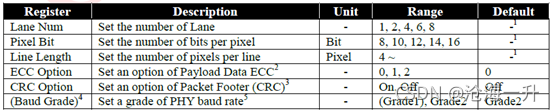

?????? SLVS-EC接口支持RAW8、RAW10、RAW12、RAW14、RAW16。每一行的長度需要為4的整數倍。

?????? 幀格式也是在是由應用層(CIS)功能配置的。通過使用包頭和該接口的其他功能嵌入幀和行信息,幀格式可以在DSP側正確傳輸和重新配置。

?????????應用層可以傳輸嵌入在RAW像素數據流中的輔助信息,如CIS配置的寄存器值,這里稱為嵌入數據。為了便于區分嵌入式數據線和DSP(RX)端的其他線,SLVS-EC接口支持通過包頭傳輸功能為包含嵌入式數據的線傳輸一個指示位。

?????? 此外,在應用層可以設置寄存器參數

五、LINK Layer

?????? LINK層的主要作用是將幀和行信息添加到從應用層(CIS)輸入的像素數據中,將數據組裝成數據包,并將其輸出到各Lane的PHY層;在RX側收集各lane的PHY輸入的接收數據,從數據包中提取像素數據、幀信息和其他信息,并輸出到應用層(DSP),進行糾錯編碼和解碼等處理。

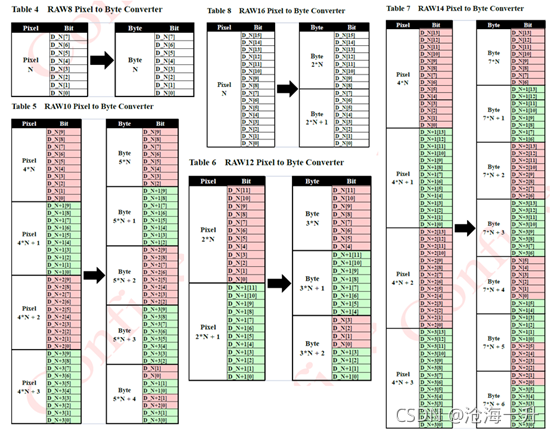

1、Pixel to Byte

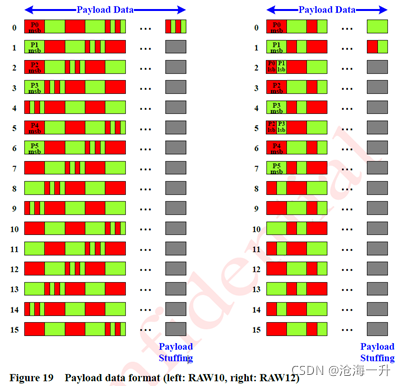

2、有效載荷數據

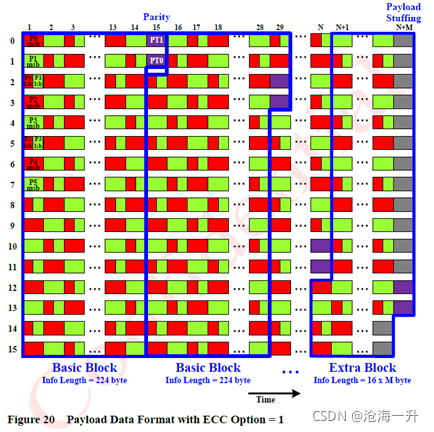

有效載荷數據指的是使用數據包發送的數據內容,是不包括幀頭和幀尾等的數據。有效載荷數據由轉換后的字節數據和有效載荷填充物組成。

?????? 有效載荷填充物的值為8’b0。長度如下:

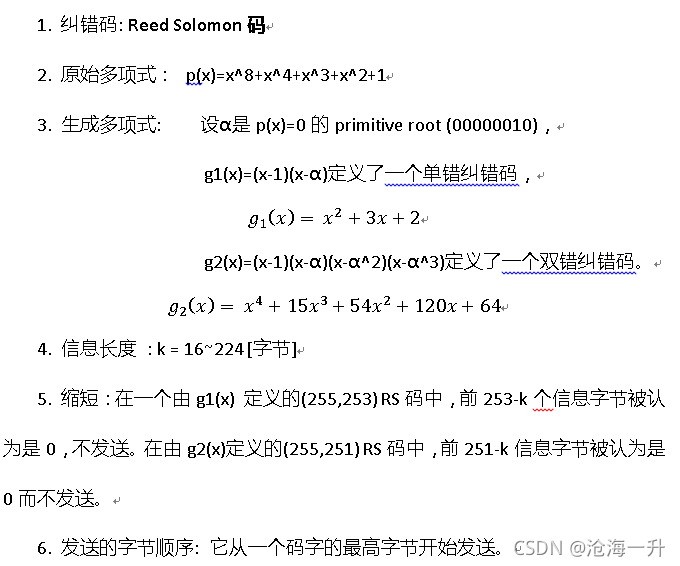

3、有效載荷數據糾錯

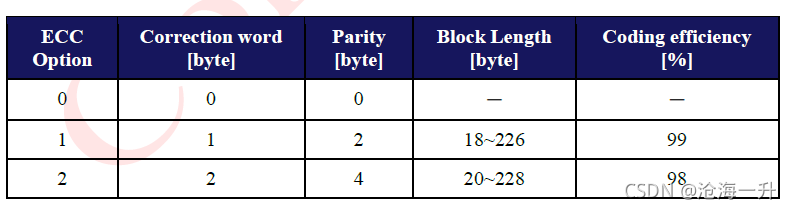

????????因為隨機數據錯誤的發生取決于PHY層的比特錯誤特性,提供有效載荷數據糾錯的功能是為了糾正這種像素數據的損壞,并提高所有SLVS-EC接口的有效比特錯誤性能。此外,SLVS-EC的糾錯性能可以被配置,稱為可擴展的FEC功能。該功能可通過配置寄存器(ECC選項)進行配置。

????????有效載荷數據糾錯的規范定義如下:

?

?

????????信息長度被定義為部分有效載荷數據中經奇偶校驗后的字節數。配置選項為

????????其中,Block Length = Info Length + Parity [byte]

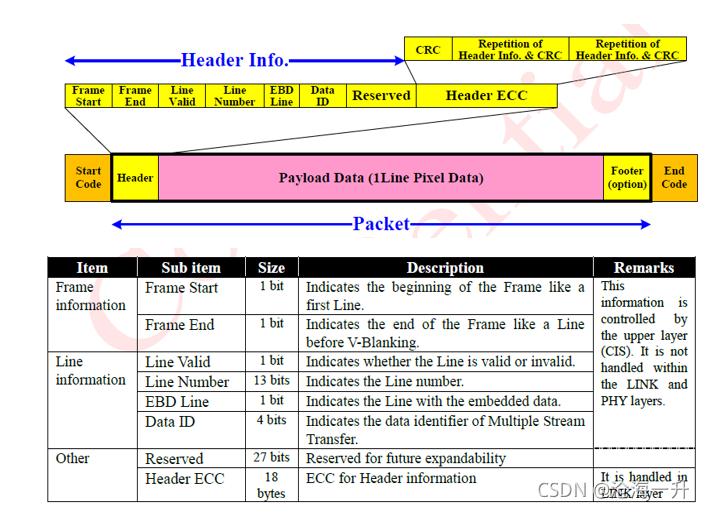

4、數據包Header的生成

?????? Header信息時發生錯誤,錯誤被CRC檢測到,重復傳輸的其他頭信息(其中沒有檢測到錯誤)可以用來在RX端重現正確的信息。

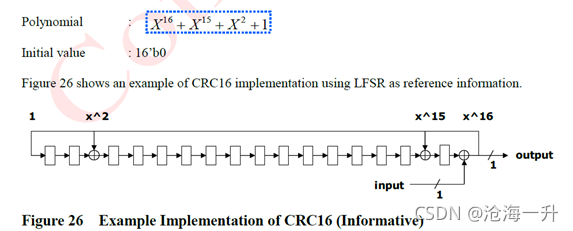

????????此數據包header 的CRC采用CRC16:

5、數據包Footer的生成

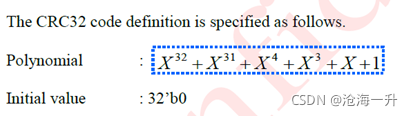

????????存儲在數據包頁腳中的信息是32階CRC碼(CRC32),用于檢測數據包中有效載荷數據的傳輸錯誤。通過將配置寄存器中的CRC選項設置為 "ON",數據包Footer被添加并在有效載荷數據之后傳輸。這個選項功能的主要應用被認為是在傳輸有效載荷數據是嵌入式數據時,對嵌入式數據傳輸錯誤的一種對策。CRC32的實現成本相對較小,所以使用CRC選項代替有效載荷數據ECC功能可以幫助減少傳輸少量嵌入式數據的應用的電路實現成本。

?

?

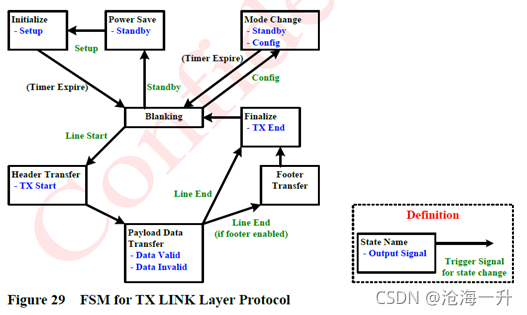

6、狀態機

?

?

?

1. Blanking:該狀態對應于圖像信息的H- Blanking。在這種狀態下,LINK層要么在傳輸一行圖像數據之前生成數據包Header,要么在數據包輸出后等待PHY控制代碼傳輸的完成。

2. Header transfer:該狀態將數據包頭從LINK層傳輸到PHY層。

3. payload data transfer。該狀態從LINK層輸出有效載荷數據(包括ECC)。

4. Footer transfer。該狀態從LINK層傳輸數據包的Footer。

5. Finalize:該狀態命令將表示數據包結束的控制代碼從LINK層傳輸到PHY層。6. Mode change:該狀態根據配置寄存器的設置,改變LINK層和PHY層的設置

7. Power save:該狀態可以通過停止LINK層和PHY層的時鐘和偏置電流等來降低功耗。在此狀態下,TX和RX不能進行通信。(此狀態也可用于改變LINK層和PHY層的設置)。)

8. Initialize:該狀態指示PHY層開始Training sequence以從power save狀態返回,并等待系統準備好進行通信。

?五、PHY Layer

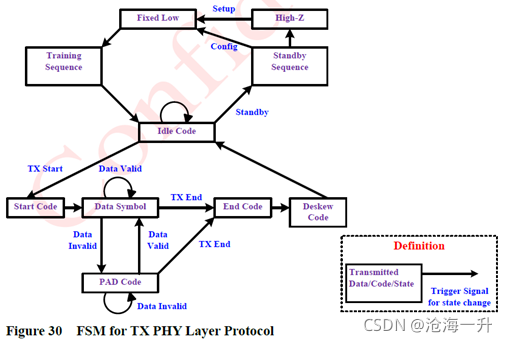

1、狀態機

?

?

1. Idle code: 該狀態表示除數據包傳輸外的空閑,并持續發送Idle code。

2.start code。該狀態下傳輸表示數據包傳輸開始的start code。

3.data symbol:該狀態從LINK層向互連網傳輸有效的包數據。

4.pad code。當沒有收到來自LINK層的有效數據包時,該狀態會傳輸假數據。

5.end code。該狀態下傳輸的控制代碼表示數據包傳輸的結束。

6.deskew code。該狀態傳輸控制碼,在數據包傳輸結束后調整通道間的偏移。

7.Standby Sequence: 該狀態按照屬性寄存器的設置傳輸待機序列。

8.High-Z : 該狀態可以通過驅動互連到高阻抗狀態,并在必要時停止時鐘和其他操作來降低功耗。

9. fixed low。該狀態在屬性寄存器中設定的周期內持續驅動互連到差分低電平狀態。

10. training sequence。該狀態按照屬性寄存器的設置傳輸training sequence。

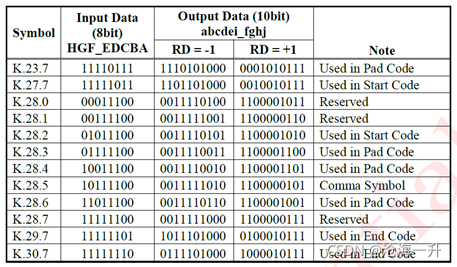

2、控制碼

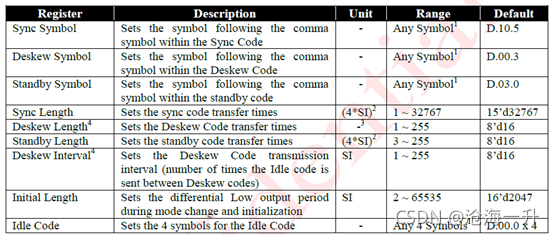

顯示了PHY控制碼的定義和分配的8B/10B符號配置。

?

?

3、Symbol Encoding

采用8b/10b編碼,控制碼采用到的編表如下:

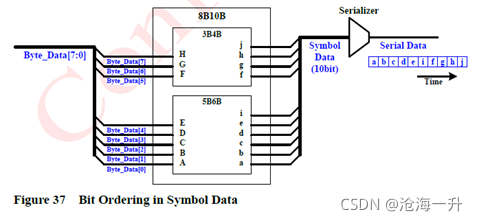

4、數據比特序

?

?

?????? 字節數據的第0位被輸入到8b/10b端口A,10位符號數據作為串行數據從a開始傳輸。

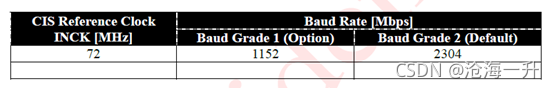

5、波特率

?????? SLVS-EC接口采用波特率。每個Lane的 PHY 比特率定義為下表中的波特率。

????????PHY總帶寬一般由配置寄存器中的Lane Num設置控制,而不是波特率等級設置。因此,波特率應固定為波特率等級2(默認設置),而不是改變為波特率等級1,這是一個可選的設置。

六、小結

- 糾錯碼

整個SLVS使用了三類糾錯碼:RS碼、CRC16、CRC32

| 糾錯碼 | 使用說明 |

| RS碼 | 用于有效載荷數據的糾錯 |

| CRC16 | 對數據包的糾錯,存放在數據包Header |

| CRC32 | 在有效載荷數據為嵌入式數據時進行糾錯,存放在數據包的Footer。 |

- PHY control code

IDLE code 可以通過寄存器進行配置。默認值為D.00.0 x 4

?

?????????

)

——mysql事務和鎖InnoDB(擴展))

)

)

![[js高手之路]構造函數的基本特性與優缺點](http://pic.xiahunao.cn/[js高手之路]構造函數的基本特性與優缺點)