? ? ? ? 完整的STA需要滿足以下兩點:

- 完整的設計約束(完整并不意味著正確)

- 運行所有需要的時序檢查

? ? ? ? 可以用以下兩條命令來進行完整性的檢查:

check_timing? ? ? ? ? ? ? ? ? ? ? ? ????????// 檢查是否缺少了約束條件

report_analysis_coverage? ? ? ? ? ? // 檢查是否是否對時序進行check? ? ? ? ??

一、檢查約束的完整性

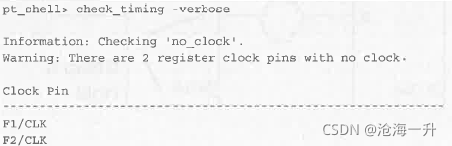

????????check_timing 這一命令會檢查設計中的每個現有約束,如果有缺失的約束,則會發出警告,我們可以根據警告對設置的約束進行檢查。

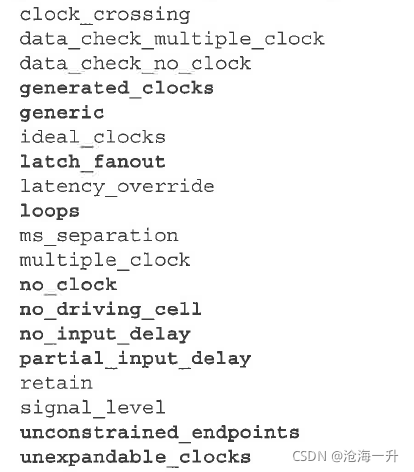

????????check_timing的完整檢查項目如下,粗體表示默認選項:

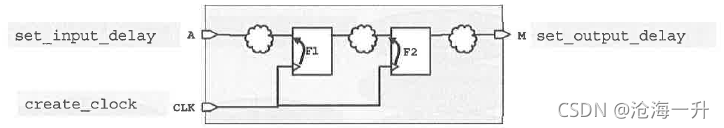

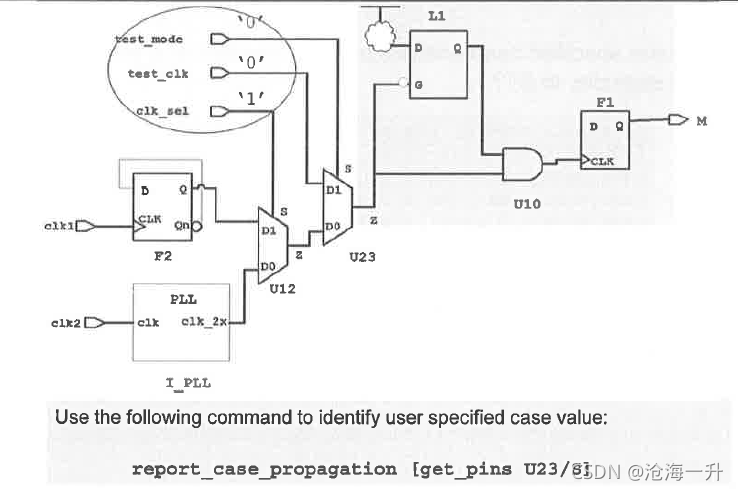

? ? ? ? 我們以下圖所示電路為例,對check_timing的檢查內容進行說明。

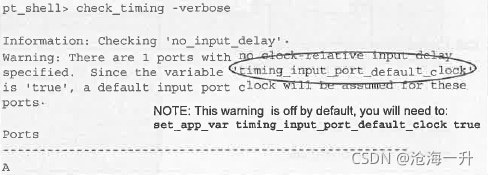

1、No input delay

????????這類警告是默認關閉的,你需要設置變量:

pt_shell>set_app_var timing_input_port_default_clock true

????????收到這種警告信息,我們需要知道:這個輸入引腳和什么相連?哪條路徑會受到這條警告的影響(或者此case缺少輸入端口的分析)?

????????我們需要檢查是否有必要約束這個port,一些情況下,是不需要為input port添加約束的

- 假設這個端口應該由set_case_analysis 命令設置,驅動一個固定的信號比如

- 假設以這個port為起點的路徑在當前模式的分析中是不存在的;

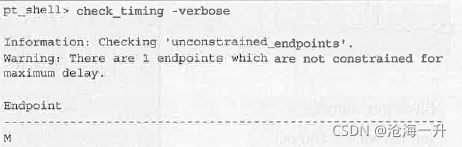

?2、No output delay

????????收到這類警告需要去知道:輸出端口連接的是什么,寄存器還是輸入端口?這條警告所影響的路徑是哪一條,他是否是一個輸出的時鐘端口?

? ? ? ? 輸出端口必須被output delay 所約束;

????????如果這個端口是一個輸出的時鐘端口,我們不需要為端口定義output_delay,創建所需要的generate_clock 然后忽略這條警告;

3、No clock

????????收到這類警告需要去知道:哪里需要創建一個時鐘去驅動受影響的端口;

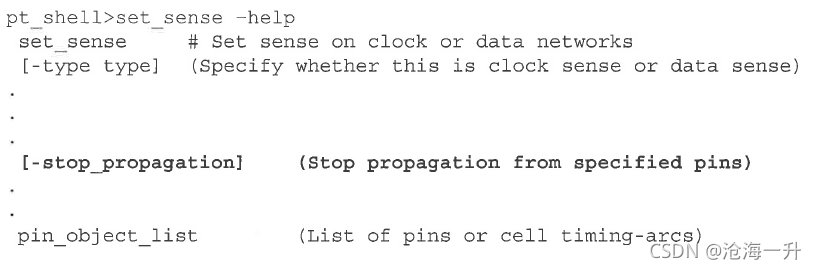

????????檢查時鐘信號是否由于某些時序弧的禁用或用戶使用set_sense命令手動停止信號而在時鐘端口的扇出中被阻斷。

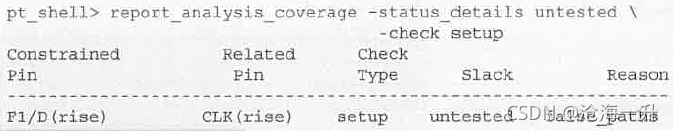

?二、檢查執行的完整性

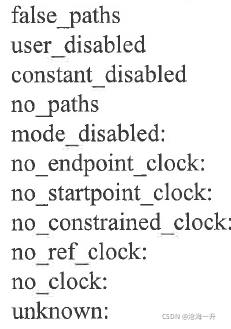

????????report _ analysis _coverage 這一命令會檢查設計中的每個現有時序檢查,如果有任何未執行,則會發出警告和原因。我們需要決定這個時序檢查是否有必要,還有檢查什么原因導致時序檢查沒有被執行。

? ? ? ? 導致時序檢查未執行的原因由下面這些:

? ? ? ? 我們以下圖為例,對這些原因進行具體的說明。

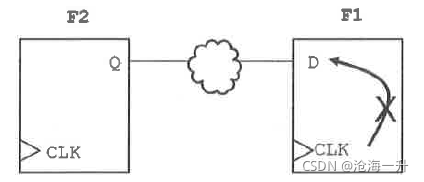

1、False path

????????false_path一般是用戶使用set_false_paths指定,異步或者專用的時鐘組;

????????收到此類的警告,我們需要去知道:1.這條時序路徑包含哪個時鐘?2.F1的上一級觸發器是什么?3.哪條false_path的命令或者clock_group的命令與此warning相關

? ? ? ? 設置false path使用的命令為

pt_shell > set_false_path -from F2/CLK -to F1/D

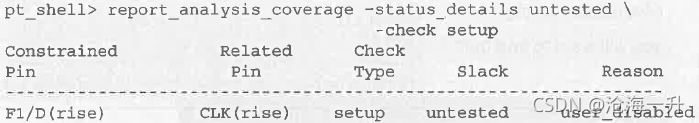

2、user disabled

????????出現此類的warning,我們需要去知道:這個時序檢查只是對指定cell(F1)無效還是定義在cell庫中,對所有instance都無效?這兩者在命令的書寫上是不同的:

pt_shell > set_disable_timing -from CLK -to D F1

pt_shell > set_disable_timing -from CLK -to D {get_lib_cell core_slow.db/fdesf2a15}

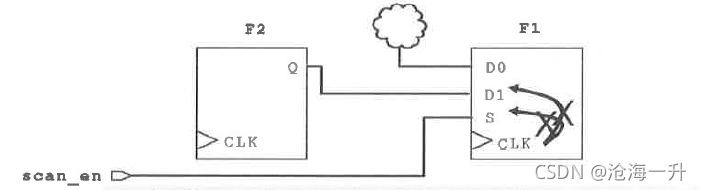

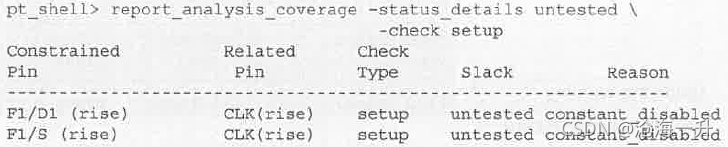

3、constant_disable

????????這種警告一般出現在:

- 用戶指定 set_case_analysis

- 信號固定為高電平或低電平;

? ? ? ? 出現此警告我們需要確認,這個timing的disable是不是由于用戶指定的case或者恒高或者恒低電平的信號導致的;用戶哪條約束導致了 timing的disable。

pt_shell > set_case_analysis 0 scan_en

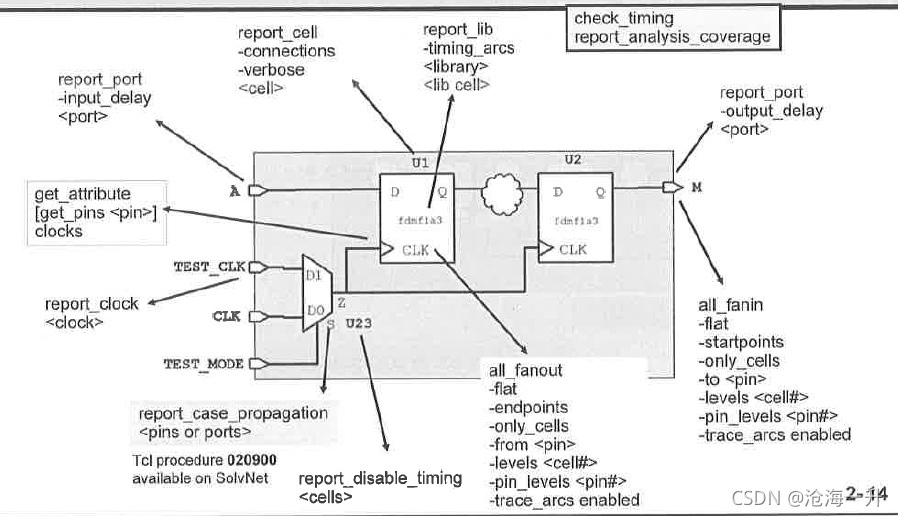

三、Debug命令

? ? ? ? 當使用check_timing 和 report_analysis_coverage 命令對約束進行檢查時,按上文所述,有可能出現一些warning,這時我們需要對出現的warning進行檢查,最常用的debug命令如下圖:

? ? ? ? 這些命令可以讓我們快速定位問題所在。

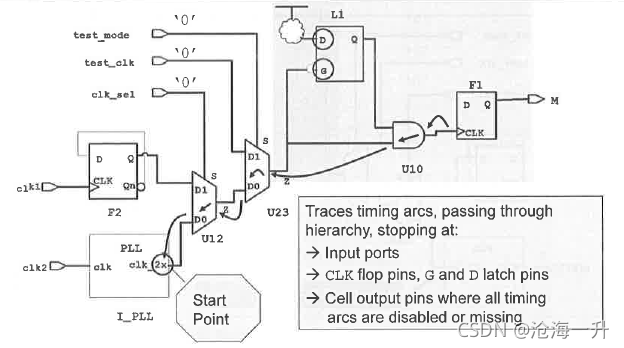

1、all_fanin

????????

? ? ? ? ?如上圖,當F1的clk端發出no clock warning,我們可以使用以下命令

pt_shell > all_fanin ?-startpoints -flat -to F1/CLK

? ? ? ? 即可以找到CLK的起始點,溯源問題發生的原因。

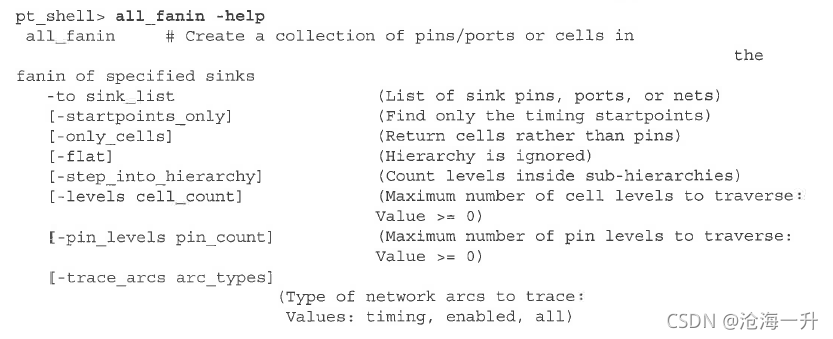

? ? ? ? all_fanin的用法如下:

? ? ? ? 如例子中的圖所示,all_fanin會追蹤時序弧,最后在三種端口停下:

- 輸入端口(input port)

- CLK flop pins ,鎖存器的G和D pins

- 時序弧被disable或missing的cell 的輸出pins

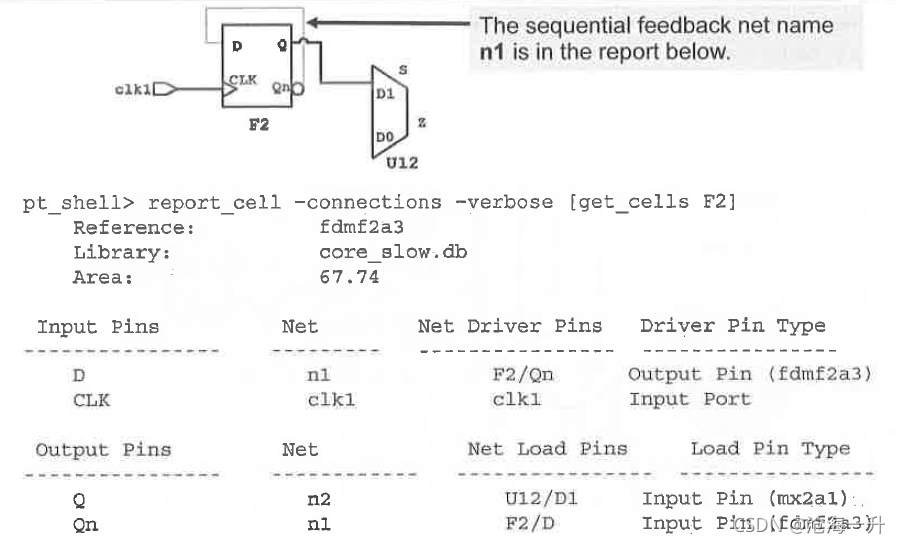

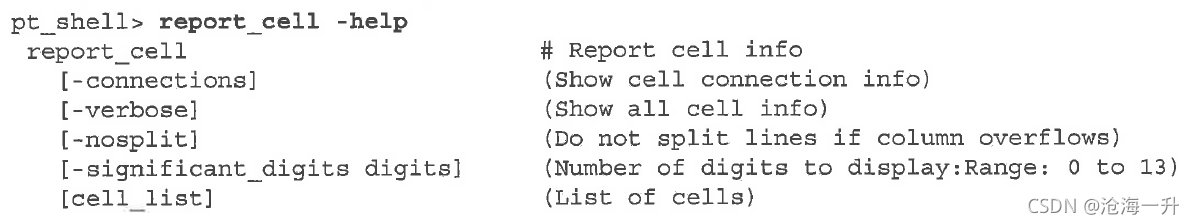

2、report_cell

? ? ? ? 如果我們定位到了問題的所在,可以使用report_cell命令查看該單元的詳細信息。

? ? ? ? report_cell的用法如下:

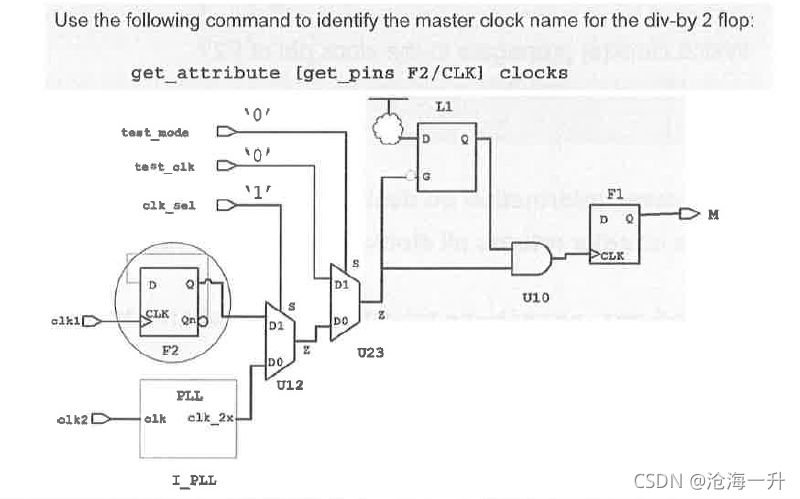

3、get_attribute

? ? ? ? PrimeTime中,針對每一個設計對象(design objects)的信息都存儲在attribute中,我們可以利用get_attribute命令來獲取單獨的設計對象的信息。

? ? ? ? 上圖中,指定的clocks這一attribute存儲了所有穿過該pin的時鐘信息。

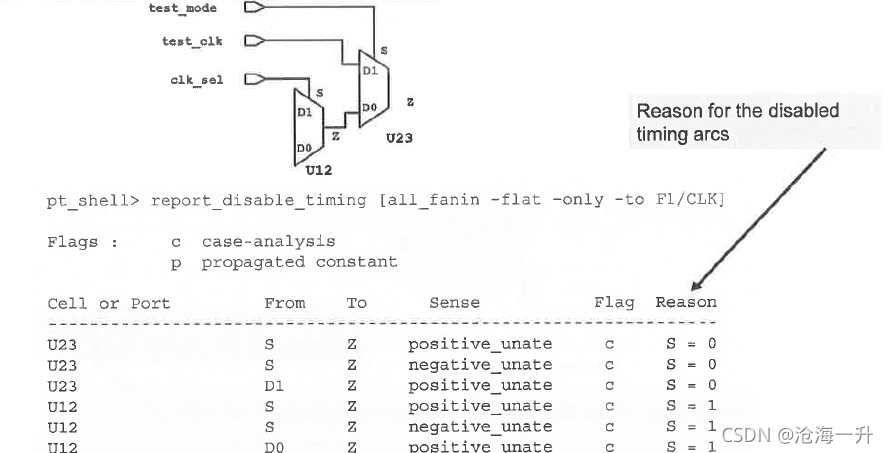

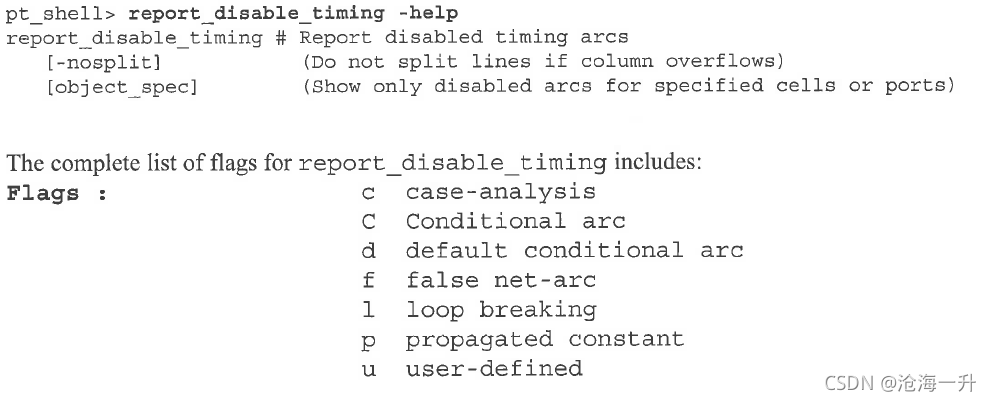

4、report_disable_timing

??????????report_disable_timing這一命令會檢查disable的時序弧,并給出原因。

? ? ? ? 其具體用法如下:

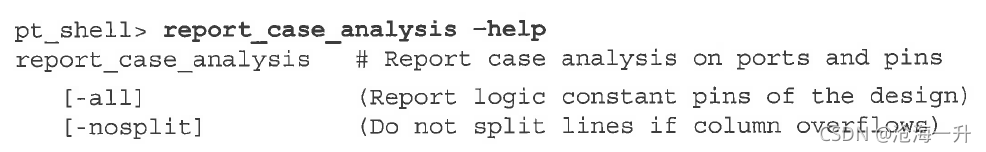

5、report_case_propagation

? ? ? ? 我們可以使用?report_case_propagation命令來查找用戶定義的值。

? ? ? ? 其用法如下

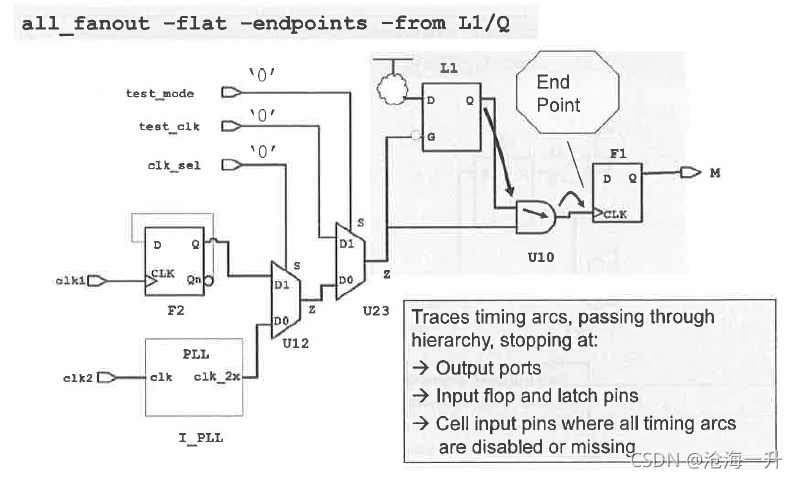

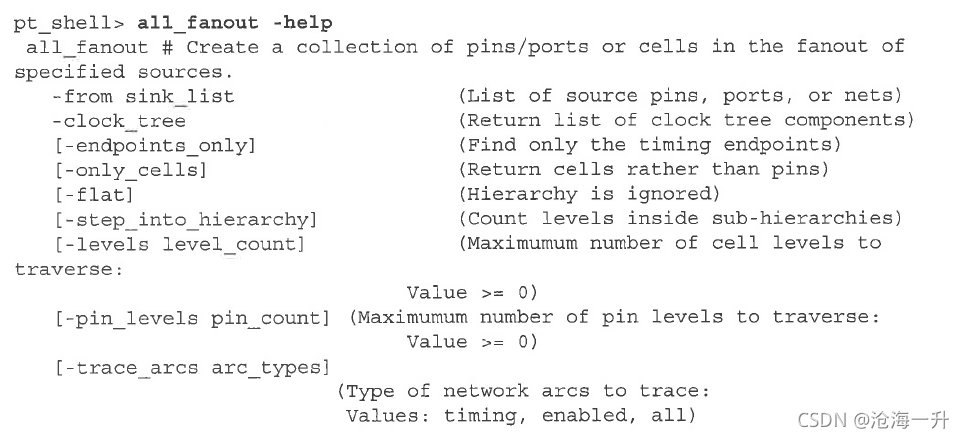

6、all_fanout

? ? ? ? 這一命令與all_fanin類似:

? ? ? ? 用法也基本一致:

?

?

? ? ? ? 合理利用PT提供的命令,我們可以很快地找到問題的所在,快速修改時序約束不合理的地方。

——mysql事務和鎖InnoDB(擴展))

)

)

![[js高手之路]構造函數的基本特性與優缺點](http://pic.xiahunao.cn/[js高手之路]構造函數的基本特性與優缺點)