????????隨著集成電路制造工藝技術的迅速發展,集成電路集成度迅速攀升,制造流程及工藝步驟日趨復雜,工藝尺寸也在不斷縮小。集成電路可制造性設計(Design For Manufacturability,DFM)?以直接提升集成電路芯片的良品率及降低芯片的生產成本為主要目的,越來越引起業界的關注。

????????隨著集成電路工藝尺寸的進步,DFM 對芯片良率的影響日益凸顯,隨著工藝尺寸的演進,到了超深亞微米90nm 及以下,工藝和設計因素對芯片良品率的影響急劇增加。因此在超深亞微米考慮可制造性是十分有必要。

一、深亞微米時代的可制造性設計問題

????????在傳統的數字后端設計中,版圖的物理設計一般通過了DRC、LVS 的物理驗證,即可保證芯片質量及良品率。然而隨著工藝尺寸進入深亞微米,一些制造技術如光刻膠曝光、顯影、刻蝕和化學機械拋光都會對金屬互連結構造成不利影響,并隨著布局的局部特征而變化,這將使得傳統的數字后端設計方法面臨嚴峻的挑戰。

????????可制造性設計是為了提升芯片生產良率的而定制的設計規則。它將設計與生產之間的聯系變得更加緊密。換句話說,完整的可制造性設計方案能夠讓IC 設計者更早的使用可制造性設計流程與規范,來提升芯片的設計、生產效率。因此,從版圖設計者的角度來說,需要有一套適應深亞微米的可制造性設計流程來指導版圖的設計與驗證工作。在過去的芯片設計中,IC 設計者可以直接將滿足物理驗證的電路設計交給代工廠,進行生產制造。但是在進入先進制程(180nm

以下)工藝后便遇到了困難,主要體現在以下幾個方面。

1、CMOS閂鎖效應

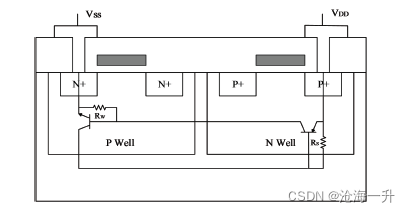

????????MOSFET 為四端器件,包括源(S)、柵(G)、漏(D)、襯底(Sub),在現代CMOS 雙阱工藝中,P 阱連接VSS,N 阱連接VDD,這種雙阱CMOS 結構將產生寄生雙極晶體管:P 阱存在NPN 晶體管,N 阱存在PNP 晶體管,構成SCR(Silicon Controlled Rectifier)寄生結構。

????????當P 管源極輸入一個正向觸發信號,在電源VDD 和地線VSS 之間由于寄生的PNP 和NPN 雙極性晶體管。當無外界干擾未引起觸發時,兩個晶體管均處于截止狀態,集電極電流增益非常小,因此閂鎖效應不會產生。但當其中一個晶體管的集電極電流由于受外部干擾而突然增加到一定值時,會反饋至另一個晶體管,從而使兩個晶體管因觸發而導通(通常情況下是PNP 比較容易觸發起來),VDD 至VSS 之間形成低抗通路。之后就算外界干擾消失,由于兩三極管之間形成正反饋,還是會有電源VDD和地VSS 之間的漏電(鎖定狀態),閂鎖效應由此而產生。隨著集成電路制造工藝的發展, 晶體管的集成度越來越高,產生閂鎖效應的可能性會越來越大。

2、金屬互連問題

????????隨著集成電路制造工藝的不斷復雜化,互連金屬層的不斷增加,以及工藝節點的不斷降低,互連制造問題已成為制約納米CMOS 工藝芯片生產制造成品率(Yield)的最大因素。一方面,工藝節點降低帶來的工藝偏差,會產生越來越多的刻蝕錯位,大大增加通孔失效的概率。另一方面,版圖的密度效應問題會使金屬在化學機械拋光過程中出現版圖表面的高低起伏。倘若金屬互連的通孔在制造過程出現這種現象,就很有可能造成層間金屬互連失效,特別是進入深亞微

米時代后,銅互連技術的大量應用使互連線通孔失效的現象發生的越來越頻繁。

3、天線效應

????????在芯片生產過程中,暴露的金屬線或多晶硅(polysilicon)等導體,就像是一根根天線,會收集電荷導致電位升高。天線越長,收集的電荷也就越多,電壓就越高。若這片導體碰巧只接了MOS 柵,那么高電壓就可能把薄柵氧化層擊穿,使電路失效,這種現象就是“天線效應(PAE)”。

?????????隨著半導體制造工藝的不斷進步,等離子體Plasma 干法刻蝕技術因其各向異性、高的選擇比等優點被廣泛用來刻蝕金屬與半導體材料。該方法通過使用放電產生的等離子體與刻蝕材料接觸發生化學反應實現刻蝕過程。干法刻蝕方法的缺點是增加了半導體內部游離的等離子體電荷數目,這無疑會增加天線效應發生的概率。

4、隨機顆粒缺陷

????????半導體制造工藝過程中許多工藝節點都會引入沾污而產生隨機顆粒缺陷(Random Particle Defects)。如果在一條或兩條較窄的互連線之間存在著隨機顆粒缺陷,則可能造成互連線短路或斷路,如圖:

????????傳統上,芯片制造廠商通過制定最小線寬、最小間距等設計規則避免隨機性誤差對良品率的影響。版圖設計者只要遵守最小設計規則就可以減少由顆粒引起的電路短路或者開路現象。但隨著集成電路進入超深亞微米時代,電路的特征尺寸在不斷減小,而引起隨機性誤差的顆粒幾何尺寸并沒有隨之變小,顆粒尺寸逐漸可以與特征尺寸相比擬,使得納米級電路的成品率對隨機誤差更加敏感。

????????隨機顆粒缺陷的位置可以通過關鍵區域(Critical Area)來進行描述,其良率Y可以由泊松等式來描述。

????????CA 表示關鍵區域面積,DD 表示工藝固有缺陷密度。

????????所謂關鍵區域,是指如果隨機缺陷的中心落在這個范圍內,就會發生電路故障(產量損失)的區域。

????????對于一個確定的版圖來說,隨機顆粒缺陷尺寸越大,則關鍵區域面積越大,芯片良率損失也會越大。通常關鍵區域CA 面積由版圖設計者決定,工藝固有缺陷密度由代工廠決定。

5、版圖圖形密度

????????在深亞微米制造工藝中,化學機械拋光(CMP)技術被廣泛應用于版圖表面的平坦化,該技術通過拋光頭與基片之間的化學反應與機械運動來實現基片表面的平坦化,但最終獲得的圖形表面平整度往往會受到版圖圖形密度影響。

CMP 是利用拋光液中化學添加劑的化學作用,首先與晶片表面材料進行化學反應,形成易去除的薄膜反應層,再通過拋光墊于晶片之間的研磨料的摩擦作用,去除前期形成的薄膜反應層,最后,通過拋光液的攜帶作用,將拋光去除的材料帶離晶片表面,露出新生表面,進一步再反應再去除,重復進行以去除表面的粗糙部位,達到平坦化目的。

?

????????所謂版圖圖形密度,是指在化學機械拋光過程中,版圖中圖形小間距、高密度區域的拋光速度比大圖形間距、小密度的區域快。由于小而孤立、凸出的圖形在平坦化過程中要承受較

大壓力,所以拋光速度較快;低處圖形承受的壓力相對較小,所以拋光速度較慢。

????????由于圖形密度的差異,最終會造成版圖圖形的凹陷和侵蝕,如上圖所示。如果在通孔平坦化時出現這種現象,將很可能出現金屬互連線斷路的現象。

二、可制造性設計流程

? ? ? ? 加入可制造性設計的后端實現流程如下圖:

? ? ? ? 整個流程其實是針對CMOS 深亞微米出現的閂鎖效應,天線效應效應、金屬互連問題、版圖隨機缺陷及版圖圖形密度等可制造性問題,提了解決方案,并加入到傳統流程中。

提及的物理實現單元可見數字后端——物理單元介紹

1、Tap 單元插入(Tap Cell Insertion)

????????在CMOS 工藝中通過插入Tap 單元來解決并預防閂鎖效應,Tap 單元版圖如圖(a)所示。作為一類特殊的物理單元,阱連接單元(Well-Tap-Cell)是近年來在130nm 及以下更先進的物理設計中新增加的,它不存在任何邏輯功能與時序約束,主要用來限制電源(地)與襯底之間的電阻,減小閂鎖效應發生的幾率:通過Tap 單元將N well 連接至VDD,P 襯底連接至VSS,以電阻并連的方式降低N 阱寄生電阻RS、P 阱寄生電阻RW,從而降低寄生三極管的電流放大倍數,從而有效提高寄生SCR 網絡抗閂鎖的能力,如圖(b)所示。

2、天線二極管插入(Antenna Cell Insertion)

????????在實踐中,消除天線效應方法一般有三種,包括跳線法,添加天線二極管,插入緩沖器三種。

????????跳線法可以分為向上跳線法與向下跳線法兩種,即通過不同金屬間向上或向下的跳線來斷開存在天線效應的金屬層,經通孔連接到其他金屬層,然后再重新連接到當前層。跳線法雖然操作簡單,但會引入額外的通孔與金屬線,進而加劇線間串擾,產生額外的設計規則問題,因此在使用時要嚴格控制通孔數量與金屬布線層。

????????所謂添加天線二極管,是指在存在天線效應的金屬層上插入天線二極管單元,通過二極管的反向漏電流來釋放電荷,實現天線效應的消除,如下圖:

????????插入緩沖器,是通過在金屬導體長線上插入多級緩沖器的方法來消除天線效應。?

3、疊層通孔最小區域填充(Double Via Insertion)

????????金屬互連問題最有效的解決方法是疊層通孔最小區域填充,即在通孔旁路通過并連冗余通孔的方式來減小通孔失效的概率,如圖所示。

?????????這種方法不僅解決了通孔空洞(Voids in Vias)、金屬互連失效等問題,保證了金屬線之間的連通性,另外,因為通孔的電阻要大于金屬線,所以增加并連的通孔數目后還可以減小通孔電阻,減小線上延時,進而改善電路關鍵路徑的時序及功耗損失。因此在設計布線之后進行疊層通孔最小區域填充是非常必要的。

4、互連線全局擴展與加寬(Wire Spreading and Widing)

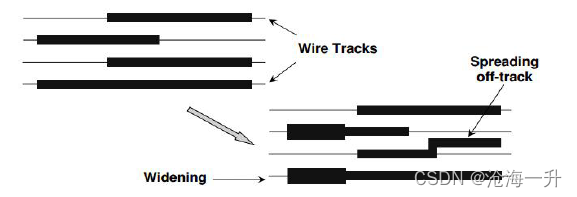

????????在芯片制造過程中,灰塵、微粒沾污都會引入隨機顆粒缺陷,增大版圖關鍵區域的面積,造成互連線短路或斷路的現象發生。(1)通過擴展互連線間距(Wire Spreading)的方法可以減小隨機缺陷對金屬線的影響,進而來降低版圖熱點分布的個數,減小關鍵區域面積。互連線間距一般會被擴大1/2 pitch 的距離,以降低關鍵區域發生短路的可能性。(2)減小斷路關鍵區域出現斷路的概率可以通過增大金屬線寬度(Widen),從而使金屬線能夠承受隨機缺陷帶來的影響,如圖所示。

????????在版圖關鍵區域分析階段,若線擴展與加寬操作未能使版圖熱點分布與數量有所減小,則需要重新進行布線,并將繞線模式設置為Density-Driven,這樣可以實現更均勻的走線分配與更小的走線間距。

5、Filler 單元的插入(Filler Cell Insertion)

????????即在版圖中密度低的區域插入一些填充單元(包括標準單元填充物與金屬填充物)來使版圖密度保持均勻,使在化學機械拋光過程獲得較好的平坦效果。為避免圖形平坦過程中出現侵蝕、凹陷現象,需要保持芯片整體密度的均勻性、一致性。任何影響導線橫截面的工藝都必須小心控制:第一點:寬金屬的侵蝕會減少其電流承載能力,使金屬線IR-Drop 更加嚴重,所以控制這一點對電源網絡分布至關重要。第二點:金屬線的侵蝕會使信號線的電阻變大,進而增加信號線上的延時。通常的做法是在版圖布線完成后在標準單元間隙插入填充單元(Filler Cell),填充單元是在標準單元庫中定義的與電路邏輯無關的填充物。

)

- 前端開發需要了解的工具集合:webpack, eslint, prettier, ...)