????????SpyGlass,這是一個很強大的RTL驗證級工具。它不僅僅能檢查sdc的錯誤,還能做以下各種檢查:Low Power, DFT,CDC(Cross Domain Check)。

一、基本概念

1、方法學相關

- Rule: 是SpyGlass 進行RTL分析的最小單位.

- Goal: 是一系列相關Rule的集合,組合起來完成RTL分析的某個特定任務. user可以用GuideWare定義好的Goal, 也可根據工程項目要求來選擇一系列rule的集合形成自定義Goal. GUI里面點Goal的button來選擇設定, 當然也可在Prj file 里定義.

- Sub-Methodology: 是一系列相關Goal的集合, 用以達成某方面特定目標, 如完成CDC check.目前包括 SpyGlass CDC/Constraints/DFT/Power/TXV Methodology2

2、 其他

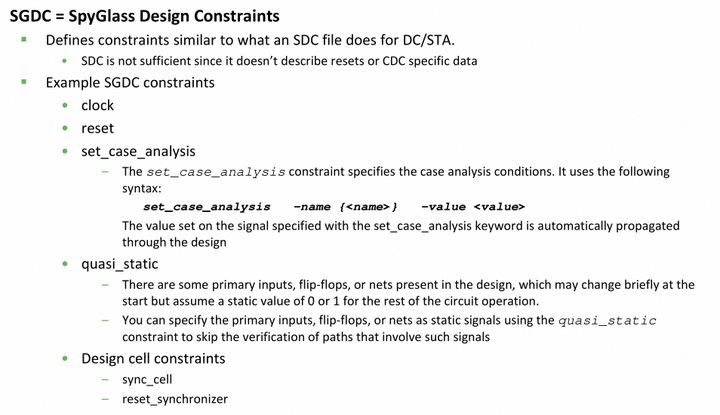

- SGDC : Constraint 文件, 主要包含clock和reset等約束信息.

- Waiver : 用以過濾一些結果的文件.

- Severity : report結果中分Fatal, Error, Warning和INFO四等級信息.

- parameter: 可以在進行RTL分析之前設定某些參數, 對檢查過程進行一些約束

二、流程簡介

????????SpyGlass的功能模型總結如下圖:

1、設置階段(setup stage)

? ? ? ? 設置階段的主要工作是:

- 添加設計文件、SGDC文件、預編譯文件和技術文件。

- 指定影響SpyGlass運行的各種設計讀取選項。例如,你可以在設計中指定頂層模塊、更改語言、指定宏等等。。

- 運行design-read流程來執行第一級的HDL分析。在進入下一階段之前,必須解決此階段報告的致命錯誤(FATAL)。

????????Spyglass 可以運行在BATCH 或者 GUI 模式。通常模式下是在batch模式下執行分析,在GUI模式下進行debug。使用命令如下:

spyglass -gui&

spyglass -project xxx.prj -designread -batch 1)工程(Project)文件

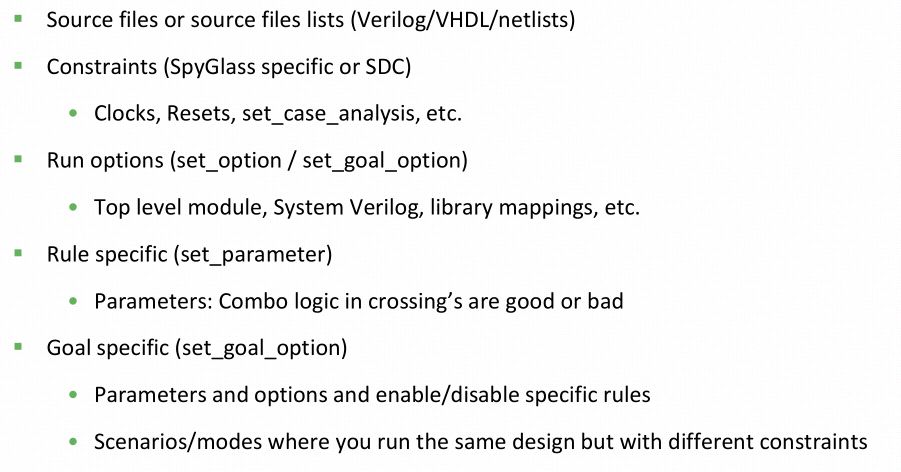

????????采用BATCH模式,這些設置都會添加到工程(Project)文件中,Project一般定義了以下內容:

????????需要讀入的文件及命令如下:

????????下面提供一個腳本范例:

#!SPYGLASS_PROJECT_FILE

#!VERSION 3.0

--------------------------------------------------------------

# This is a software generated project file. Manual edits to this

file could be lost during the next save operation

# Copyright Synopsys Inc.

# Last Updated By: SpyGlass SpyGlass_vL-2016.06

# Last Updated On Mon Dec 2 17:25:10 2019

-------------------------------------------------------------

##Data Import Section

read_file -type sourcelist cmd_files_ic

read_file -type sgdc xxx.sgdc

##Common Options Section

set_option top xxx

set_option projectwdir .

set_option language_mode mixed

set_option designread_enable_synthesis no

set_option designread_disable_flatten no

set_option enableSV yes

set_option disablev2k yes

set_option 87 no

set_option sdc2sgdc yes

set_option top xxx

set_option active_methodology

$SPYGLASS_HOME/GuideWare/latest/block/rtl_handoff

set_option sdc2sgdcfile xxx_sdc2sgdc.sgdc

set_option extractDomainInfo true

set_option stop { saradc_10bit_5vp15 reg_1p5_5vp15 por_lvd_5vp15

pch_5vp15 sensoradc_5vp15 osc800k_trim_5vp15 crystal_32k16m_5vp15

pll_800kto48m_5vp15 pad_cp pad_vdd pad_vss RASP256X9 RASP1536X9

pfm_1110skh32kx32_v1a0 gpio_ana_pad_5vp15 pad_vpp pad_avdh pad_avs

por2_5vp15 }

##Goal Setup Section

current_methodology

$SPYGLASS_HOME/GuideWare/latest/block/rtl_handoff

#current_goal cdc/cdc_setup_check -top xxx

set_parameter enable_generated_clocks yes

set_parameter write_sdc yes

set_parameter report_indirect_port_clock yes

set_parameter report_detail Clock_check10,all

set_parameter allow_combo_logic yes

set_parameter debug_proc yes

set_parameter enable_glitchfreecell_detection yes

set_parameter show_sdc_progress yes

set_parameter strict_sync_check no

set_parameter use_inferred_clocks yes

set_parameter show_all_sdc_violations yes

#set_parameter gen_block_sgdc -default

set_parameter allow_clock_on_output_port yes

set_parameter clock_gate_cell "ICG_V ICG"

set_parameter enable_sync_cell "sync_level, Sync_Pulse"

############2)約束(SGDC)文件

? ? ? ? SGDC包含的內容一般如下:

?????????SDC文件可以直接被SpyGlass讀取,自動轉換成SGDC,需要設置以下內容完成sdc2sgdc的轉換:

set_option sdc2sgdc yes????????在.sgdc 文件中只需要寫入下面語句就可以

current_design sssss

sdc_data -file sssss_src.sdc????????在目錄/constraints/sdc_check/spyglass_reports/sdc2sgdc/會有轉化后的sdgc 文件。在sdc2sgdc 時,sdc 和sgdc 可以混合,如下:

current_design sssss

clock -name clkA -period 10 -edge 0 5

//時鐘約束include ssss.sgdcset_case_analysis -name "sssss.atpg_test_en" -value 0

set_case_analysis -name "sssss..osc_sel" -value 1

//設置路徑分析sdc_data -file sssss_src.sdc //綜合時使用的約束文件reset -name "sssss.uAnd2.Z" -async -value 0

reset -name "sssss..POR_SRC" -async -value 0

//設置異步復位信號2、目標(Goal)設定和運行(Run)階段

????????在此階段將選擇并運行目標。目標是規則的集合。可以選擇規則,也可以指定規則執行的順序。

????????在SpyGlass CDC分析期間可以在不同的階段運行不同的SpyGlass CDC目標。在每個階段中,修復所報告的違例并轉移到下一個階段。如果不遵循這個分步驟的方法,可能會看到大量違反CDC的情況,其中大多數是由于不正確的設置或沒有修復前幾個階段的違例引起的。

? ? ? ? 這里我們以GUI界面為主進行介紹。

????????輸入命令進入gui 界面如下:

????????spyglass 類似pt,是靜態驗證工具。特點就是不需要編寫testbench,就可以驗證。

????????1. Adding Design Files----加入rtl 和sgdc 文件。這里需要通過set optin對Top Level Design Unit 進行設置。

????????2. Viewing and Changing Design Read Options

????????3. Running Design Read

? ? ? ? 點擊file -> new_project (對應sg_shell>new_project spyglass-1 –force 命令)

? ? ? ? 點擊Run Design Read?開始進行設計文件編譯和分析,在讀取完成后會在下方窗口列出問題。如下圖所示:

????????其中三個問題類型都為ErrorAnalyzeB Box,這是因為有的模塊文件沒有添加,SPYGLASS找不到,后面SPYGLASS會將其作為黑盒子處理。

????????左側instance下文件不同顏色標識意義為:

- 綠色表示該模塊可進行分析,但不可進行綜合;

- 黑色表示該模塊作為黑盒子存在;

- 白色表示該模塊可綜合。

????????需要注意,只是讀取設計并不會完成綜合,因此也不會創建相關的原理圖。因此,為了使用spyglass,首先應該解決黑盒子問題。

????????然后選擇不同目標進行檢查:

????????? 然后點擊Run Goal(s)?,當運行完成,會自動彈出Analyze Result窗口。

????????得到分析結果后,首先查看Lint分析結果。首先展開lint/lint_rtl文件夾消息。錯誤信息以紅色顯示,警告以橙色顯示,信息以綠色顯示。雙擊違規消息,此時與錯誤相關的代碼會在RTL代碼窗口中顯示出來。?此時可以對該問題進行分析。

? ? ? ? 可以通過手動添加waivers來放棄對一些電路的檢查:鼠標在違規信息上 ->?右鍵?->?Waive Selected Messages…

????????這將打開waivers編輯器窗口,并為其填充相關信息(違規消息、規則和設計單位(DU)):

????????可以在Comments字段中添加放棄的原因。做出任何更改后,單擊Apply。可以將Waiver設置保存為文件然后重復使用:在waivers編輯器窗口中右鍵點擊左側面板中文件,然后選擇Save Waiver Files。?SpyGlass會為每個Goal保存一個關于檢查過濾的文件。

3、生成報告

????????報表內容為運行的Goal的分析結果。有的功能需要使用SpyGlass的組件完成,如果具有相應的License則會將相應的運行結果包含在報表中。報表包括datasheet?和dashboard?。

?????????在GUI界面下打開shell命令窗口,輸入如下命令生成報表:

write_aggregate_report datasheetwrite_aggregate_report dashboard????????生成的報表可以用瀏覽器打開,下面兩張圖為報表示例:

學習筆記整理系列三)

:線程池+并發編程+分布式設計+中間件)