提示:文章寫完后,目錄可以自動生成,如何生成可參考右邊的幫助文檔

文章目錄

- 前言

- 一、數字時鐘是什么?

- 二、EDA里面數碼管的顯示

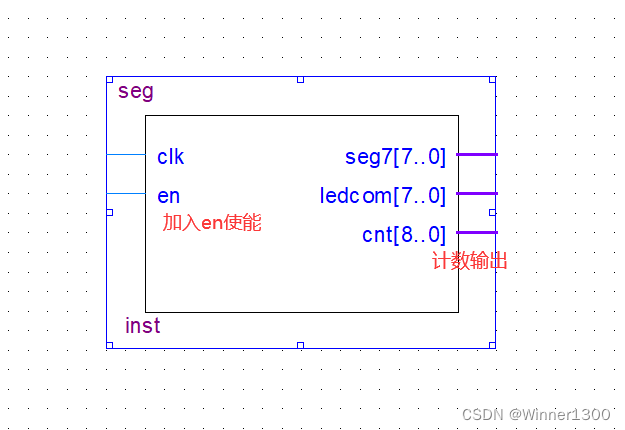

- 1.元件模型

- 2.參考程序

- 3. 實驗仿真波形

- 4.實驗現象

- 5. 仿真問題

- 三、顯示時鐘

- 1. 時鐘電路模塊

- 2.參考程序

- 3.仿真波形

- 4.實驗效果

- 總結

前言

提示:這里可以添加本文要記錄的大概內容:

前面學習了基本的數字芯片邏輯編程,學會了計數器等,這次來一個做一個綜合應用。數字時鐘,采用數碼管顯示時分秒。

提示:以下是本篇文章正文內容,下面案例可供參考

一、數字時鐘是什么?

數字時鐘是一種以數字顯示取代模擬表盤的鐘表,它能夠以數字的形式顯示當前的時間,并且可以同時顯示時、分、秒。此外,它通常具有對時、分、秒進行準確校準的功能。

示例:能用數碼管顯示 時分秒的時鐘

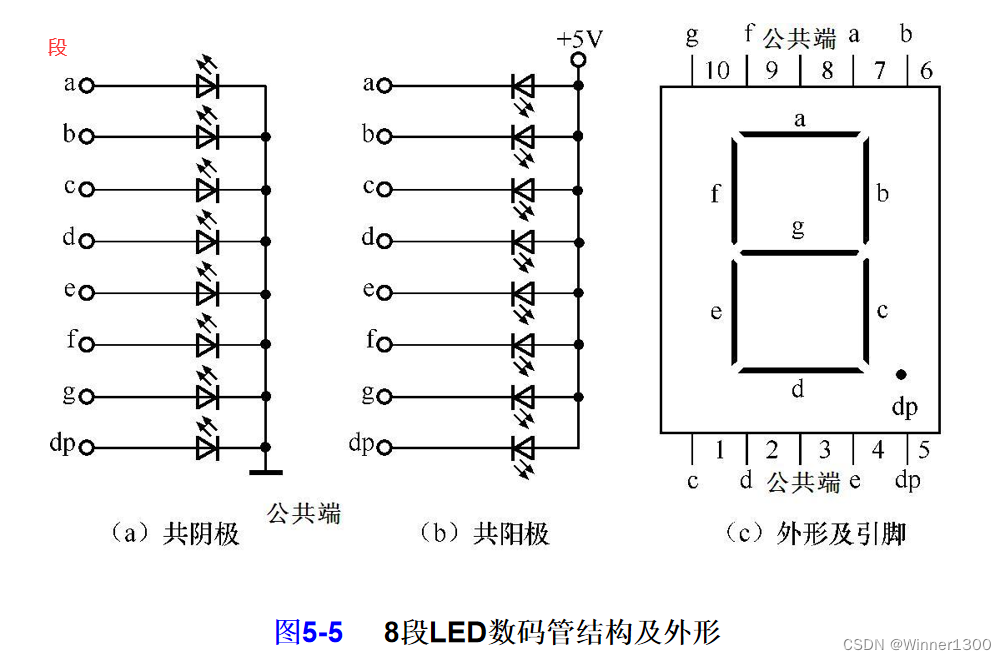

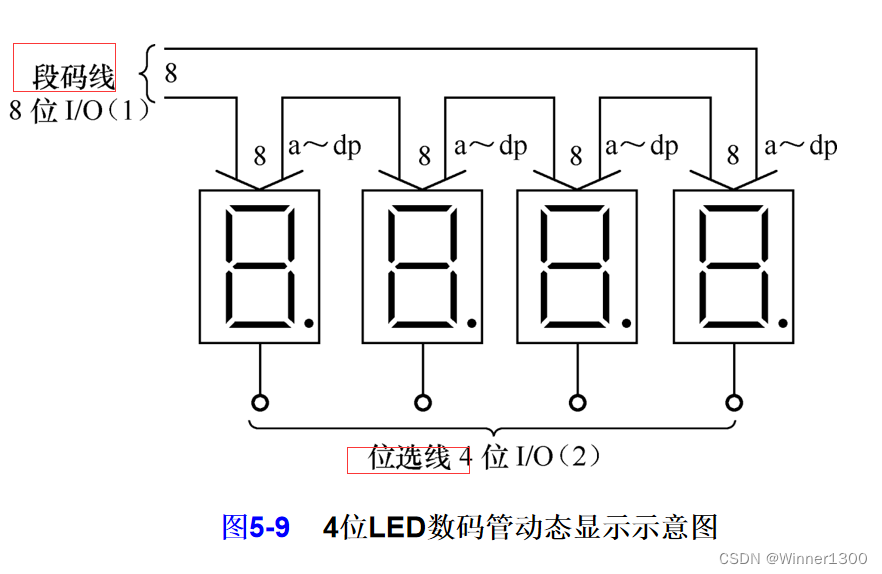

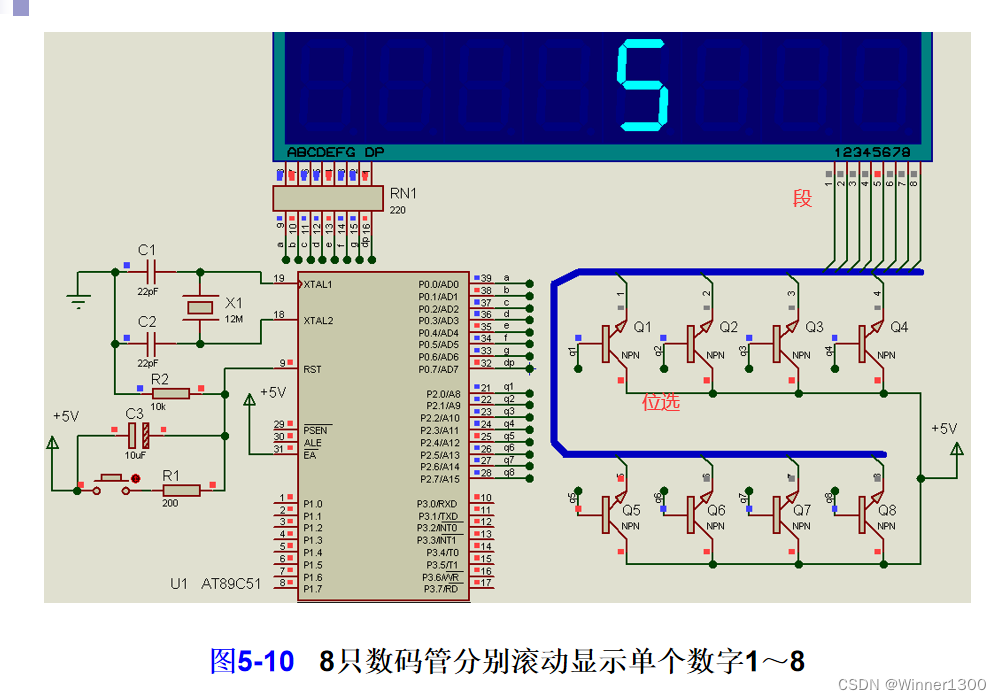

二、EDA里面數碼管的顯示

目標:動態數碼管顯示: 12345678

時間顯示的狀態效:”12.20.30 12-20.30 12-20-30

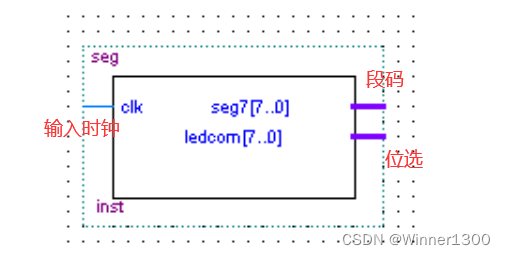

1.元件模型

代碼如下(示例):

2.參考程序

代碼如下(示例):

module seg(clk,seg7,ledcom);

input clk; // 假設系統提供的時鐘 50Mhz

output[7:0] seg7; //段

output[7:0] ledcom; //位選

reg[7:0] seg7; //alway 里面賦值要用reg數據

reg[20:0] cnt;

reg[7:0] ledcom;

always@(posedge clk)

begin if(cnt==21'b1 1111 1111 1111 1111 1111) // 2的22減一cnt<=0; else cnt<=cnt+1;

end

always@(cnt) //給位選

begin case(cnt[16:14]) // 14 15 16 000 ->111 前面13為 滿進位3'b000:ledcom<=8'b00000001;//0 只有一個位選為1 只有第一位數碼管選中并顯示3'b001:ledcom<=8'b00000010;//1 3'b010:ledcom<=8'b00000100;//2 3'b011:ledcom<=8'b00001000;//3 3'b100:ledcom<=8'b00010000;//0 3'b101:ledcom<=8'b00100000;//1 3'b110:ledcom<=8'b01000000;//2 3'b111:ledcom<=8'b10000000;//3 endcase

end

always@(cnt) //段碼

begin case(cnt[16:14]) 3'b000:seg7<=8'b00000111;//0 同時給到段碼 ,保證只有 第一個數碼管亮 3'b001:seg7<=8'b11011011;//1 3'b010:seg7<=8'b11001111;//23'b011:seg7<=8'b10100111;//3 3'b100:seg7<=8'b11101101;//0 3'b101:seg7<=8'b11111101;//1 3'b110:seg7<=8'b01000111;//2 3'b111:seg7<=8'b11111111;//3 endcase

end

endmodule

為了仿真改小了參數

module seg(clk,seg7,ledcom,cnt,en);

input en;

input clk; // 假設系統提供的時鐘 50Mhz

output[7:0] seg7; //段

output[7:0] ledcom; //位選

reg[7:0] seg7; //alway 里面賦值要用reg數據

output reg[8:0] cnt;

reg[7:0] ledcom;

always@(posedge clk)

begin if(!en)cnt<=0;elseif(cnt==8'b111111111) // 2的22減一cnt<=0; else cnt<=cnt+1;

end

always@(cnt) //給位選

begin case(cnt[7:5]) // 14 15 16 000 ->111 前面13為 滿進位3'b000:ledcom<=8'b00000001;//0 只有一個位選為1 只有第一位數碼管選中并顯示3'b001:ledcom<=8'b00000010;//1 3'b010:ledcom<=8'b00000100;//2 3'b011:ledcom<=8'b00001000;//3 3'b100:ledcom<=8'b00010000;//0 3'b101:ledcom<=8'b00100000;//1 3'b110:ledcom<=8'b01000000;//2 3'b111:ledcom<=8'b10000000;//3 default:ledcom<=8'b10000000;endcase

end

always@(cnt) //段碼

begin case(cnt[7:5]) 3'b000:seg7<=8'b00000111;//0 同時給到段碼 ,保證只有 第一個數碼管亮 3'b001:seg7<=8'b11011011;//1 3'b010:seg7<=8'b11001111;//23'b011:seg7<=8'b10100111;//3 3'b100:seg7<=8'b11101101;//0 3'b101:seg7<=8'b11111101;//1 3'b110:seg7<=8'b01000111;//2 3'b111:seg7<=8'b11111111;//3 default:seg7<=8'b11111111;endcase

end

endmodule測試文件

`timescale 1 ps/ 1 ps

module seg_tb3();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

reg en;

// wires

wire [8:0] cnt;

wire [7:0] ledcom;

wire [7:0] seg7;// assign statements (if any)

seg i1 (

// port map - connection between master ports and signals/registers .clk(clk),.cnt(cnt),.en(en),.ledcom(ledcom),.seg7(seg7)

);

initial

begin

// code that executes only once

// insert code here --> begin // --> end

#10 clk= 0;

#100 en=0;

#10 en=1;

$display("Running testbench");

end always #10 clk=~clk;

always

// optional sensitivity list

// @(event1 or event2 or .... eventn)

begin

// code executes for every event on sensitivity list

// insert code here --> begin @eachvec;

// --> end

end

endmodule實際仿真測試元件圖

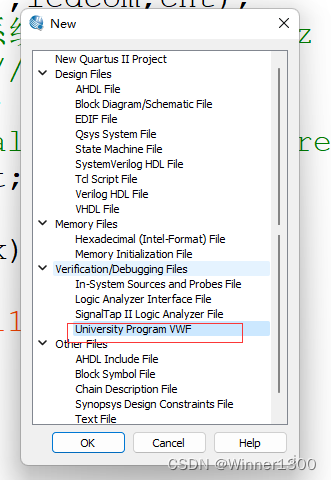

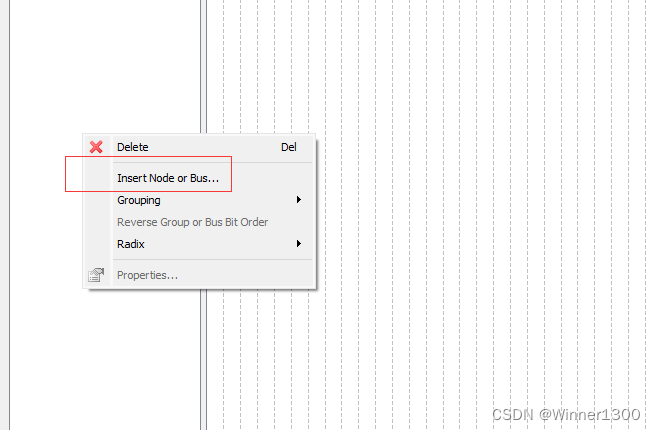

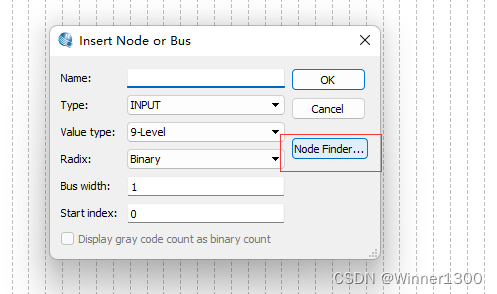

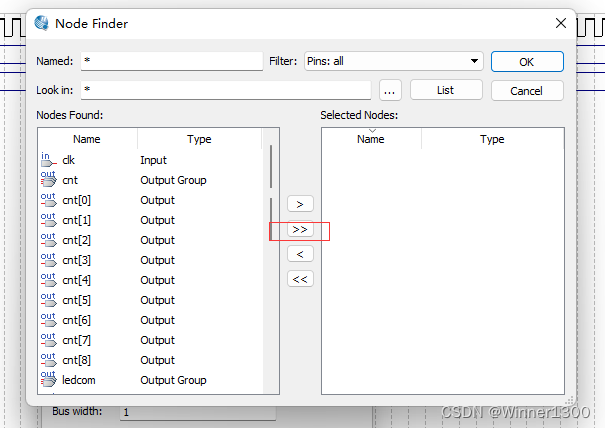

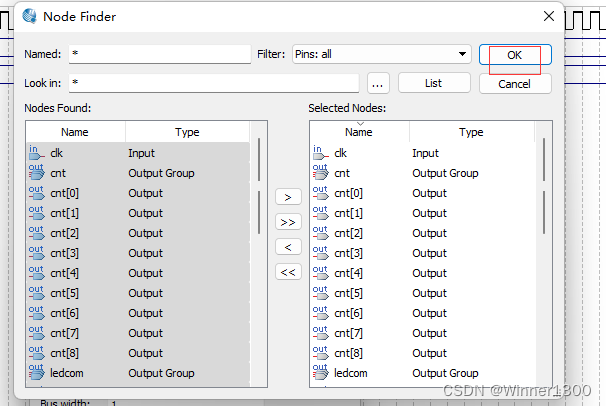

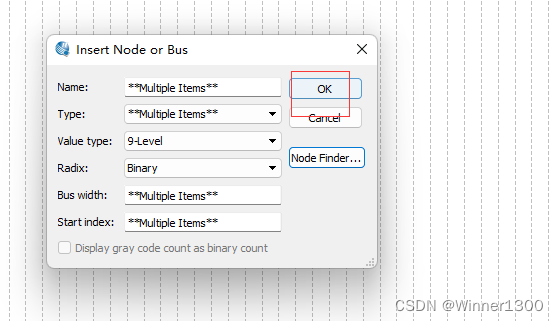

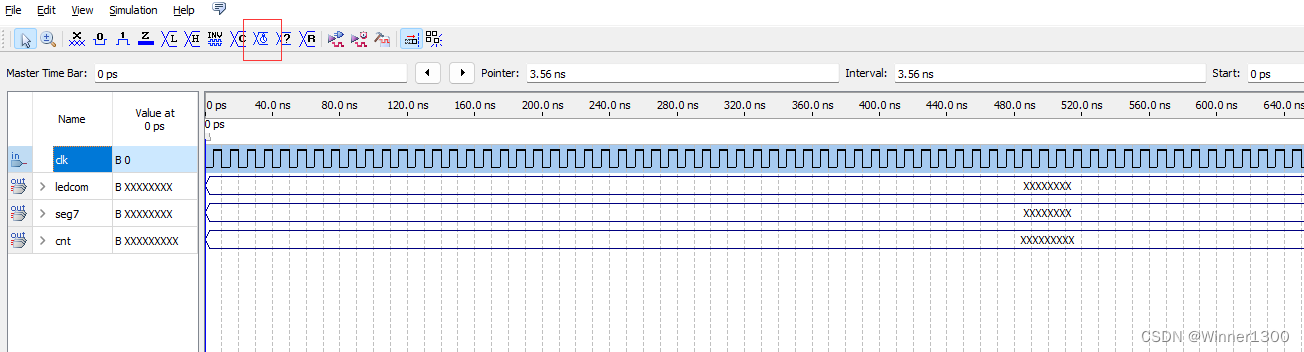

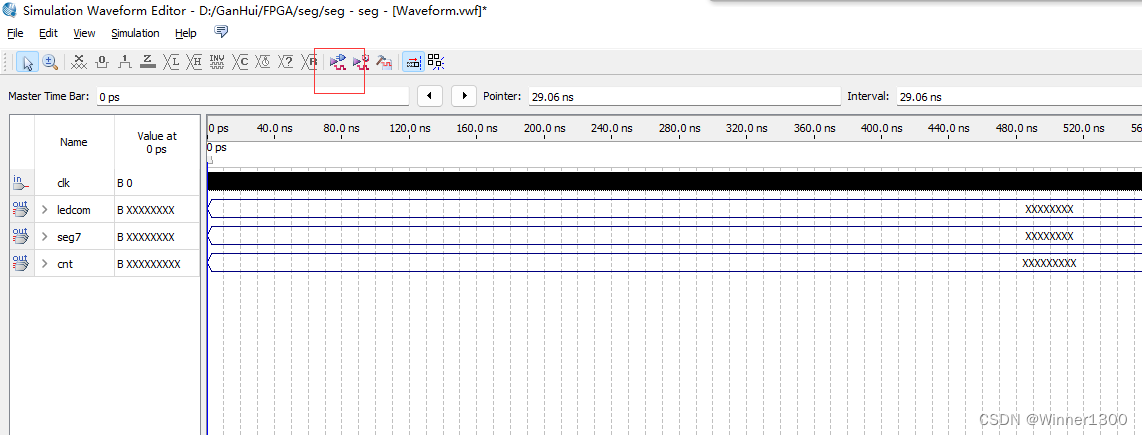

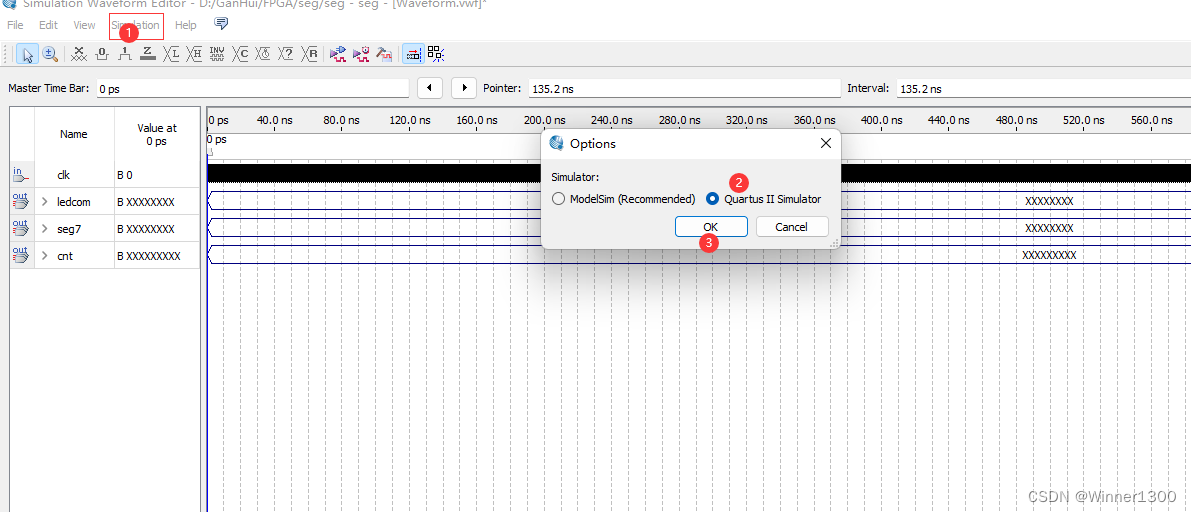

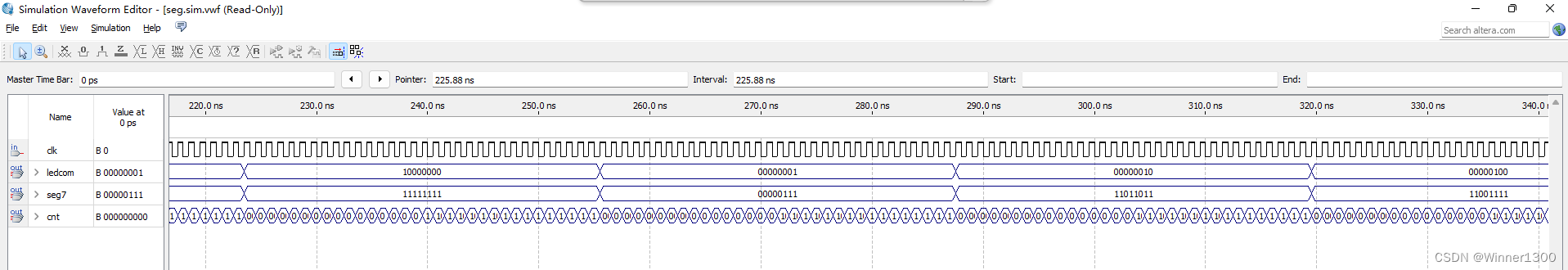

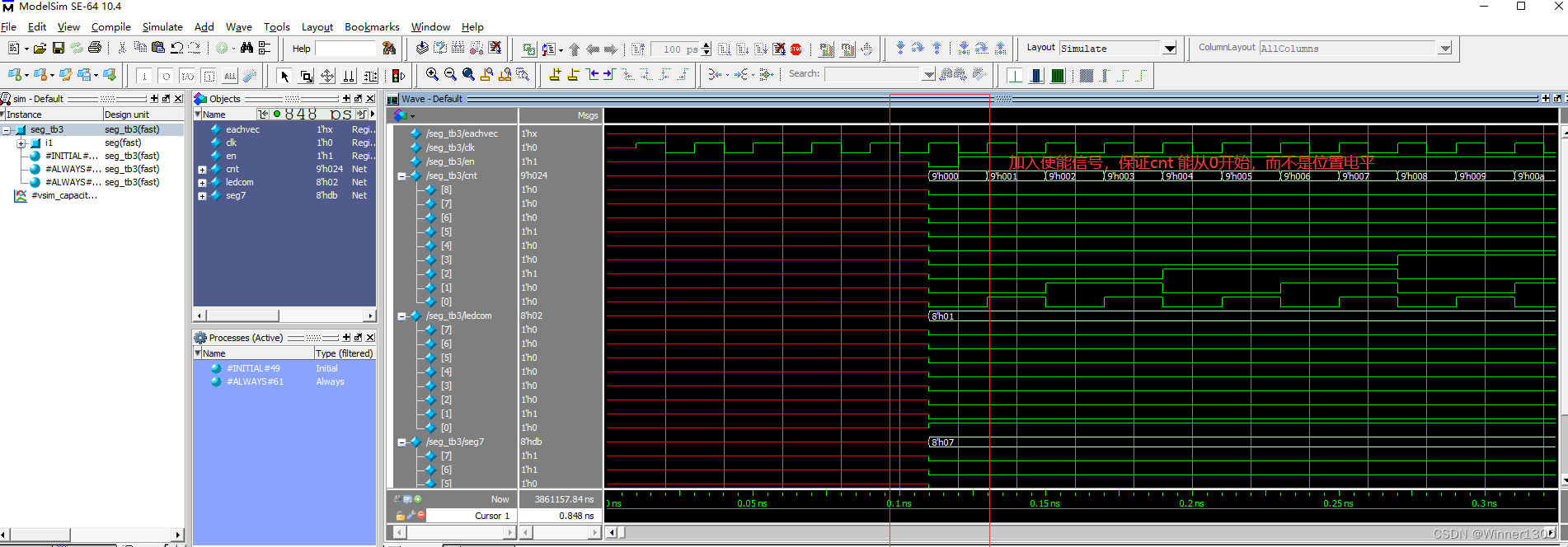

3. 實驗仿真波形

4.實驗現象

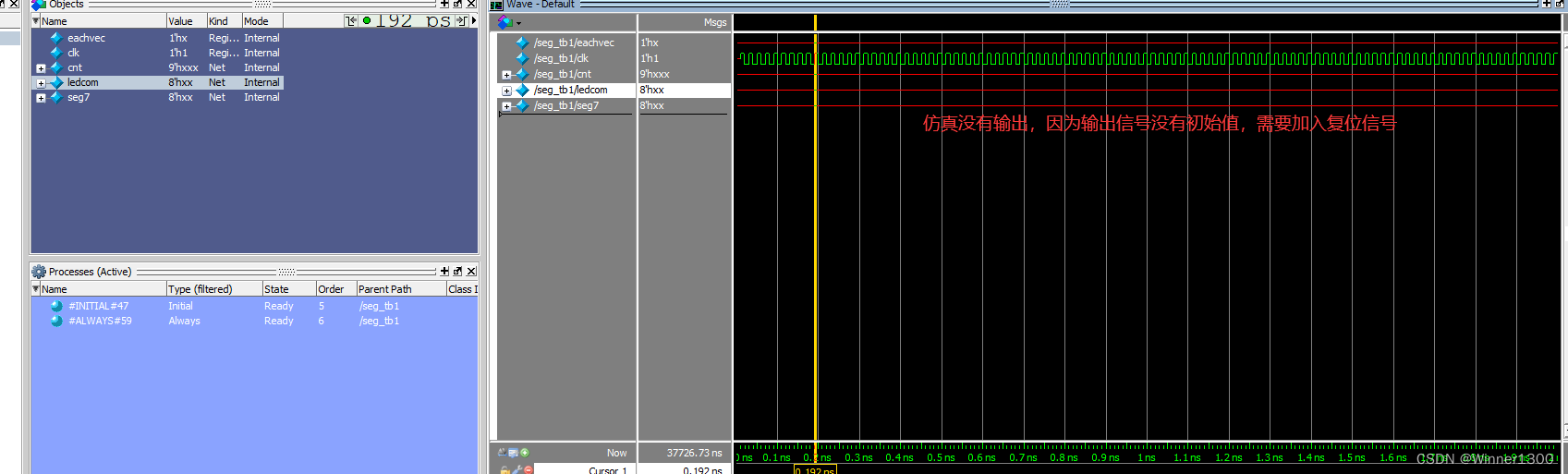

5. 仿真問題

三、顯示時鐘

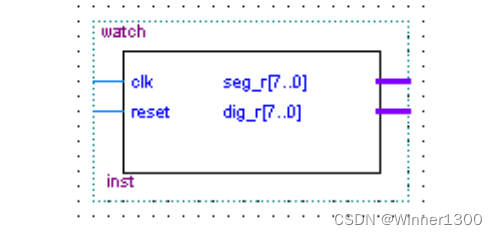

1. 時鐘電路模塊

2.參考程序

module watch(clk,reset,seg_r,dig_r);

input clk;

input reset;

output[7:0] seg_r;

output[7:0] dig_r;

reg[25:0] count;

reg[15:0] hour;

reg sec;

reg[4:0] disp_dat;

reg[7:0] seg_r;

reg[7:0] dig_r;

always @(posedge clk)

begin count = count + 1'b1; if(count == 26'd25000000)begin count = 26'd0; sec = ~sec; end

end

always @(posedge sec)

begin

if(reset==0) hour[15:0]=0; else begin hour[3:0] = hour[3:0]+1'b1; if(hour[3:0] == 4'ha) begin hour[3:0] = 4'h0; hour[7:4] = hour[7:4]+1'b1; if(hour[7:4] == 4'h6) begin hour[7:4] = 4'h0; hour[11:8] = hour[11:8] + 1'b1; if(hour[11:8] ==4'ha) begin hour[11:8] = 4'h0; hour[15:12] = hour[15:12] + 1'b1; if(hour[15:12] == 4'h6) hour[15:12] =4'h0; end end end endend

always @(posedge clk)

begin case(count[17:15]) 3'd0:disp_dat = hour[3:0]; 3'd1:disp_dat = hour[7:4]; 3'd3:disp_dat = hour[11:8]; 3'd4:disp_dat = hour[15:12]; endcase case(count[17:15]) 3'd0:dig_r = 8'b10000000; 3'd1:dig_r = 8'b01000000; 3'd2:dig_r = 8'b00000000; 3'd3:dig_r = 8'b00010000; 3'd4:dig_r = 8'b00001000; 3'd5:dig_r = 8'b00000000; 3'd6:dig_r = 8'b00000000; 3'd7:dig_r = 8'b00000000; endcase

end

always @(posedge clk)

begin case(disp_dat)

0:seg_r=8'b01111111; 1:seg_r=8'b00000111; 2:seg_r=8'b11011011; 3:seg_r=8'b11001111; 4:seg_r=8'b10100111; 5:seg_r=8'b11101101;6:seg_r=8'b11111101; 7:seg_r=8'b01000111; 8:seg_r=8'b11111111; 9:seg_r=8'b11101111;

default:seg_r = 8'hff; endcase

end

endmodule

3.仿真波形

4.實驗效果

總結

提示:這里對文章進行總結:

)

)

存儲非負值)

———http和https詳細解析)

、模板案例)

猜想)