目錄

- 1、前言

- 免責聲明

- 2、相關方案推薦

- FPGA圖像處理方案

- FPGA圖像縮放方案

- 自己寫的HLS圖像縮放方案

- 3、設計思路詳解

- Video Processing Subsystem 介紹

- 4、工程代碼詳解

- PL 端 FPGA 邏輯設計

- PS 端 SDK 軟件設計

- 5、工程移植說明

- vivado版本不一致處理

- FPGA型號不一致處理

- 其他注意事項

- 6、上板調試驗證并演示

- 準備工作

- 輸出靜態演示

- 7、福利:工程源碼獲取

Zynq-7000系列FPGA使用 Video Processing Subsystem 實現圖像縮放,提供工程源碼和技術支持

1、前言

沒玩過圖像縮放都不好意思說自己玩兒過FPGA,這是CSDN某大佬說過的一句話,鄙人深信不疑。。。

目前市面上主流的FPGA圖像縮放方案如下:

1:Xilinx的HLS方案,該方案簡單,易于實現,但只能用于Xilinx自家的FPGA;

2:非純Verilog方案,大部分代碼使用Verilog實現,但中間的fifo或ram等使用了IP,導致移植性變差,難以在Xilinx、Altera和國產FPGA之間自由移植;

3:純Verilog方案;

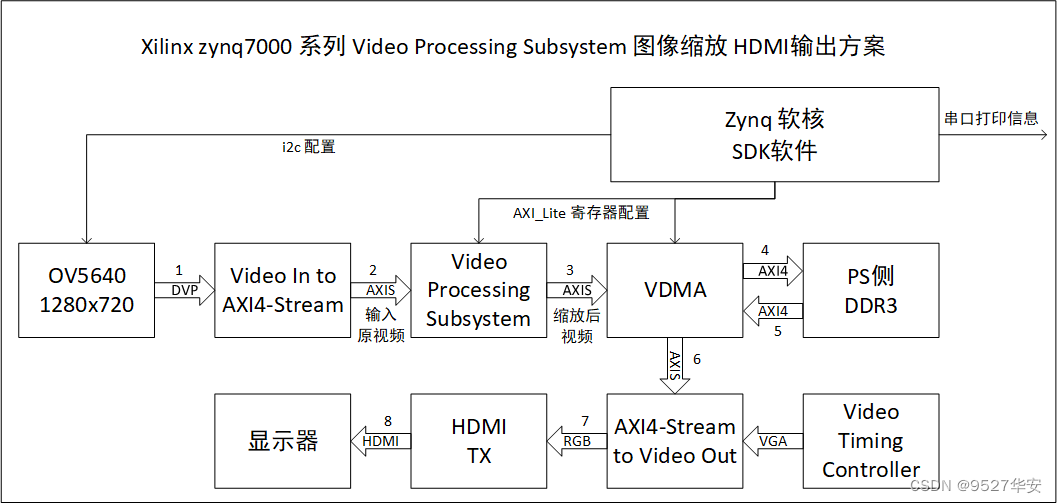

本文使用Xilinx Zynq7000系列FPGA Zynq7020實現Video Processing Subsystem圖像縮放,輸入視頻源采用OV5640攝像頭模組;FPGA采集OV5640攝像頭視頻DVP轉RGB888,調用Zynq軟核的片內i2c控制器將OV5640配置為1280x720@30Hz分辨率;然后調用Xilinx官方的Video In to AXI4-Stream IP核將RGB視頻流轉換為AXI4-Stream視頻流;然后調用Xilinx官方的Video Processing Subsystem IP核將輸入視頻進行任意尺寸圖像縮放操作,該操作通過Zynq軟核SDK軟件配置,其本質為通過AXI_Lite 做寄存器配置;然后調用Xilinx官方的VDMA IP將視頻做PS側DDR3的視頻緩存操作,調用Zynq將VDMA配置為三幀緩存,其本質為通過AXI_Lite 做寄存器配置;然后調用Xilinx官方的Video Timing Controller IP和AXI4-Stream to Video Out IP將AXI4-Stream視頻流轉換為RGB視頻流;然后添加自定義的HDMI發送IP將RGB視頻轉換為TMDS的差分視頻送顯示器顯示;提供一套vivado2019.1版本的工程源碼和技術支持;

本博客詳細描述了Zynq-7000系列FPGA使用 Video Processing Subsystem 實現圖像縮放的設計方案,工程代碼可綜合編譯上板調試,可直接項目移植,適用于在校學生、研究生項目開發,也適用于在職工程師做學習提升,可應用于醫療、軍工等行業的高速接口或圖像處理領域;整個工程調用Zynq軟核做IP的配置,Zynq的配置在SDK里以C語言軟件代碼的形式運行,所以整個工程包括FPGA邏輯設計和SDK軟件設計兩部分,需要具備FPGA和嵌入式C語言的綜合能力,不適合初學者或者小白;

提供完整的、跑通的工程源碼和技術支持;

工程源碼和技術支持的獲取方式放在了文章末尾,請耐心看到最后;

免責聲明

本工程及其源碼即有自己寫的一部分,也有網絡公開渠道獲取的一部分(包括CSDN、Xilinx官網、Altera官網等等),若大佬們覺得有所冒犯,請私信批評教育;基于此,本工程及其源碼僅限于讀者或粉絲個人學習和研究,禁止用于商業用途,若由于讀者或粉絲自身原因用于商業用途所導致的法律問題,與本博客及博主無關,請謹慎使用。。。

2、相關方案推薦

FPGA圖像處理方案

我的主頁目前有FPGA圖像處理專欄,改專欄收錄了我目前手里已有的FPGA圖像處理方案,包括圖像縮放、圖像識別、圖像拼接、圖像融合、圖像去霧、圖像疊加、圖像旋轉、圖像增強、圖像字符疊加等等;以下是專欄地址:

點擊直接前往

FPGA圖像縮放方案

我的主頁目前有FPGA圖像縮放專欄,改專欄收錄了我目前手里已有的FPGA圖像縮放方案,從實現方式分類有基于HSL實現的圖像縮放、基于純verilog代碼實現的圖像縮放;從應用上分為單路視頻圖像縮放、多路視頻圖像縮放、多路視頻圖像縮放拼接;從輸入視頻分類可分為OV5640攝像頭視頻縮放、SDI視頻縮放、MIPI視頻縮放等等;以下是專欄地址:

點擊直接前往

自己寫的HLS圖像縮放方案

之前寫過一篇自己寫的HLS圖像縮放的博客,該方案與官方的Video Processing Subsystem區別在于手寫的看得到;以下是博客地址:

點擊直接前往

3、設計思路詳解

本文使用Xilinx Zynq7000系列FPGA Zynq7020實現Video Processing Subsystem圖像縮放,輸入視頻源采用OV5640攝像頭模組;FPGA采集OV5640攝像頭視頻DVP轉RGB888,調用Zynq軟核的片內i2c控制器將OV5640配置為1280x720@30Hz分辨率;然后調用Xilinx官方的Video In to AXI4-Stream IP核將RGB視頻流轉換為AXI4-Stream視頻流;然后調用Xilinx官方的Video Processing Subsystem IP核將輸入視頻進行任意尺寸圖像縮放操作,該操作通過Zynq軟核SDK軟件配置,其本質為通過AXI_Lite 做寄存器配置;然后調用Xilinx官方的VDMA IP將視頻做PS側DDR3的視頻緩存操作,調用Zynq將VDMA配置為三幀緩存,其本質為通過AXI_Lite 做寄存器配置;然后調用Xilinx官方的Video Timing Controller IP和AXI4-Stream to Video Out IP將AXI4-Stream視頻流轉換為RGB視頻流;然后添加自定義的HDMI發送IP將RGB視頻轉換為TMDS的差分視頻送顯示器顯示;提供一套vivado2019.1版本的工程源碼和技術支持;

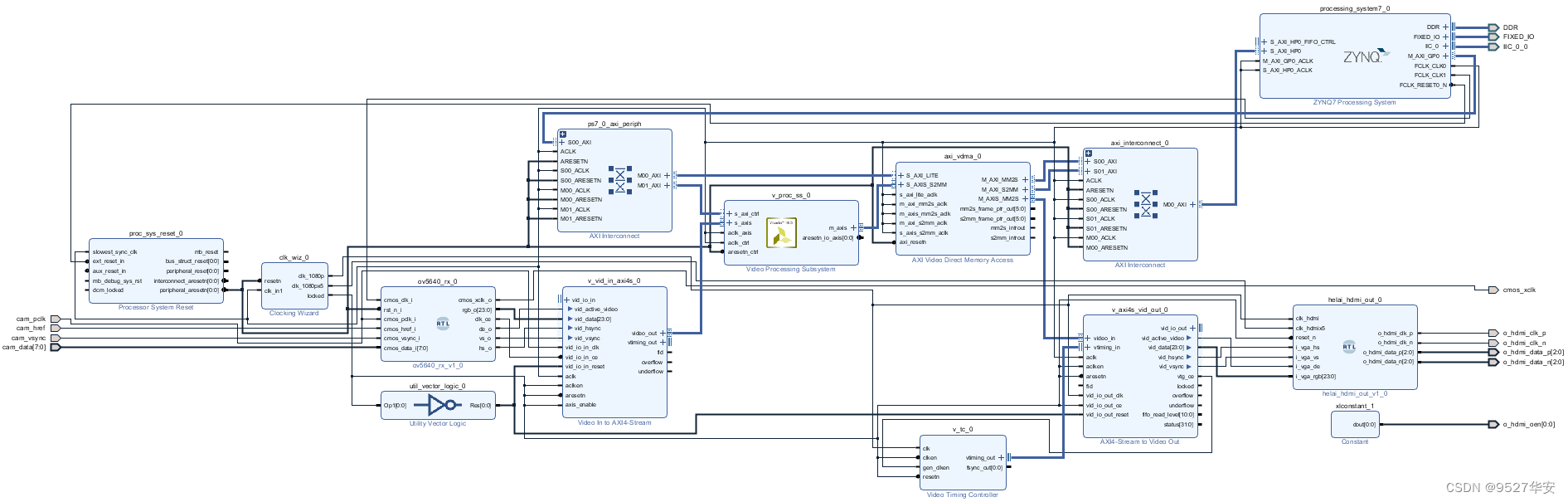

工程源碼設計框圖如下:

框圖解釋:箭頭表示數據流向,箭頭內文字表示數據格式,箭頭外數字表示數據柳巷的步驟;

Video Processing Subsystem 介紹

由于工程所用到的IP都是常用IP,所以這里重點介紹一下Video Processing Subsystem;

Video Processing Subsystem有縮放、去隔行、顏色空間轉換等功能,這里僅使用圖像縮放功能;其特點如下:

適用于Xilinx所有系列的FPGA器件;

支持最大分辨率:8K,即可以處理高達8K的視頻;

輸入視頻格式:AXI4-Stream;

輸出視頻格式:AXI4-Stream;

需要SDK軟件配置,其本質為通過AXI_Lite 做寄存器配置;

提供自定義的配置API,通過調用該庫函數即可輕松使用,具體參考SDK代碼;

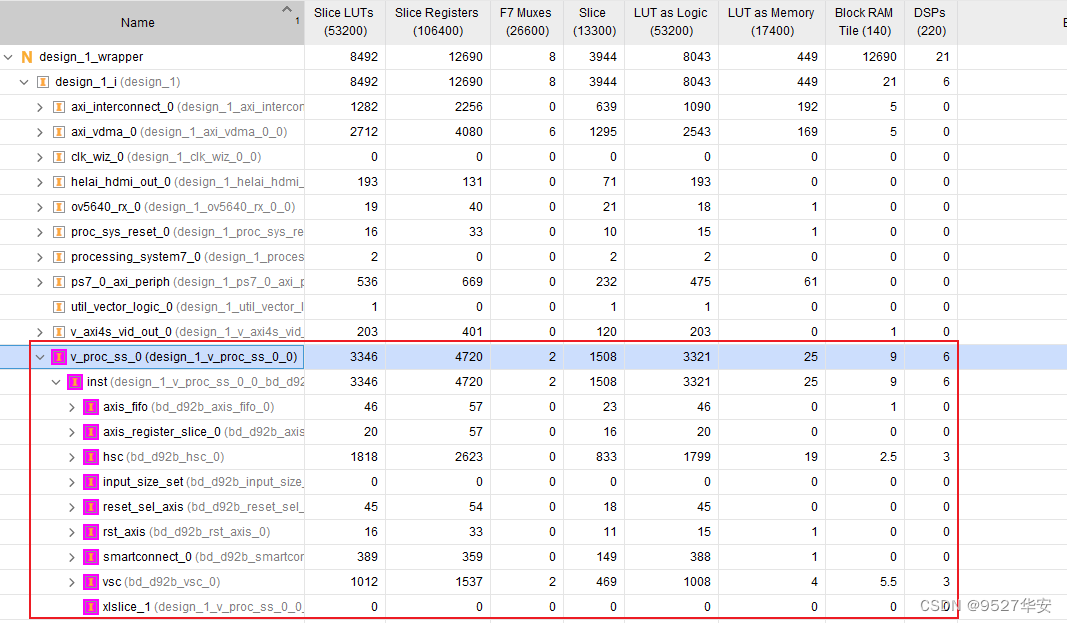

模塊占用的FPGA邏輯資源更小,相比于自己寫的HLS圖像縮放而言,官方的Video Processing Subsystem資源占用大約減小30%左右,且更高效:

Video Processing Subsystem邏輯資源如下,請謹慎評估你的FPGA資源情況;

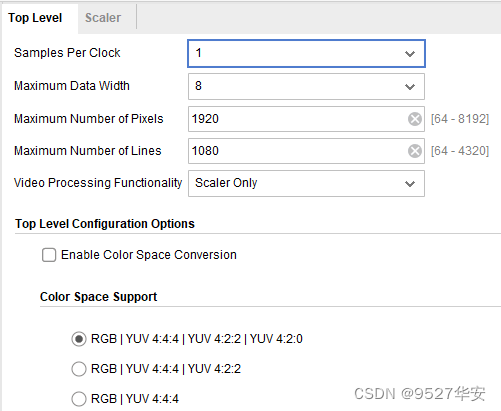

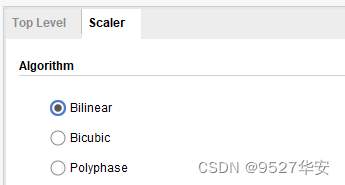

Video Processing Subsystem IP配置如下:這里配置為雙線性插值圖像縮放算法;

4、工程代碼詳解

PL 端 FPGA 邏輯設計

開發板FPGA型號:Xilinx–Zynq7020–xc7z020clg400-2;

開發環境:Vivado2019.1;

輸入:OV5640攝像頭,分辨率1280x720p;

輸出:HDMI,1080P分辨率下的有效區域顯示;

工程作用:Zynq-7000系列FPGA使用Video Processing Subsystem實現圖像縮放, HDMI 輸出;

工程BD如下:

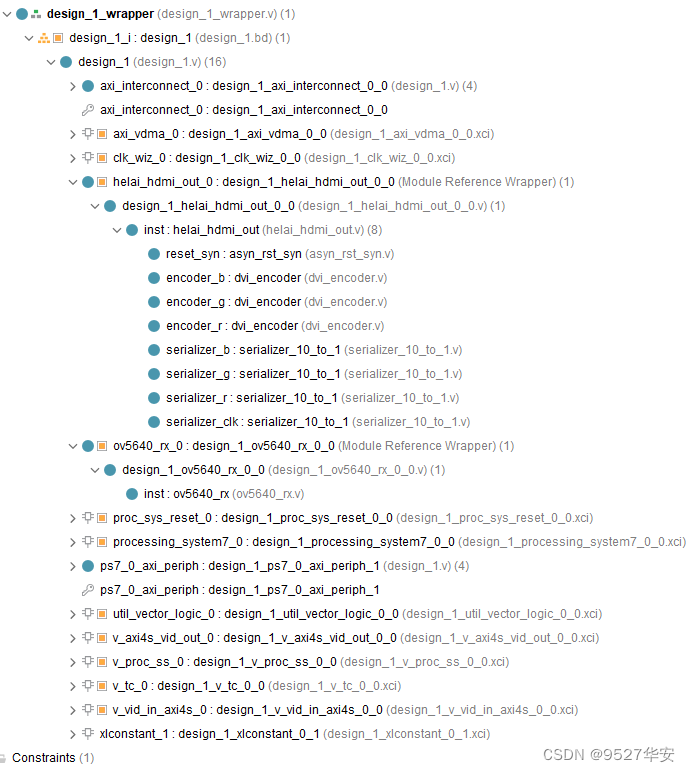

工程代碼架構如下:

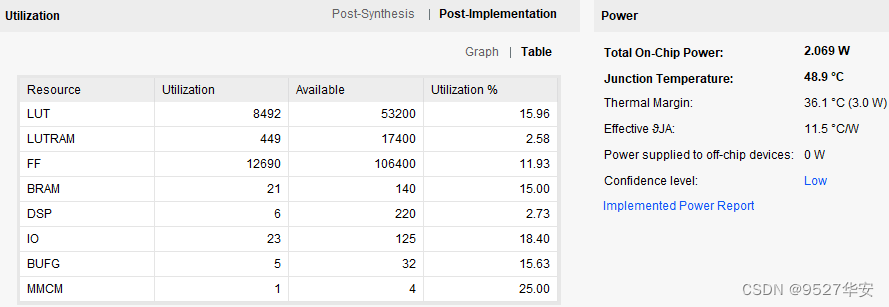

工程的資源消耗和功耗如下:

PS 端 SDK 軟件設計

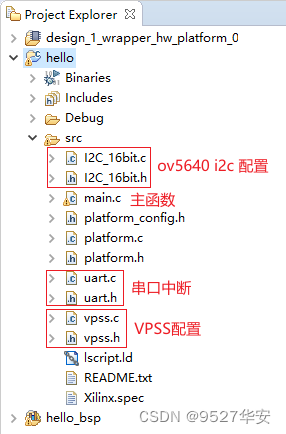

PS 端 SDK 軟件工程代碼架構如下:

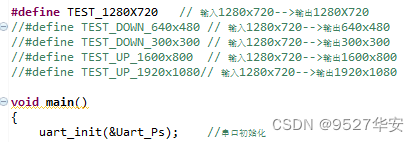

主函數通過如下的五個宏定義設計了五種不同的圖像縮放方案:

ov5640輸入分辨率1280x720,HDMI輸出分辨率1280x720;

ov5640輸入分辨率1280x720,HDMI輸出分辨率640x480;

ov5640輸入分辨率1280x720,HDMI輸出分辨率300x300;

ov5640輸入分辨率1280x720,HDMI輸出分辨率1600x800;

ov5640輸入分辨率1280x720,HDMI輸出分辨率1920x1080;

主函數進行相應的圖像縮放操作,并打印相關信息,代碼如下:

5、工程移植說明

vivado版本不一致處理

1:如果你的vivado版本與本工程vivado版本一致,則直接打開工程;

2:如果你的vivado版本低于本工程vivado版本,則需要打開工程后,點擊文件–>另存為;但此方法并不保險,最保險的方法是將你的vivado版本升級到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解決如下:

打開工程后會發現IP都被鎖住了,如下:

此時需要升級IP,操作如下:

FPGA型號不一致處理

如果你的FPGA型號與我的不一致,則需要更改FPGA型號,操作如下:

更改FPGA型號后還需要升級IP,升級IP的方法前面已經講述了;

其他注意事項

1:由于每個板子的DDR不一定完全一樣,所以MIG IP需要根據你自己的原理圖進行配置,甚至可以直接刪掉我這里原工程的MIG并重新添加IP,重新配置;

2:根據你自己的原理圖修改引腳約束,在xdc文件中修改即可;

3:純FPGA移植到Zynq需要在工程中添加zynq軟核;

6、上板調試驗證并演示

準備工作

Zynq7000系列開發板;

OV5640攝像頭;

HDMI顯示器或者LCD顯示屏,我用到的LCD顯示屏為4.3寸分辨率800x480;

輸出靜態演示

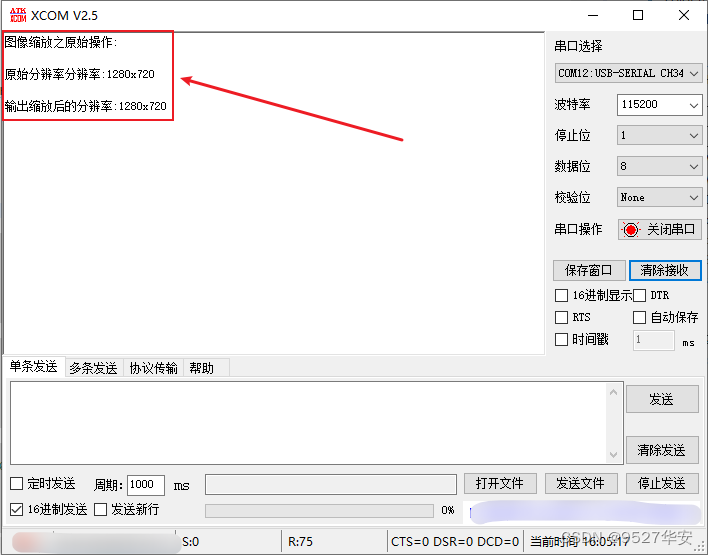

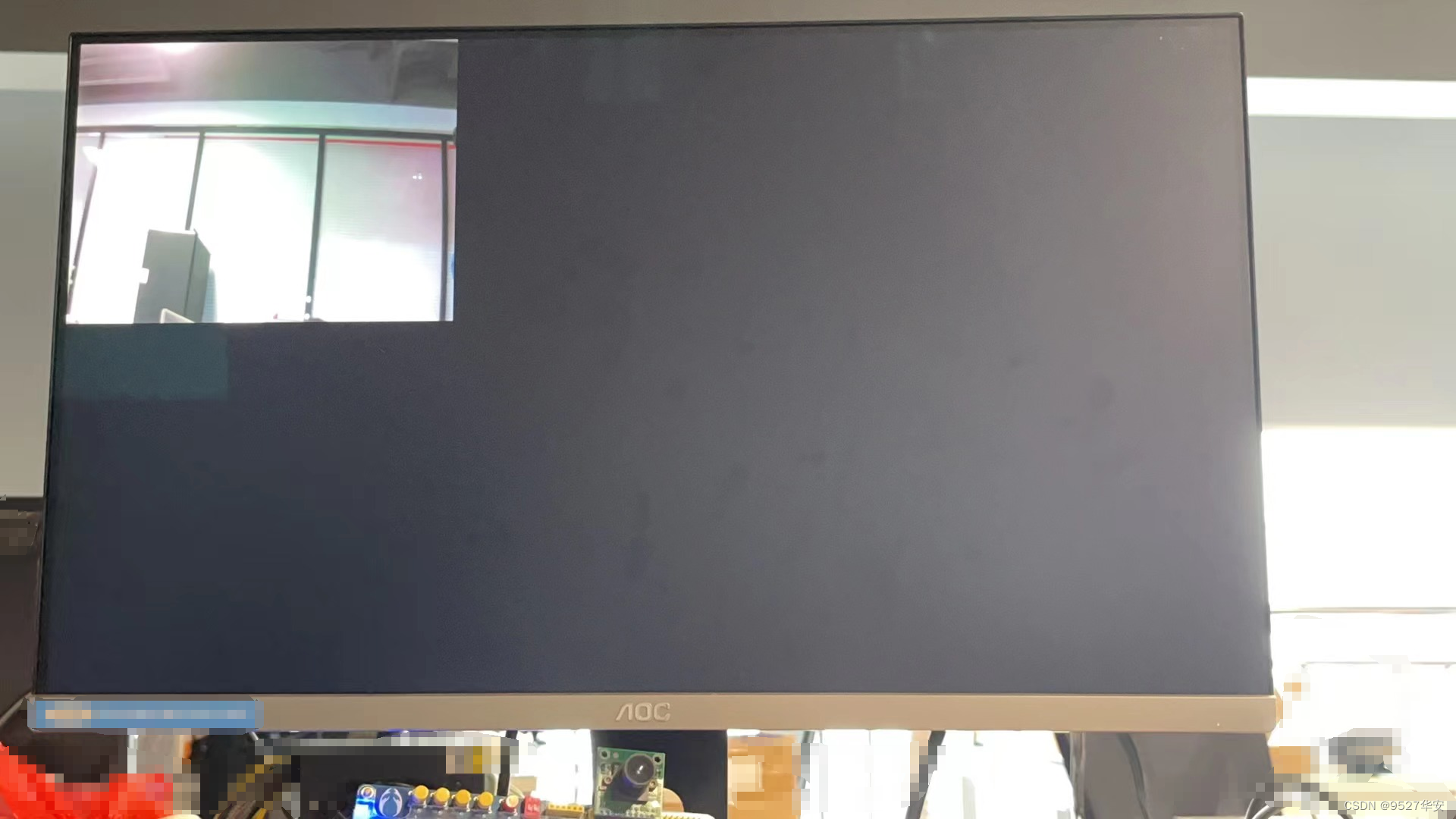

ov5640輸入分辨率1280x720,HDMI輸出分辨率1280x720;

HDMI顯示輸出和串口打印分別如下:

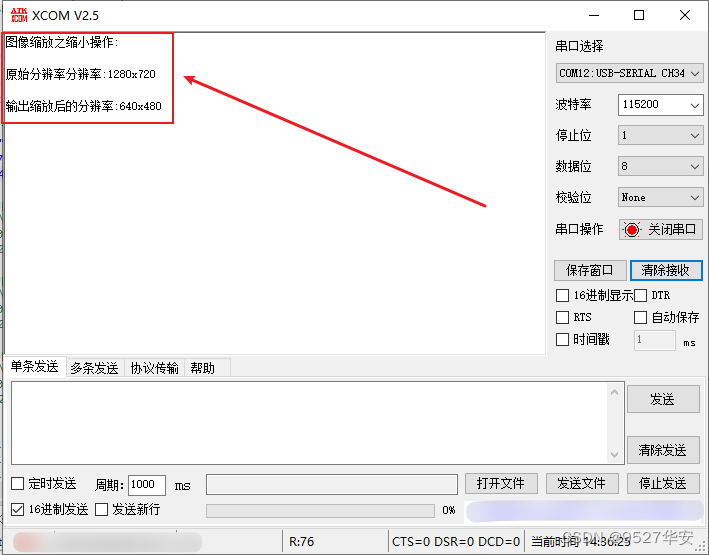

ov5640輸入分辨率1280x720,HDMI輸出分辨率640x480;

HDMI顯示輸出和串口打印分別如下:

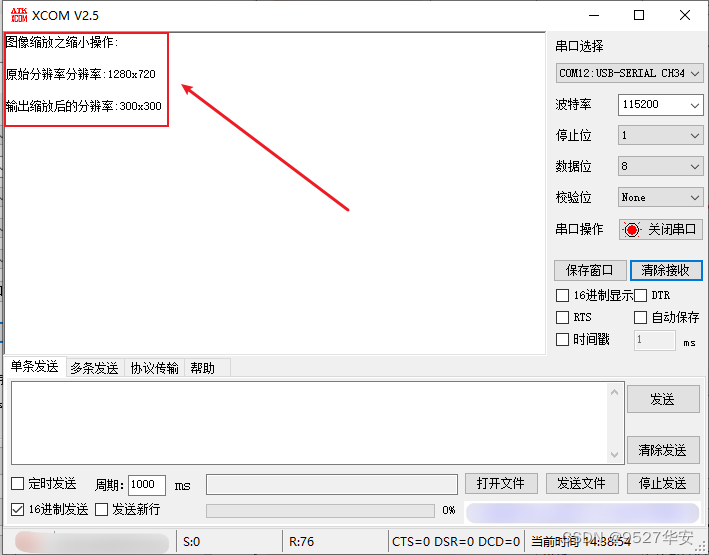

ov5640輸入分辨率1280x720,HDMI輸出分辨率300x300;

HDMI顯示輸出和串口打印分別如下:

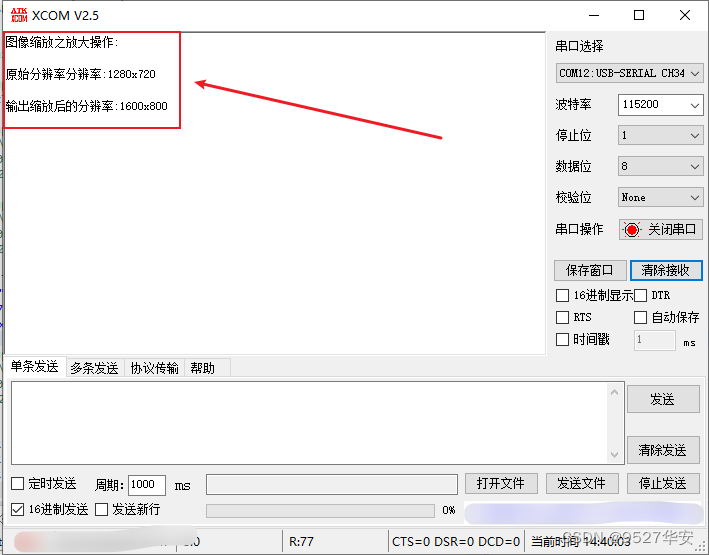

ov5640輸入分辨率1280x720,HDMI輸出分辨率1600x800;

HDMI顯示輸出和串口打印分別如下:

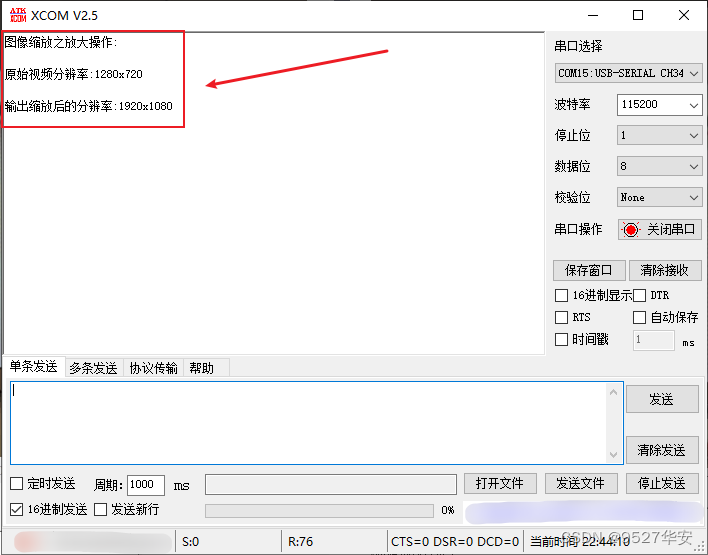

ov5640輸入分辨率1280x720,HDMI輸出分辨率1920x1080;

HDMI顯示輸出和串口打印分別如下:

7、福利:工程源碼獲取

福利:工程代碼的獲取

代碼太大,無法郵箱發送,以某度網盤鏈接方式發送,

資料獲取方式:私,或者文章末尾的V名片。

網盤資料如下:

)

:工作中的 Git 實踐)

)

,哈希(unordered_map)的練習)

)

![TC397 EB MCAL開發從0開始系列 之 [15.2] Fee配置 - QsBlock demo](http://pic.xiahunao.cn/TC397 EB MCAL開發從0開始系列 之 [15.2] Fee配置 - QsBlock demo)

)