PCB設計中避免電磁干擾(EMI)是一項涉及電路架構、布局布線、材料選擇及制造工藝的系統工程。本文從設計原理到工程實踐,系統闡述EMI產生機制及綜合抑制策略,覆蓋高頻信號控制、接地優化、屏蔽技術等核心維度,為高密度、高速PCB設計提供完整的EMI解決方案。

一、EMI產生機理與抑制原理

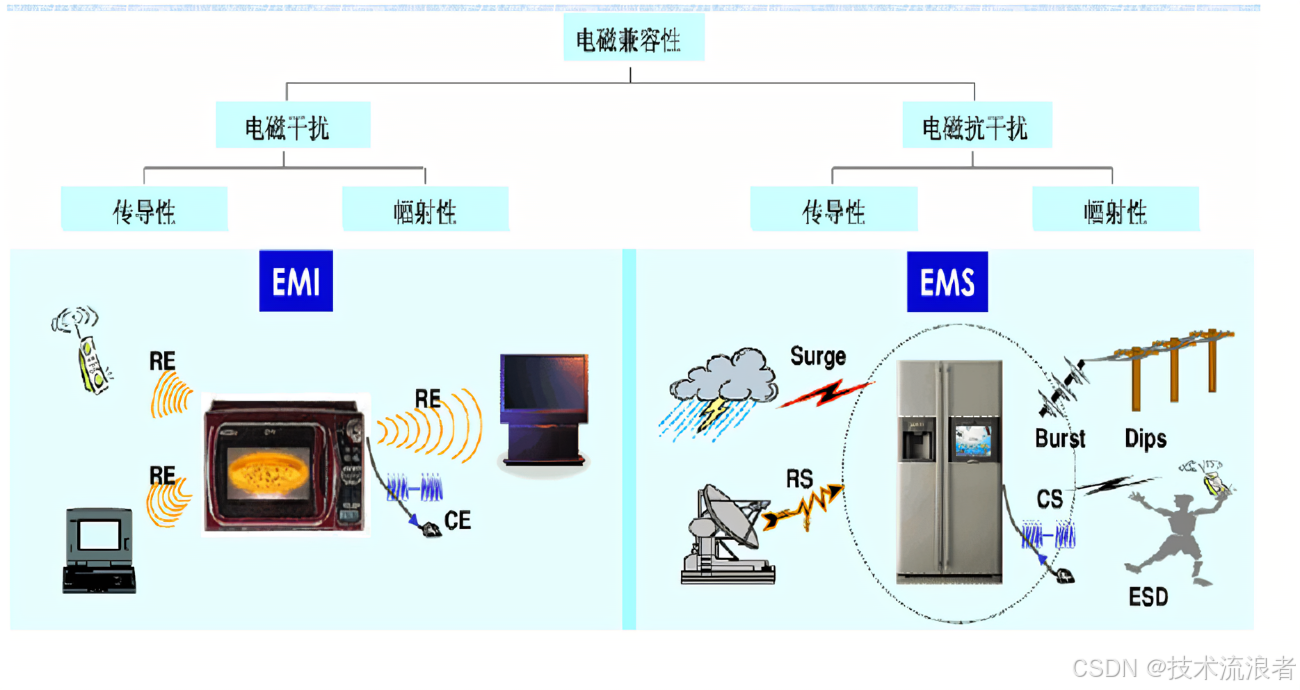

電磁干擾源于電流突變產生的電磁場耦合,主要包含傳導干擾(30Hz-30MHz)和輻射干擾(30MHz-GHz以上)。其形成需三個要素:干擾源、耦合路徑、敏感設備。抑制策略需從這三方面切入:

- 干擾源控制

降低高速信號上升時間(Tr),如使用Tr>1ns的驅動芯片可將fknee(最高EMI頻率)限制在350MHz以下。開關電源選用軟開關拓撲(如LLC)可將dv/dt降低60%以上。- 耦合路徑阻斷

傳輸線參數優化,差分對阻抗偏差控制在±5%以內,減少共模噪聲。采用帶狀線替代微帶線可降低輻射強度達10dB。- 敏感設備防護

高精度ADC前端增加共模扼流圈(CMC),抑制1MHz以上干擾信號達40dB。

二、分層堆疊設計與EMI抑制

層疊結構是EMI控制的物理基礎,典型八層板推薦結構:

| 層序 | 功能 | 材質要求 |

|---|---|---|

| 1 | 信號層 | 低粗糙度銅箔(Rz<2μm) |

| 2 | 地平面 | 1oz銅厚,完整無分割 |

| 3 | 信號層 | 玻纖效應補償材料 |

| 4 | 電源平面 | 多區域分割,去耦電容集中 |

| 5 | 信號層 | 帶防護帶的敏感信號 |

| 6 | 電源平面 | 混合壓合結構 |

| 7 | 地平面 | 多點過孔連接 |

| 8 | 信號層 | 表層鋪地網格 |

關鍵設計原則:

- 相鄰信號層走線正交布局,減小層間串擾

- 電源/地平面間距≤4mil,形成低阻抗供電網絡

- 高速信號優先布在內層,利用地平面屏蔽輻射

三、布局優化策略

1. 功能分區

- 數字/模擬隔離:通過開槽分割地平面,間距>20mm,跨區信號采用磁珠或電容濾波

- 高頻模塊集中:WiFi/BT模塊與CPU保持≥15mm間距,外圍增加屏蔽罩安裝焊盤

- 電源模塊布局:DC-DC轉換器靠近輸入端,輸入/輸出環路面積<5cm2

2. 時鐘電路處理

- 晶體振蕩器外殼多點接地,周圍布設接地過孔陣列(間距λ/10)

- 時鐘線長度匹配誤差<50mil,避免并行長度超過1000mil

- 時鐘驅動器采用源端串聯匹配(Rs=Z0-Zout)

四、走線關鍵技術與規范

1. 高速信號布線

- 阻抗控制:差分對采用邊緣耦合結構,線寬/間距比=2:1,參考平面間距誤差<5%

- 過孔優化:高速信號過孔反焊盤直徑=2倍孔徑,背鉆殘樁<8mil

- 蛇形繞線:振幅≤5W(W為線寬),間距≥3W,避免周期性結構引發諧振

2. 電源走線規范

- 主電源通道寬徑比≥1A/mm,分支采用星形拓撲

- 去耦電容布局遵循"先小后大"原則:0402封裝電容距引腳<100mil

- 電源平面分割避免形成狹長區域,防止腔體諧振

3. 特殊信號處理

- 射頻信號:采用共面波導(CPW)結構,兩側接地帶過孔間距<λ/8

- 復位信號:增加RC濾波(R=33Ω,C=10nF),走線遠離時鐘區域

- 接口信號:USB/HDMI等差分對長度偏差<5mil,距板邊≥3H(H為介質厚度)

五、接地系統設計

1. 混合接地策略

- 低頻電路(<1MHz):單點接地,星形拓撲

- 高頻電路(>10MHz):多點接地,過孔間距<λ/20

- 混合信號系統:采用"Hybrid Ground"結構,數模地通過磁珠連接

2. 地平面優化

- 避免地平面分割,必要分割時跨分割線布設跨接電容(100nF/1μF并聯)

- 地平面邊緣縮進20H規則(H為板層間距),減少邊緣輻射

- 關鍵IC下方設置局部地島,通過過孔陣列與主地連接

3. 接地過孔陣列

- 過孔間距計算公式:

(f_max單位GHz,d單位mm)- BGA封裝器件每四個信號過孔配一個地過孔

- 板邊設置接地屏蔽過孔帶,間距<λ/10

六、屏蔽與濾波技術

1. 電磁屏蔽

- 局部屏蔽:敏感模塊采用0.2mm厚鍍錫鋼罩,接地點間距≤5mm

- 電纜屏蔽:同軸線外層編織網360°端接,轉移阻抗<100mΩ/m

- 縫隙處理:屏蔽罩開窗長寬比<5:1,接觸面導電襯墊壓縮率30%

2. 濾波設計

- 電源入口濾波:π型濾波網絡(10μF+磁珠+0.1μF),截止頻率<1MHz

- 信號線濾波:

- 低頻:RC濾波(R=50Ω,C=100pF)

- 高頻:三端電容(接地引腳長度<1mm)

- 共模濾波:共模扼流圈阻抗>100Ω@100MHz,差模插損<0.5dB

七、先進材料與工藝

1. 基材選擇

- 高頻電路:Rogers RO4350B(εr=3.48,tanδ=0.0037@10GHz)

- 高速數字:MEGTRON6(Dk=3.7,Df=0.002@1GHz)

- 汽車電子:Isola FR408HR(Tg≥180℃,CAF電阻>500MΩ)

2. 銅箔處理

- 超低輪廓銅箔(HVLP):表面粗糙度Rz<2μm,降低趨膚效應損耗

- 表面涂覆:化學沉銀(0.1-0.3μm)或ENIG(3-5μm Ni,0.05-0.1μm Au)

3. 制造工藝

- 激光直接成像(LDI):線寬精度±3μm,阻抗控制偏差<±5%

- 等離子體除膠渣:孔壁粗糙度Ra<8μm,提升高頻信號完整性

八、仿真驗證與測試

1. 前仿真階段

- SI/PI分析:HyperLynx仿真確定走線拓撲,確保眼圖張開度>60%

- EMI預測:CST Microwave Studio計算近場輻射,優化屏蔽方案

2. 后驗證測試

- TDR測試:時域反射儀測量阻抗連續性,采樣率>40GHz

- 近場掃描:探頭分辨率<1mm,定位輻射超標點

- EMC認證:依據CISPR32標準,10m法暗室測試輻射發射限值

九、特殊場景EMI控制

1. 汽車電子

- CAN總線終端電阻選用汽車級厚膜電阻(-40~125℃溫漂<±1%)

- 點火線圈驅動電路增加TVS陣列,箝位電壓<40V

2. 醫療設備

- 生物電信號采集前端采用Guard Ring結構,漏電流<1pA

- 射頻消融設備實現雙屏蔽層設計,層間介質厚度≥2mm

3. 航空航天

- 板級三防涂層介電常數<3.0,厚度均勻性±5μm

- 關鍵信號線實施冗余布線,間距>50mil

通過系統化的EMI控制策略,結合先進設計工具與制造工藝,可有效實現PCB電磁兼容性設計。從GHz級5G基站到μV級醫療傳感,科學的EMI管控技術持續推動電子設備向更高性能、更小體積、更低功耗方向演進。未來隨著AI輔助設計、光子集成等技術的發展,PCB的EMI控制將進入智能化、多維化新階段。

![[Vue]跨組件傳值](http://pic.xiahunao.cn/[Vue]跨組件傳值)