目錄

一、題目與題解

1.Simple wire(簡單導線)

2.Four wires(4線)

3.Inverter(逆變器(非門))?

4.AND gate??(與門)

5.?NOR gate??(或非門)

6.?XNOR gate(異或非(同或)門)

7.Declaring wires(聲明導線)

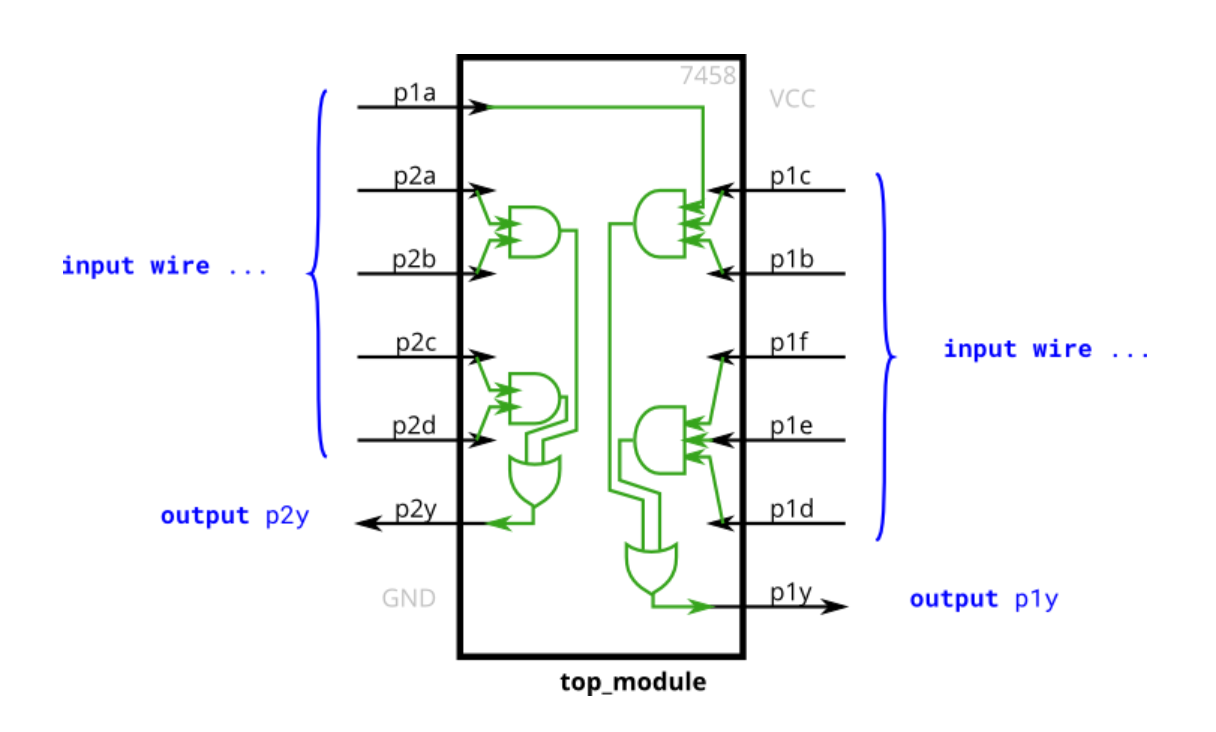

8.7458 chip( 7458芯片)

二、雜談

1.新的數據類型:wire

2.串聯運算符:{}

3.邏輯運算符

4.同或的表示方法

一、題目與題解

1.Simple wire(簡單導線)

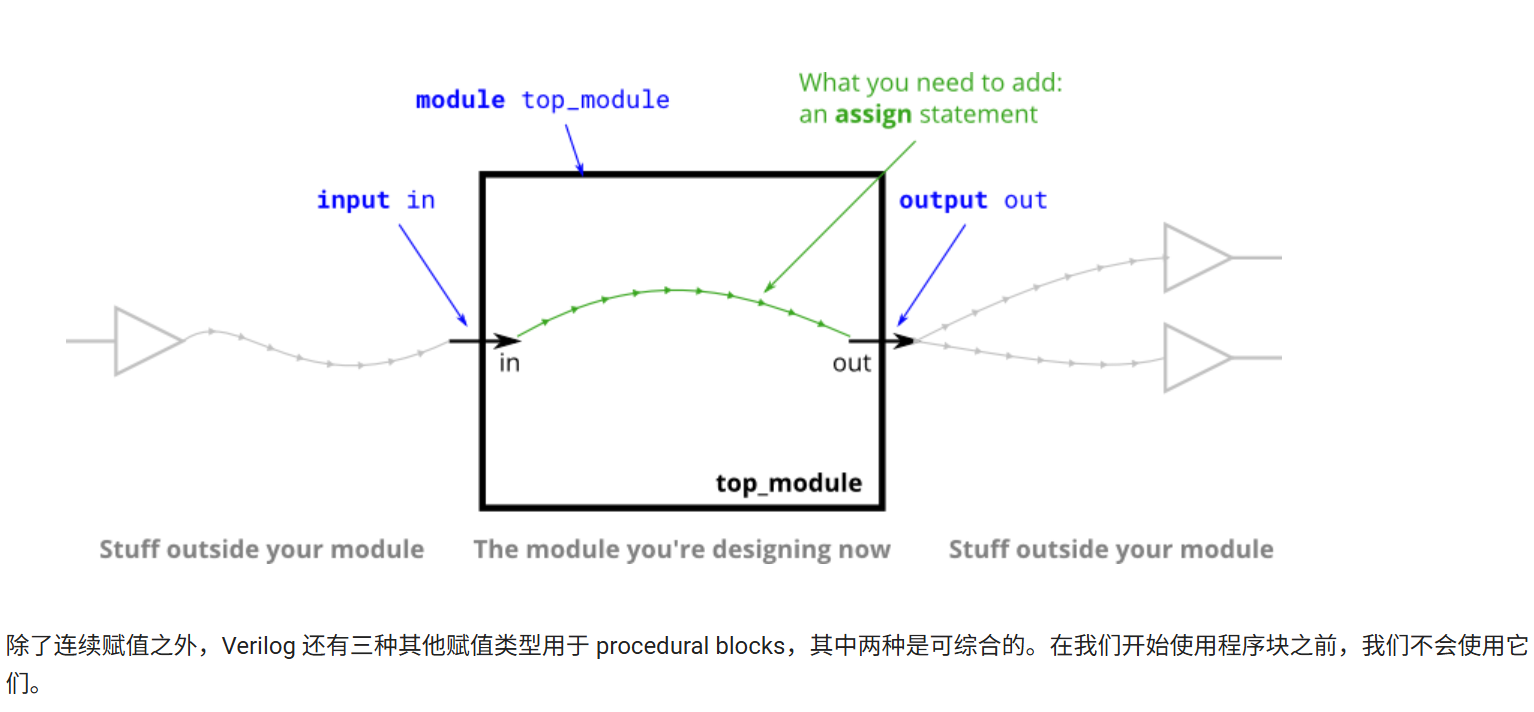

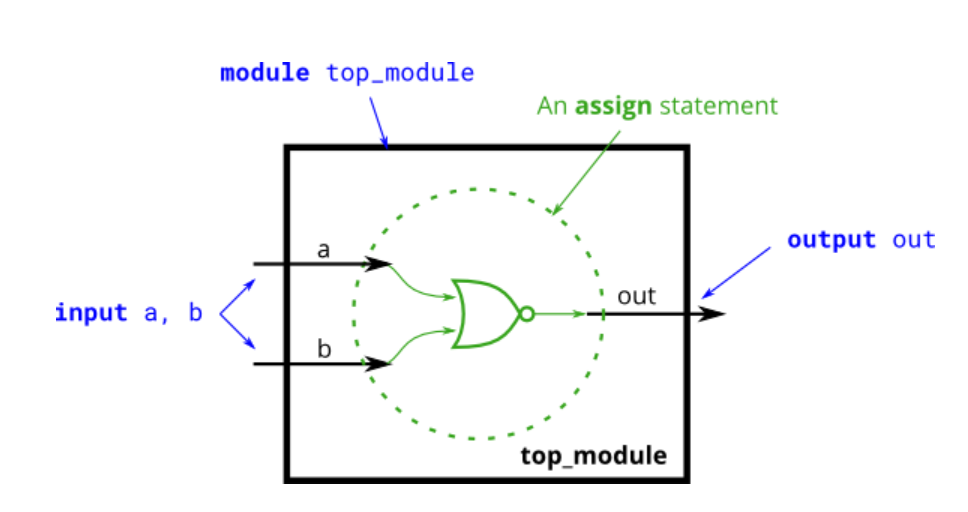

創建一個具有一個 input 和一個 output 的模塊,其行為類似于一條線。

與物理電線不同,Verilog 中的電線(和其他信號)是定向的?。這意味著信息僅沿一個方向流動,從 (通常一個)?源流向接收器?(源通常也稱為驅動器?,將值驅動到線路上) 。在 Verilog 的 “continuous assignment” (?

assign left_side = right_side;?) 中,右側的信號值被驅動到左側的導線上。賦值是 “continuous” 的,因為即使右側的值發生變化,賦值也會一直繼續。連續分配不是一次性事件。模塊上的端口也有一個方向(通常是輸入或輸出)。輸入端口由模塊外部的東西驅動,而輸出端口則驅動外部的東西。從模塊內部查看時,輸入端口是驅動器或源,而輸出端口是接收器。

下圖說明了電路的每個部分如何對應于Verilog代碼的每個位。模塊和端口聲明創建電路的黑色部分。您的任務是通過添加要連接到 的語句來創建一條線路(綠色)。開箱即用的部件不是您關心的問題,但您應該知道,通過將測試線束的信號連接到頂部_模塊的端口,可以測試您的電路。

module top_module( input in, output out );assign out = in;

endmodule2.Four wires(4線)

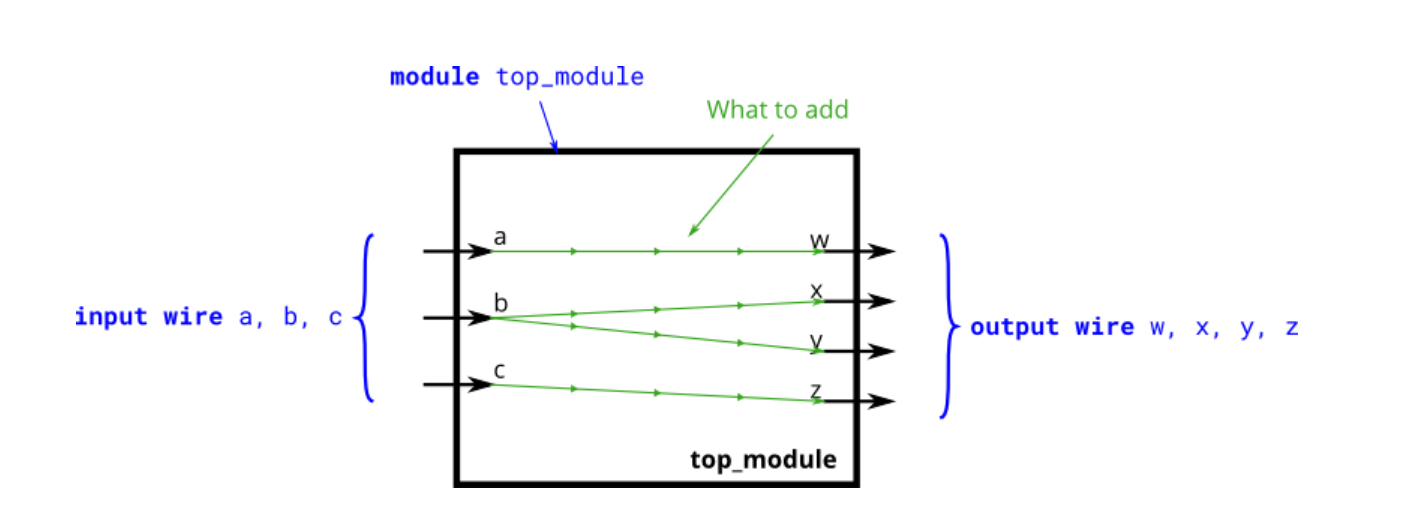

創建一個具有 3 個輸入和 4 個輸出的模塊,其行為類似于進行以下連接的電線:

a -> w b -> x b -> y c -> z下圖說明了 circuit 的每個部分如何對應于 Verilog 代碼的每個位。從模塊外部,有三個輸入端口和四個輸出端口。

當您有多個?assign?語句時,它們在代碼中出現的順序無關緊要。與編程語言不同,?assign?語句(“連續賦值”)描述事物之間的連接?,而不是將值從一個事物復制到另一個事物的操作?。

現在也許應該澄清一個潛在的混淆來源:這里的綠色箭頭代表電線之間的連接,但本身不是電線。該模塊本身已經聲明了 7 條電線(名為 a、b、c、w、x、y 和 z)。這是因為?

input?和?output?聲明實際上聲明了一個連線,除非另有指定。寫入輸入線 a?與寫入 a?相同。因此,assign?語句不是在創建電線,而是在已經存在的 7 條電線之間創建連接。?

module top_module( input a,b,c,output w,x,y,z );assign w = a;assign x = b,y = b;assign z = c;//如果我們確定每個信號的寬度,使用//串聯運算符等效且更短://assign {w,x,y,z}={a,b,b,c};

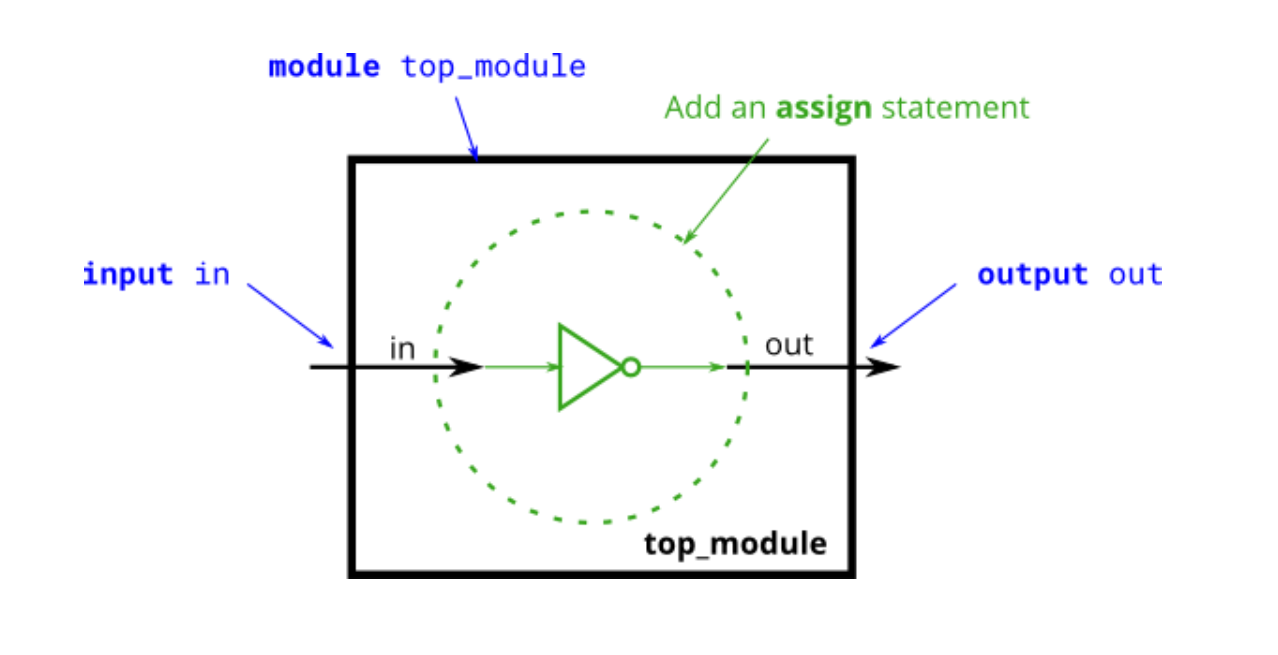

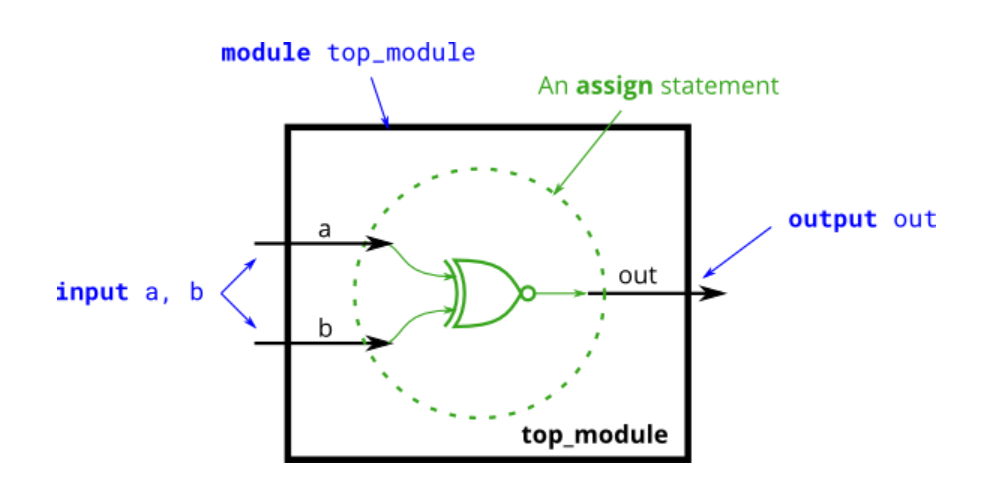

endmodule3.Inverter(逆變器(非門))?

創建一個實現 NOT 門的模塊。該電路類似于線,但略有不同。當從電線連接到電線時,我們將實現逆變器(或者"非門")而不是普通電線。使用assign語句。assign語句將持續將in的非轉換為out。

module top_module( input in, output out );assign out = ~in;

endmodule4.AND gate??(與門)

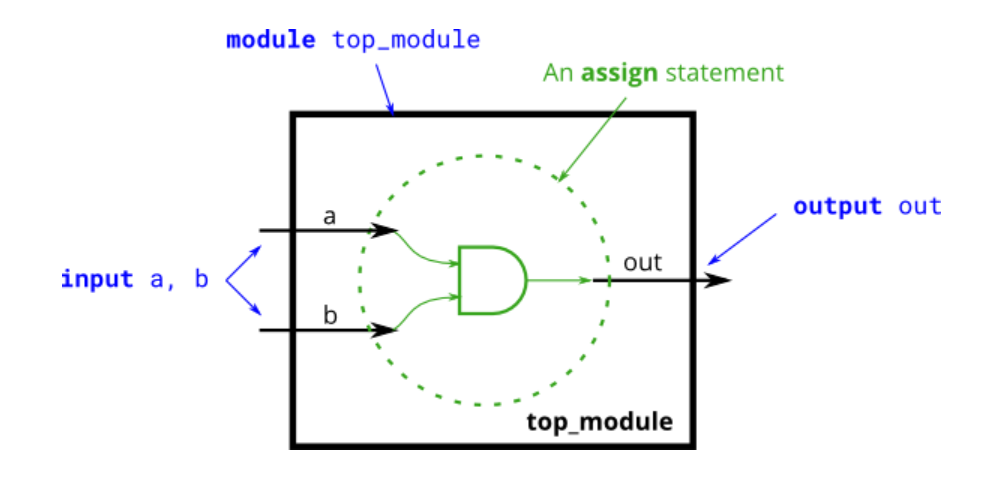

創建實現 AND 門的模塊。

該電路現在有三條導線(a、b和out)。導線a和b已經具有由輸入端口驅動的值。但wire out目前并不是由任何因素驅動的。寫一個assign語句,用a和b的AND信號輸出。

請注意,該電路與NOT門非常相似,只是多了一個輸入。如果聽起來不一樣,那是因為我已經開始描述信號是被驅動的(已知值由附加到它的某個東西決定)還是不是被某個東西驅動的。輸入線由模塊外部的東西驅動。assign語句將把一個邏輯電平驅動到一條線上。正如您所料,一條導線不能有多個驅動器(如果有,其邏輯級別是多少?),沒有驅動程序的導線將有一個未定義的值(在合成硬件時通常被視為0)。

module top_module( input a, input b, output out );assign out = a & b;

endmodule5.?NOR gate??(或非門)

創建一個實現或非門的模塊。或非門是輸出反轉的或門。在Verilog中編寫NOR函數時需要兩個運算符。

assign語句用一個值驅動一條線(或者更正式地稱為“網”)。該值可以是任意復雜的函數,只要它是組合函數(即無內存、無隱藏狀態)。assign語句是一種連續賦值,因為每當其任何輸入發生變化時,都會“重新計算”輸出,就像一個簡單的邏輯門一樣

module top_module( input a, input b, output out );assign out = ~(a | b);

endmodule6.?XNOR gate(異或非(同或)門)

創建一個實現 XNOR 門的模塊。

module top_module( input a, input b, output out );//assign out = a ~^ b;a和b相同輸出0,不同輸出1//assign out = a ^~ b;assign out = ~(a ^ b);

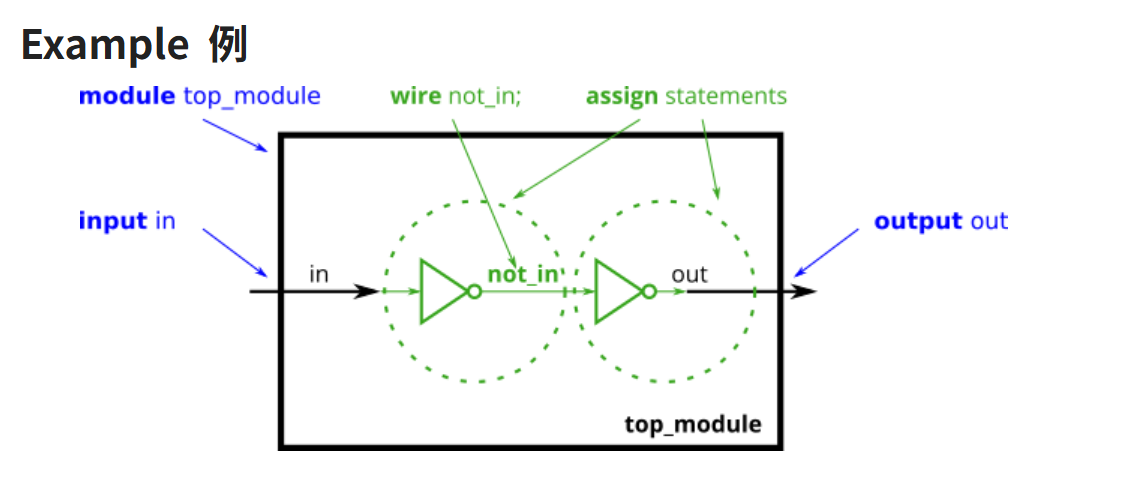

endmodule7.Declaring wires(聲明導線)

到目前為止,電路已經足夠簡單,以至于 output 是 inputs 的簡單函數。隨著電路變得越來越復雜,您將需要電線將內部組件連接在一起。當你需要使用 wire 時,你應該在 module 的主體中聲明它,在它第一次使用之前的某個地方。(將來,您將遇到更多類型的信號和變量,它們也以相同的方式聲明,但現在,我們將從 type 為?wire?的信號 ) 開始。

module top_module (input in, // Declare an input wire named "in"output out // Declare an output wire named "out" );wire not_in; // Declare a wire named "not_in"assign out = ~not_in; // Assign a value to out (create a NOT gate).assign not_in = ~in; // Assign a value to not_in (create another NOT gate).endmodule // End of module "top_module"在上面的模塊中,有三根電線 (?in?,?out?, 和?not_in?),其中兩根已經聲明為模塊的輸入和輸出端口的一部分(這就是為什么你在前面的練習中不需要聲明任何電線的原因)。需要在 module 內部聲明 wire?not_in?。從模塊外部不可見。然后,使用兩個?assign?語句創建兩個 NOT 門。請注意,您首先創建哪個 NOT 門并不重要:您最終仍然會得到相同的電路。

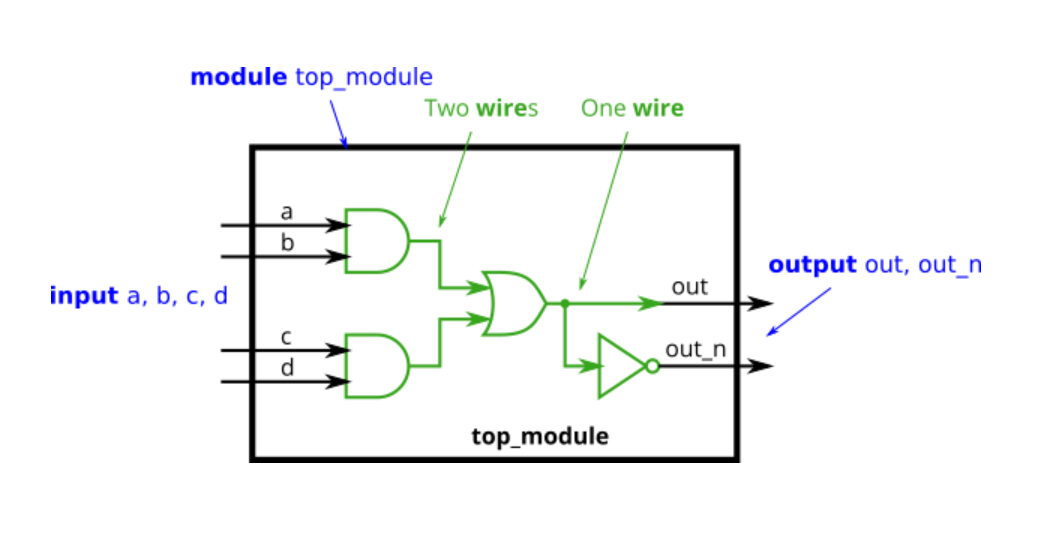

實現以下電路。創建兩條中間線(命名您想要的任何名稱)以將 AND 和 OR 門連接在一起。請注意,饋送 NOT 門的 wire 實際上是 wire?out?,因此您不一定需要在此處聲明第三根 wire 。請注意 wires 是如何由一個 source (gate 的 output) 驅動的,但可以饋送多個 inputs。

如果您遵循圖中的電路結構,則最終應該有四個 assign 語句,因為有四個信號需要賦值。

module top_module (input a,input b,input c,input d,output out,output out_n );wire w1, w2; // Declare two wires (named w1 and w2)assign w1 = a&b; // First AND gateassign w2 = c&d; // Second AND gateassign out = w1|w2; // OR gate: Feeds both 'out' and the NOT gateassign out_n = ~out; // NOT gateendmodule8.7458 chip( 7458芯片)

7458 是一款具有 4 個 AND 門和 2 個 OR 門的芯片。此問題比?7420?稍微復雜一些。

創建與 7458 芯片具有相同功能的模塊。它有 10 個輸入和 2 個輸出。您可以選擇使用?

assign?語句來驅動每根輸出線,也可以選擇聲明 (four) 線用作中間信號,其中每根內部線都由其中一個 AND 門的輸出驅動。如需額外練習,請嘗試兩種方式。

module top_module ( input p1a, p1b, p1c, p1d, p1e, p1f,output p1y,input p2a, p2b, p2c, p2d,output p2y );//第一種方法assign p2y = (p2a & p2b) | (p2c & p2d);assign p1y = (p1a & p1c & p1b) | (p1f & p1e & p1d);//第二種方法wire a,b,c,d;assign a = p2a & p2b;assign b = p2c & p2d;assign p2y = a | b;assign c = p1a & p1c & p1b;assign d = p1f & p1e & p1d;assign p1y = c | d;

endmodule二、雜談

1.新的數據類型:wire

2.串聯運算符:{}

? ? ? ? assign {w, x, y, z} = {a, b, b, c};

? ? ? ? 可實現一對一的賦值

3.邏輯運算符

? ? ? ? &與

? ? ? ? |或

? ? ? ? ~非

? ? ? ? ?^異或

4.同或的表示方法

? ? ? ?~ (a ^ b) == (a ^~ b) ==?(a ~^ b)

)

)

)