2.1 電阻的應用

2.1.1 與電阻相關的經典案例

如果說芯片是電路的骨架,那么電阻就是在芯片之間起連接作用的關節。電阻的阻值、布放位置等,對設計的成功起著至關重要的作用。

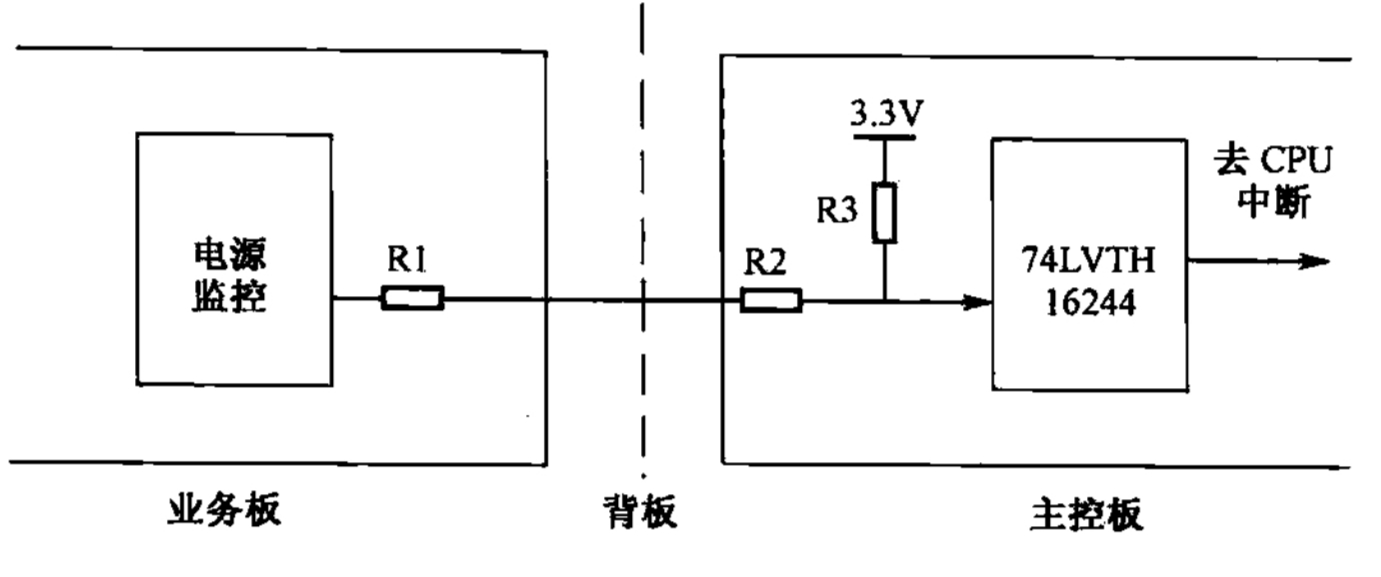

【案例2.1】串聯電阻過大,導致板間告警失敗

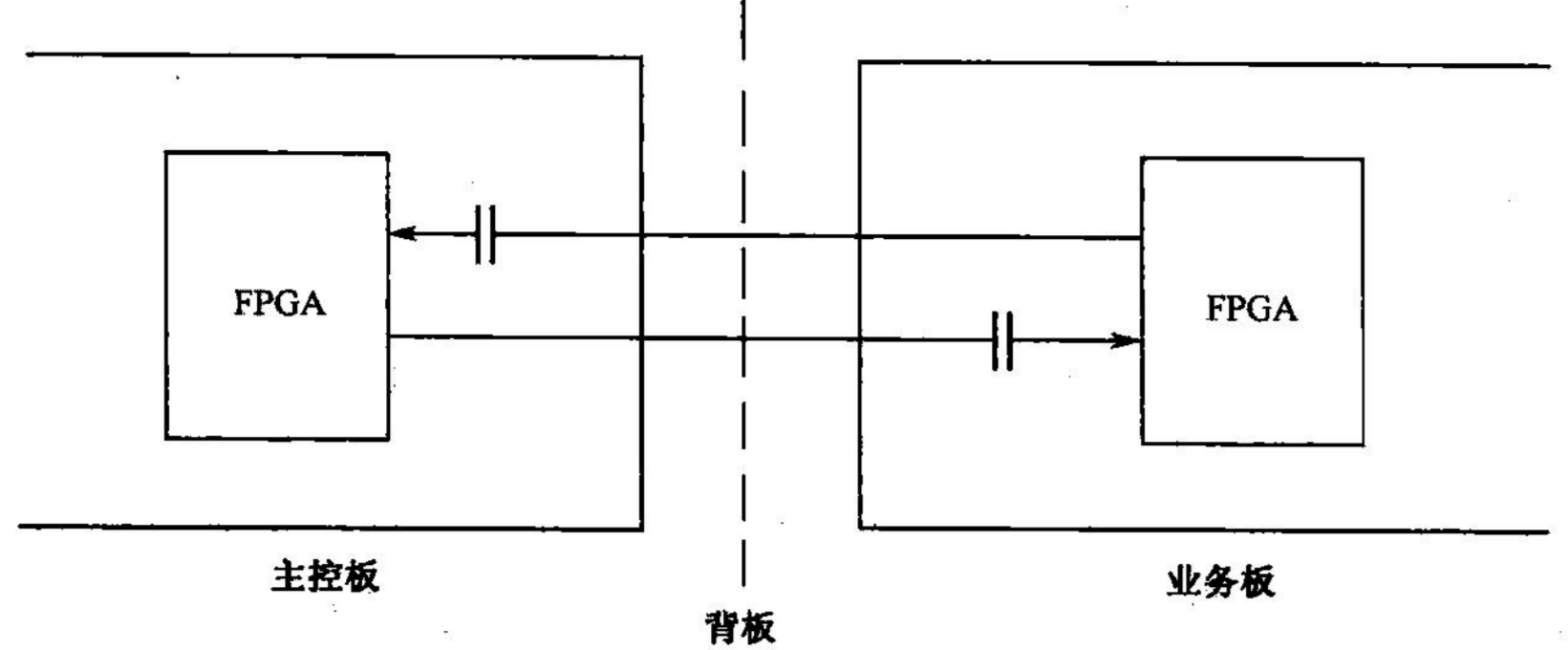

某產品由業務板和主控板構成。業務板上電源監控芯片的告警信號通過背板,輸送到主控板,經主控板上邏輯芯片74LVTH16244處理后連接到主控板上CPU的中斷信號。功能測試發現,強制將業務板被監控的一路電源拉地,CPU中斷信號卻不被使能。

【討論】

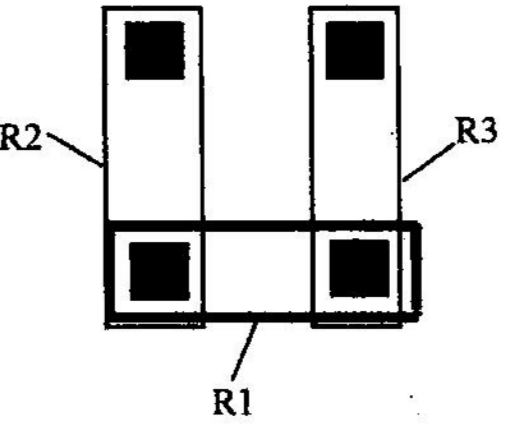

該部分電路如下圖所示。

考慮到單板的熱插拔要求,信號和背板連接器之間都串有電阻。R1=1kΩ(kΩ:千歐姆),R2=100Ω(Ω:歐姆),R3=1kΩ。

進行強度測試時強制將被監控的電源接地,在業務板側,測量業務板電源監控芯片輸出的告警信號,可測得有效低電平(0V),但在主控板74LVTH16244側,測得輸入信號電平為1.7V,遠超出低電平的輸入門限。

74LVTH16244是高阻抗輸入,因此3.3V將在三個電阻上分壓。當電源監控芯片輸出低電平0V時,經過分壓后,在主控板上74LVTH16244的輸入端分得電平為3.3V/2.1kΩ×1.1kΩ=1.7V,超出低電平門限。將R1的阻值更換為33Ω,告警時74LVTH16244的輸入電平為(3.3V/1.133kΩx0.133kΩ=0.38V),仍在低電平門限之內,主控板能正確識別告警信息。

這個案例看似簡單,但卻暴露了一個多單板協同設計時很容易出現的問題。在本案例中,考慮到熱插拔需要,單獨看主控板和業務板的設計都不存在缺陷,但在協同工作時卻暴露出問題。若一個產品由多塊單板組成,設計者在進行單板與背板連接器接口電路設計時,必須充分考慮本單板與其他單板協同工作的問題。

需要提及的是,有些設計者會有疑問,將R1的阻值改為33Ω后,74LVTH16244的輸入電平0.38V雖然處在輸入信號的低電平門限范圍內,但容量不是很大,能不能將R3的阻值增大,如果用4.7kΩ等,使得告警時74LVTH16244的輸入電平進一步降低?答案是不能,這涉及邏輯器件實現電平翻轉時的電流要求,將在第3章做詳細分析。

【案例2.2】電阻額定功率不夠造成的單板潛在缺陷

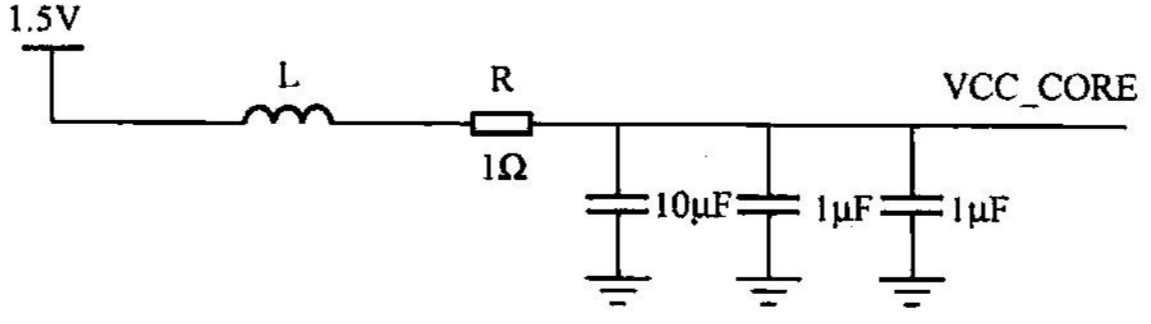

某單板上PHY芯片(以太網物理層芯片)的核心電源濾波電路設計如下圖所示。

根據PHY芯片資料,該電源對噪聲等于抗特別敏感,因此在設計中不僅采用了LC濾波電路,還在輸入之后串聯了一個1Ω的電阻R。LC濾波電路能濾除高頻段噪聲,而本電路中的電阻R不僅能衰減高頻段噪聲,而且能衰減低頻段噪聲,即能作為一個全頻段衰減器。這種設計方法常用于對噪聲特別敏感的電源,如時鐘的電源等。

單板長時間運行發現,電阻R經常爆裂。

【討論】

設計中選用的電阻R,尺寸為0402,額定功率為1/16W,核對PHY芯片資料,其內核電源最大功耗為300mW,即最大電流為200mA,而該電阻的最大通流能力僅62.5mA。當PHY全速工作時,電流將超過電阻的額定電流,造成電阻損壞。

類似的案例很多,設計者在電阻選型時,對阻值往往非常關注,卻比較容易忽略對額定功率的審核。

本案例中,電阻的失效能通過實驗室長時間測試反映出來,這是很值得慶幸的事情。若電阻的額定電流和實際工作電流比較接近,則可能構成產品的一個潛在缺陷。

【拓展】

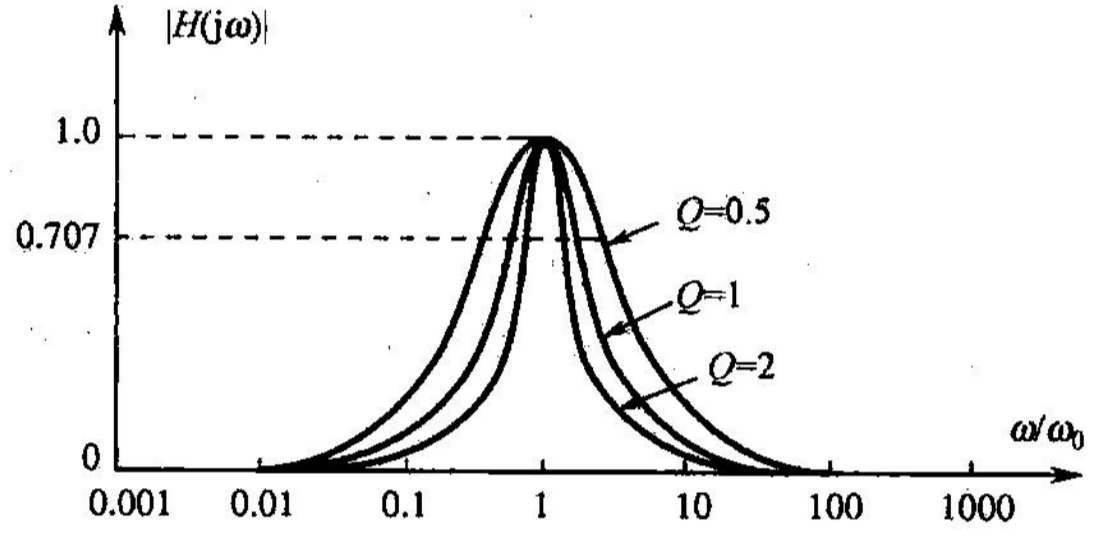

在本案例中,電阻起的是全頻段濾波的作用,在類似應用中,電阻還有一個作用是降低電路的品質因數Q。Q定義為回路發生諧振時,儲存能量與一周期內消耗能量之比。在一個由R、L、C組成的串聯電路中,總阻抗Z=R+1/(jω?C)+jω?L=R+j[ω?L-1/(ω?C)],回路諧振時,假定諧振頻率為ω?,則滿足ω?L=1/(ω?C),此時電路的總阻抗達到最小值R,Q的值如下:

Q=ω?L/R = 1/(ω?CR)= 1/RX(L/C)^1/2? ?(2.1)

因此,回路發生諧振時,能量將集中于諧振頻率點ω?,根據Q值的不同,繪制回路幅頻特性曲線如圖2下圖所示,圖中|H(jω)|是電路傳遞函數的模,該值越接近1,表示電路越能無損耗地傳遞能量。從圖中可以發現,Q值越大,能量越集中,表現為|H(jω)|的值越接近1,電路的損耗越小。

在儲能電路中,Q值越大,意味著損耗越小;在選頻電路中,Q值越大,意味著濾除其他頻帶信號的能力越強。因此在這些情況下,希望Q值越大越好。

但在電源或信號線路中,Q值越大,通常意味著性能越陡峭,越容易引發振鈴等現象,信號通過這種回路后容易發生失真。因此在這種情況下,希望Q值小一些比較好。

在本例所示的原理圖中,加入電阻R可降低Q值,以避免電源線路的振蕩。

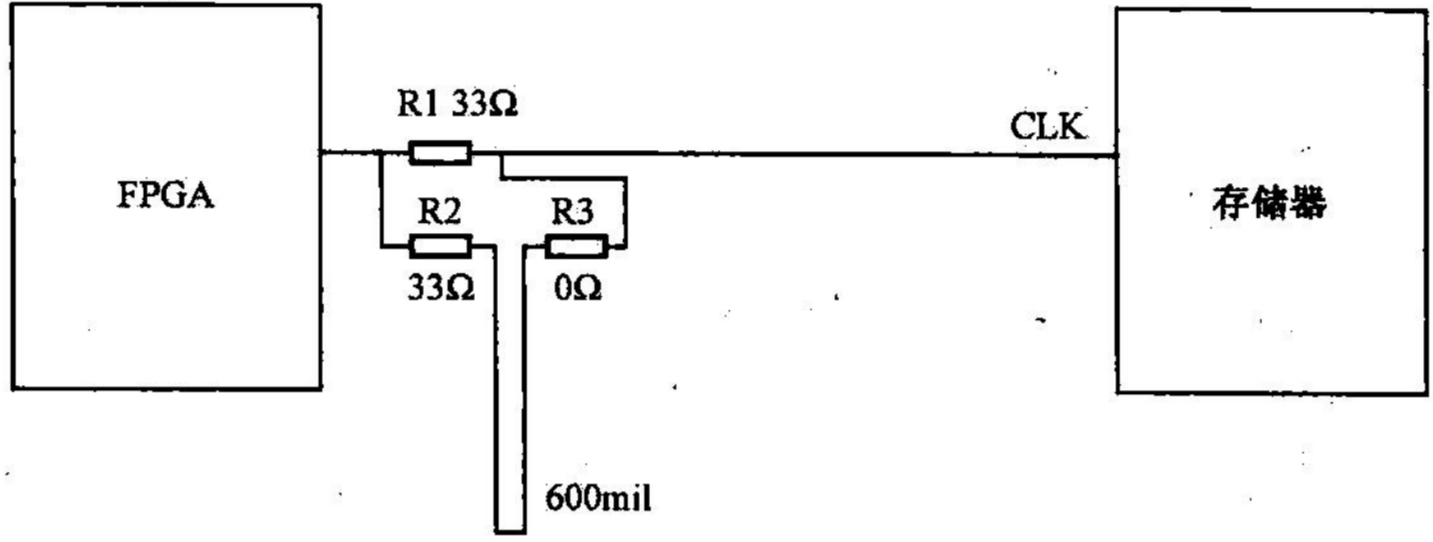

【案例2.3】電阻在時序設計中的妙用

某設計要求FPGA芯片兼容地支持兩個廠家的存儲器,經時序分析發現,這兩個廠家的存儲器雖然引腳的定義完全相同,但時序參數卻略有差異。經時序計算后,B廠家存儲器件的時鐘信號線要比A廠家的長600mil(mil即米爾,是長度單位1mil=0.0254mm)。

【討論】

一個設計(即同一份原理圖和PCB)同時兼容兩個廠家的器件,是電路設計中常見的需求,此時,QG電阻往往能起到極好的作用。

如下圖所示,當采用A廠家存儲器時,將R1加入物料清單中,而R2和R3不入物料清單;當采用B廠家存儲器時,R2和R3加入物料清單,而R1不入物料清單。

PCB設計的注意事項有:第一,R2需要緊靠近R1的右邊引腳放置,R3需要緊靠近R1的右邊引腳放置,這樣做的目的是減少在時鐘信號線上可能出現的分叉(stub);第二,R2和R3之間的走線長度為600mil,以滿足B廠家存儲器的要求。

如果信號速率極高,短小的分叉將對信號完整性產生很大的影響。因此,當設計不允許信號線上存在分叉時,可以采用如圖2.5所示的PCB設計。

在下圖中的PCB上,將R2和R3各自的一個引腳焊盤與R1的兩個引腳焊盤分別重合,R2和R3的另一個引腳通過600mil走線連接,從而可以完全避免在R1與R2、R3之間存在的分叉。采用這種方式,PCB上將出現設計規則檢查(DRC)錯誤,可以將這個錯誤忽略,并通過產品工程師。

2.1.2 電阻應用要點

在高速電路設計中,對于電阻的應用,有四個關注點:

(1)電阻的阻值;

(2)電阻的精度;

(3)電阻的額定功率;

(4)電阻的精度。

其中,對于阻值,可依據電路的要求計算得到。有時候計算得到的阻值屬于非常用阻值,從節省成本的角度考慮,建議采用常用阻值的電阻通過串聯或并聯的方式構成該阻值。例如,363Ω的阻值,可采用常用阻值330Ω和33Ω串聯構成。這樣做的目的,一方面可以構建比較精確的阻值,另一方面可以避免選用非常用的電阻器件。一般而言,越是非常用的器件,價格往往越高。

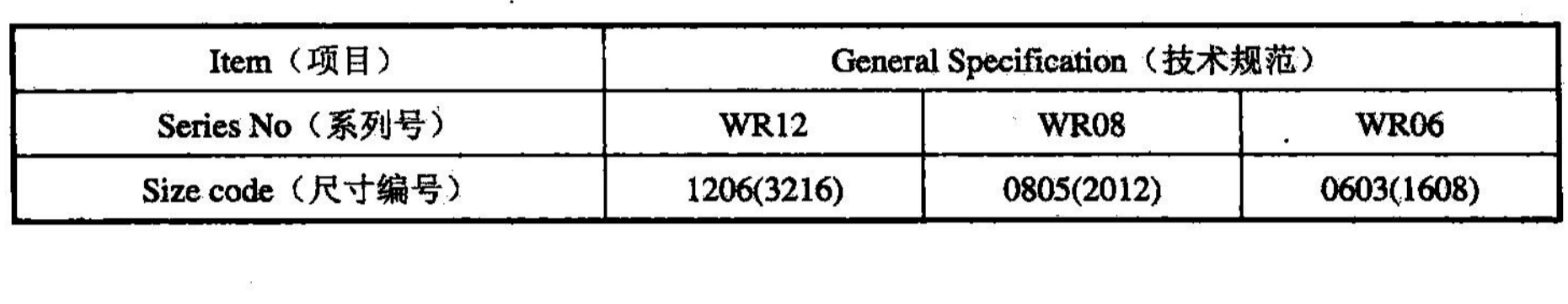

對于尺寸,需注意電阻的廠家資料上往往提供有兩種尺寸代碼,如下表所示。

上表中摘自某電阻的廠家資料。表中同一系列的電阻有兩種尺寸代碼,一種是EIA(美國電子工業協會)代碼,另一種是公制代碼。這兩種代碼都由4位數字構成,前兩位表示電阻封裝的長度,后兩位表示寬度。EIA代碼是英制代碼,以英寸為單位,如0603的電阻,表示長度為0.06in(60mil),寬度為0.03in(30mil)。該電阻的公制代碼為1608,表示長度為1.6mm,寬度為0.8mm。

上表中摘自某電阻的廠家資料。表中同一系列的電阻有兩種尺寸代碼,一種是EIA(美國電子工業協會)代碼,另一種是公制代碼。這兩種代碼都由4位數字構成,前兩位表示電阻封裝的長度,后兩位表示寬度。EIA代碼是英制代碼,以英寸為單位,如0603的電阻,表示長度為0.06in(60mil),寬度為0.03in(30mil)。該電阻的公制代碼為1608,表示長度為1.6mm,寬度為0.8mm。

額定功率和精度這兩項參數比較容易被忽略。案例2.2就是與額定功率相關的案例,在針對額定功率的選型時,需要注意至少降額20%使用。

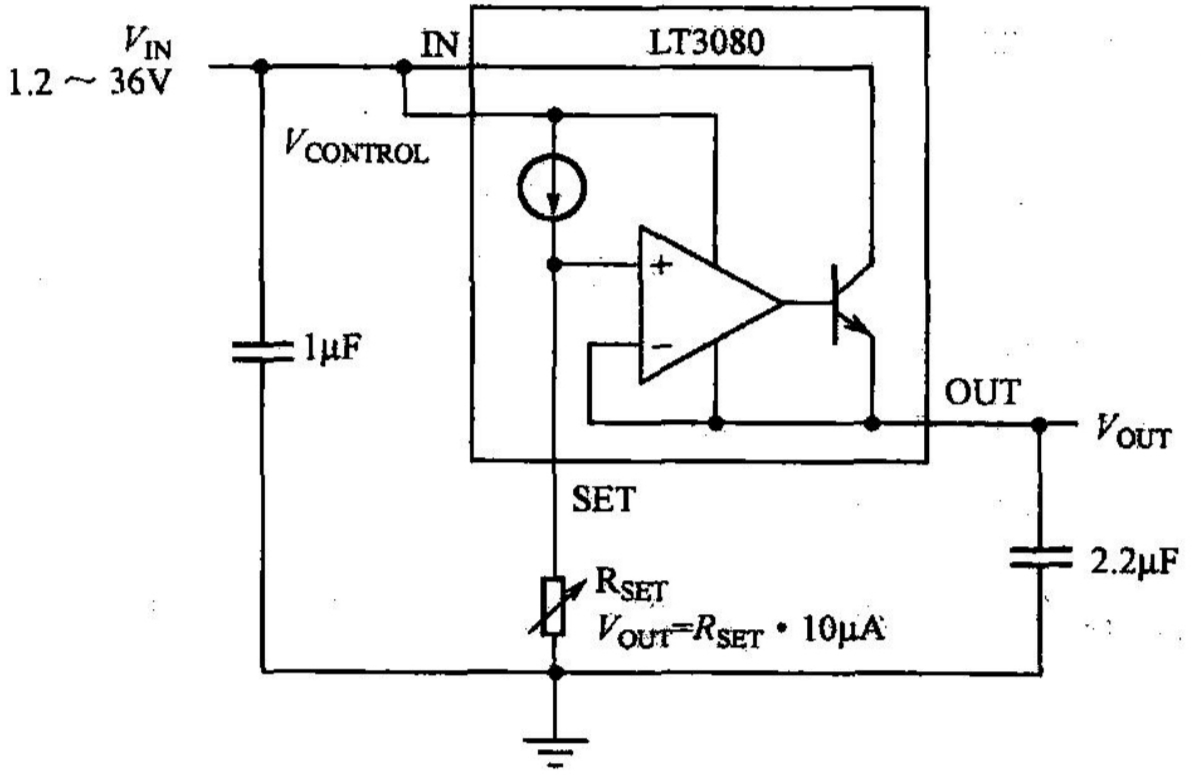

關于精度,最常見的應用是在電源芯片上。如下圖所示為Linear公司的LDO電源芯片LT3080,利用外部的電阻RSET設定VOUT的值。

在這種應用中,電阻的精度直接決定了輸出電壓的精度,如果選擇5%精度的電阻,則輸出電源的電壓波動范圍將達到10%,顯然無法滿足設計的要求,因此必須選擇1%精度的電阻,即使這樣,僅僅因為該電阻的精度偏差,輸出電源的電壓偏差就達到了2%。

理解要點:

① QG電阻對高速電路設計有重要的意義。

② 在功耗高的路徑上,如果串聯了電阻,選型時需要考慮電阻的額定功率。

③ 當電阻用于設定器件的工作參數時,應選擇高精度電阻。

2.2 電容的選型及應用

2.2.1 與電容相關的經典案例

電容對高速電路的貢獻非常大,即便是在一塊最普通的單板上,電容也隨處可見。因此,電容是電路設計中最為常見的器件。但同時,電容也是最容易被忽視的器件。在設計中,設計者們往往知道需要放置電容,但對電容的選型卻隨心所欲。

事實證明,很多單板的設計失敗,根本原因就在于電容。以下根據實際工作中的三個案例來說明電容選型的重要性。

【案例2-4】電容失效導致低溫下硬盤停止工作

某單板設計以及功能驗證完成后,在溫箱里做-30℃的低溫冷啟動測試,發現單板啟動到“硬盤檢測”步驟時報錯。在此條件下測試硬盤的5V電源,發現其紋波很大,達到800mV,使硬盤無法正常工作。設計人員重新審視原理圖后發現,在硬盤的5V電源上除了若干小容量的陶瓷電容以外,大容量的電容只有一個,是47μF的鋁電解電容,該電容的工作溫度范圍為-55℃~105℃。將此鋁電解電容更換為同樣容值的鉭電容后,在-30℃做多次低溫冷啟動,單板工作正常。

【案例2.5】多次帶電插拔子板導致母板上鉭電容損壞

在調試中,對某單板上的子板做多次熱插拔功能測試,發現插拔十多次就會導致母板上的一顆鉭電容爆裂。該單板由母板和子板構成,兩者通過連接器連接。由母板提供12V電源,經過連接器后送到子板,作為子板的工作電源,而該鉭電容是母板上靠近連接器就近布放的。為12V電源濾波的電容,其標稱值是100μF,額定電壓16V。將該電容更換為同樣容值的鋁電解電容后,問題得到解決,強度測試通過。

【案例2.6】高速電路中電容應用問題導致CPU工作不穩定

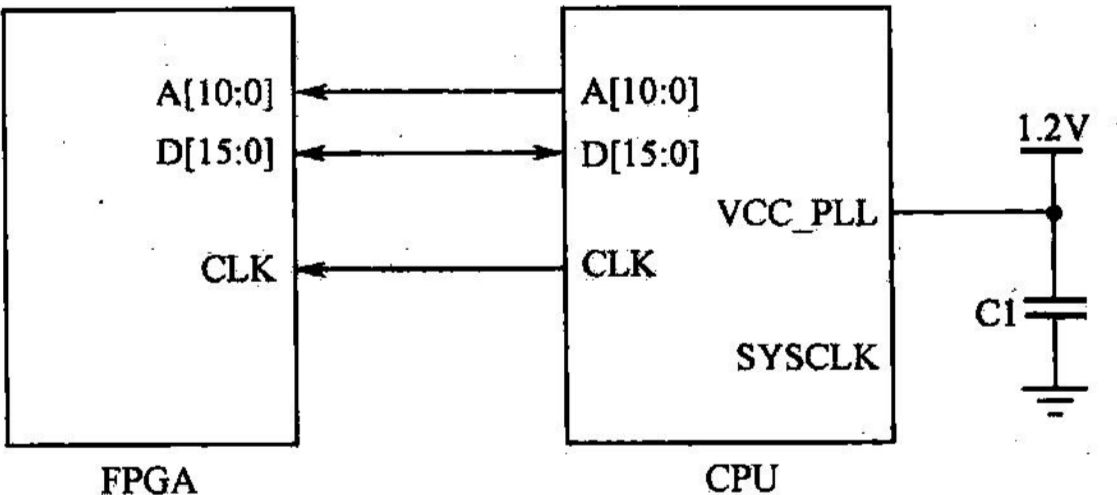

某單板上,以太網數據包的處理工作由CPU負責完成。測試發現,在少量數據處理時,單板工作正常,而一旦出現大量數據處理,偶爾會發生丟數據包現象。以太網數據是通過板上FPGA進行預處理后再送到CPU,簡化原理圖如下圖所示。

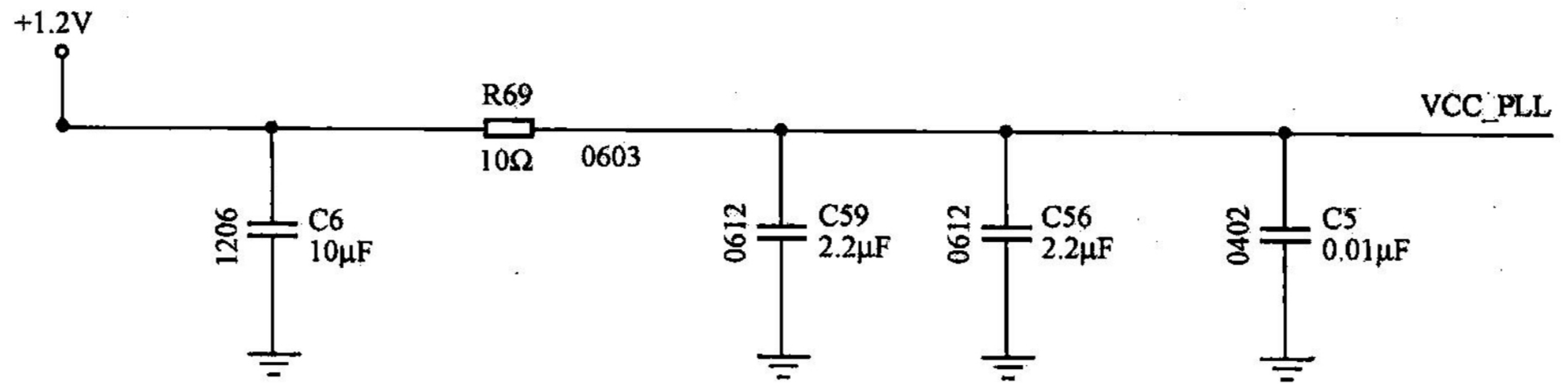

SYSCLK是CPU的系統時鐘,頻率為66MHz,由外部66MHz晶振提供。CLK為CPU和FPGA之間接口電路的工作時鐘,頻率為132MHz,由CPU內部鎖相環對SYSCLK倍頻產生。通過對CPU和FPGA之間的總線進行信號質量以及時序測試,大量數據處理時,借助示波器的快速采集功能,可以發現FPGA一側的輸入數據在某些瞬時無法滿足時序要求,而大多數情況下卻有充足的時序余量。重新分析時序,發現時序設計正確。用示波器單獨測量CLK信號的完整性,打開快速采集功能,發現在某些瞬間,CLK信號的邊沿會發生1/4周期的偏移。由此懷疑CPU內部的鎖相環工作不穩定,測量給鎖相環供電的VCC_PLL引腳,紋波達到50mV,紋波加上噪聲達到70mV。該電路設計時,VCC_PLL信號上沒有放有一個10μF、1206封裝的陶瓷電容,改板后在VCC_PLL引腳附近就近增加兩個0612封裝的2.2μF陶瓷電容,和一個0402封裝的0.1μF陶瓷電容,問題得到解決。

類似的案例還有很多,表面上看都不違背電路原理。案例2-4中的鋁電解電容,標稱溫度范圍能達到-55℃,為何在-30℃就會出現問題?案例2-5中的鉭電容,額定電壓16V,距離其工作電壓12V還有33%的裕量,為何會出現爆裂?案例2-6中的電容失效,經過長時間、大量信號測試后,卻發現根源竟是幾個電容。在設計中,出現的問題卻需要耗費大量的調試時間,那么在設計中,如何避免出現類似問題?本節內容將主要就電容的選型和應用要點展開討論。

2.2.2 高速電路設計中電容的作用及分析

1. 高速電路設計中電容的作用

1)電容的作用之一——電荷緩沖池

在高速電路設計中,電源的負載是動態的,即高速運行器件的電流和功耗是不斷變化的。為了保證器件工作的穩定,希望器件的工作電壓不隨電流和功耗的劇烈變化而同程度變化,即希望器件電壓盡量穩定。在這種情況下,需要為器件提供一種緩沖池,以便當外界環境劇烈變化時,器件的工作電壓能保持相對的穩定。電容的本質是儲存電荷和釋放電荷,當外界環境變化時,電容中的電荷能被迅速積累或釋放。根據公式ΔU=Q/C?ΔU表示電容兩端電壓的變化量,ΔQ表示電容兩端電荷的變化量,C 為電容的容值),當外部環境的變化驅使器件的工作電壓增加或減少時,電容能通過積累或者釋放電荷以吸收這種變化,即將器件工作電壓的變化轉變為電容中電荷的變化,從而保持器件工作電壓的穩定。因此,電容的作用之一就是電荷緩沖池,以使高速運行器件的工作電壓保持穩定。

2)電容的作用之二——高頻噪聲的重要濾波器

對高速運行的電路而言,無時無刻不存在狀態的轉變。例如,信號的狀態不斷在1和0之間切換,器件的電流方向不斷在輸出和輸入之間切換。這種高速的轉變,將在電路上產生大量的噪聲干擾。從頻譜上看,這些干擾在相當大程度上處于有效信號的2次、3次等倍頻頻率,在電源傳輸路徑上,需要將這些干擾濾波到相對穩定的地平面上,以免影響器件的工作。根據公式Z=1/(jωC),當頻率較高時,電容表現為低阻抗,因此,可將電容作為高頻噪聲的重要濾波器。

3)電容的作用之三——實現交流耦合

當兩個器件通過高速信號互連時,信號兩端的器件可能對直流分量有不同的要求。例如,A 和 B 兩個器件之間通過高速差分對信號互連,但 A 器件工作于1.8V,B 器件工作于3.3V,則 A 器件驅動的差分信號將攜帶1.8V直流分量,導致信號到達接收端 B 器件時無法被正確識別。反之,B 器件驅動的信號,到達 A 器件,其電平可能超過 A 器件所允許的最大輸入電平。對于這種情況,需要將信號所攜帶的發送端的直流分量在達到接收端前,予以濾除,即隔離信號兩邊器件的直流分量。基于電容的通交流、阻直流的天然特性,電容具有這種隔離功能。因此,電容的作用之三是實現交流耦合(AC Couple),以實現對直流的隔離(DC Blocking)。

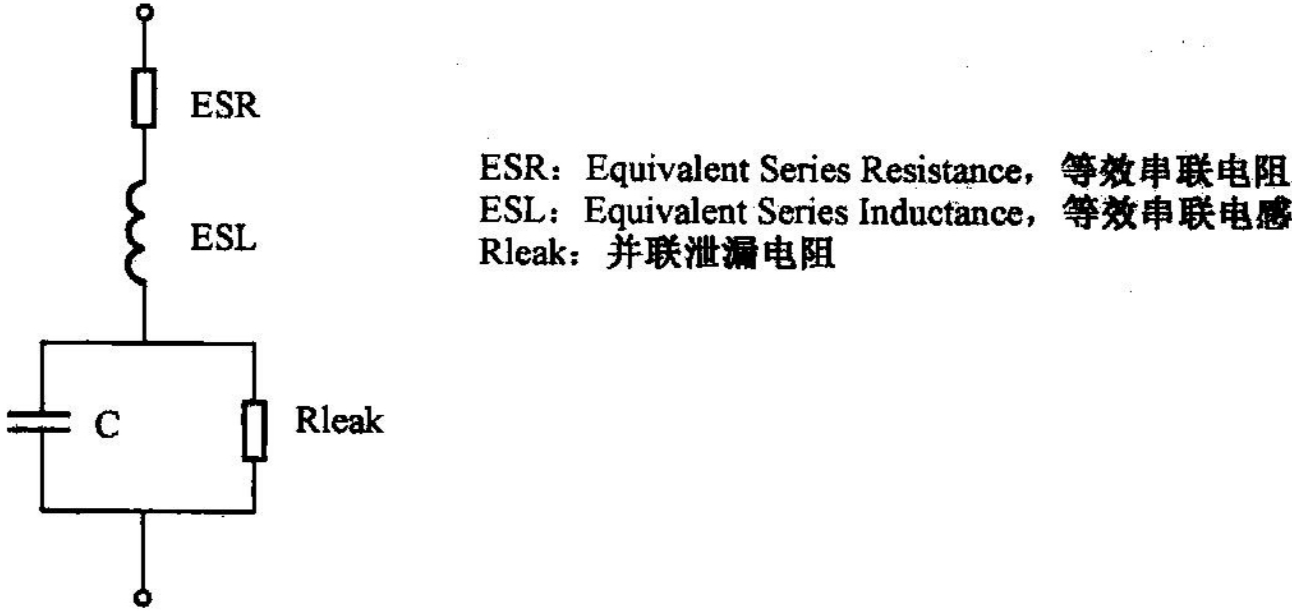

2. 電容等效電路的分析

如下圖所示,在高速設計領域,電容器件并不是純粹的電容,而是帶有電阻、電感等成分的小電路。其中 ESL 由容器件的引腳電感和電容器件兩極間等效電感串聯而成,主要取決于封裝;ESR 由電容器件的引腳電阻和電容器件兩極間等效電阻構成,主要取決于電容工作溫度、工作頻率以及電容體本身的導線電阻等;Rleak 則取決于容器件本身特有的泄漏特性。可以認為,電容器件的特性同時取決于電容分量、ESL分量、ESR分量及泄漏特性。

ESR:Equivalent Series Resistance,等效串聯電阻

ESL:Equivalent Series Inductance,等效串聯電感

Rleak:并聯泄漏電阻

1)電容分量

以一個案例來分析電容器件的電容分量對高速設計的影響。

【案例2.7】交流耦合電容選擇不當引起數據幀出錯

如下圖所示,某產品主控板和業務板的FPGA通過背板上電平為LVPECL的差分對信號線互連,數據速率是800Mbps(Mbps:兆比特每秒),為隔離兩板間直流偏置電平的相互影響,采用交流耦合,耦合電容選用0.01μF的陶瓷電容。測試發現,發送某些碼型時,接收方經常檢測到數據幀出錯。

【討論】

仔細研究出錯的碼型,發現它們都有一個共同的特性,即存在較長連續0和連續1比特位的情況。從邏輯設計工程師處獲知,FPGA并沒有對發送的數據幀進行擾碼處理,而是將原始數據幀直接發送到外部信號線上。交流耦合電容在正常工作時,處于平衡的充放電狀態,但原始數據幀中較長連0和連1比特位的出現,打破了這種平衡,使得信號通過判決門限的時間發生抖動,導致接收端判決出錯。

在交流耦合中,電容串接在線路中,阻抗為1/jωC。容值越小的電容,對低頻信號所表現出的阻抗越大,使低頻信號的衰減越嚴重。

定義Tc為每比特位的數據周期,NUM為最大容許連0或連1比特位的數目,負載的阻抗為R(一般取50Ω),C為交流耦合電容容值。則有經驗公式:

Cmin=7.8xNUMxTc/R(2.2)

本例中,Tc=1.25ns,R=50Ω,根據碼型分析,本產品應用中可能出現的最大連0或連1比特位的長度為85,因此設定NUM=86,則交流耦合電容的最小取值要求為

Cmin=7.8x86x1.25ns/50Ω=16.77nF=0.01677μF

設計中,選用0.01μF的耦合電容,顯然無法滿足式(2.2),導致數據幀出錯。

在設計時需注意,耦合電容取值也不能太大,如果容值太大,將無法滿足高速信號變換的邊沿斜率要求。在高速設計中,一般取耦合電容的容值為0.1μF,這樣既可以滿足數據幀中可能出現的長1長0情況,又能滿足高速信號變換的要求。

2)ESL分量

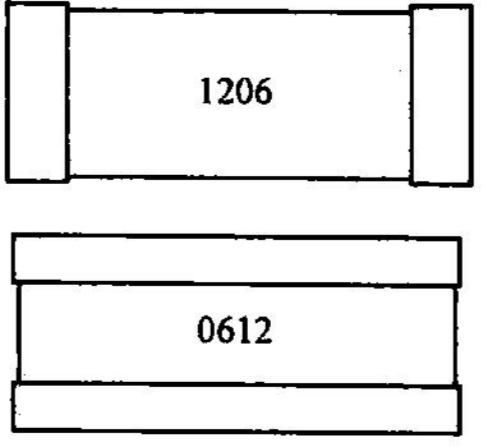

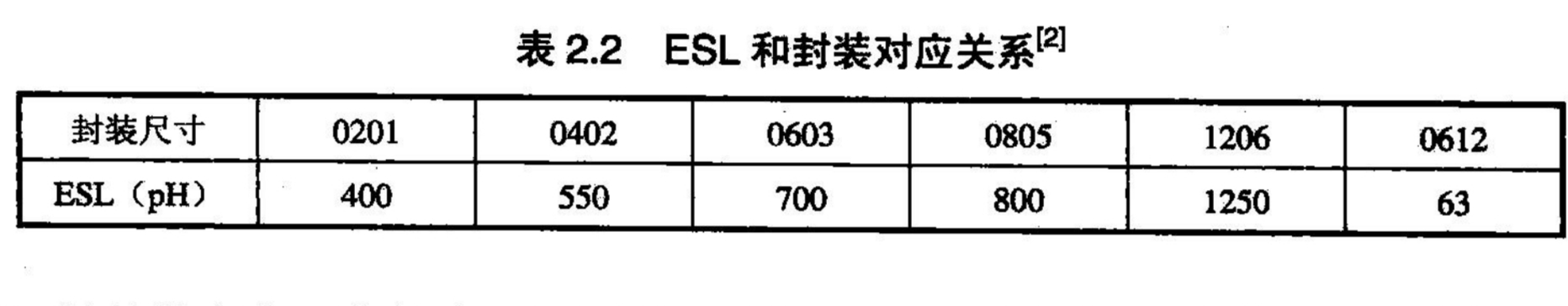

如何利用封裝信息獲得大致的ESL值?ESL值取決于電容器件的類型和封裝。在高速電路中,應選用ESL值小的貼片電容,因此僅以小尺寸貼片式的陶瓷電容作為示例,對于插孔式電容,如鉭電解電容,其ESL值將比下表所列出的值大得多。從下表列出,隨著封裝的增大,ESL值將隨之增大。比較特殊的是0612封裝的貼片電容,其ESL值不僅遠遠小于相同外形尺寸的1206的ESL值,甚至小于目前業界尺寸最小的0201封裝的ESL值。下圖所示為1206和0612封裝的電容的對比。

0612封裝的電容,其長邊為焊接邊,連接PCB上的焊盤,相比1206封裝,一方面可以有更大的、能直接和PCB焊盤貼合的面積;另一方面,其內部電容體到PCB焊盤的距離也更近,因此ESL值最小。就成本而言,在相同容值的條件下,0612封裝比1206封裝只是略微貴一些。

【案例2.8】利用0612封裝的電容增強濾波性能

結合案例2-6,更正后的VCC_PLL濾波電路如下圖所示。

?【討論】

對VCC_PLL的濾波,使用了兩個0612封裝的濾波電容。一個就近CPU的VCC_PLL引腳放置,一個布放在VCC_PLL這條信號線(PCB上應加粗)離CPU引腳最遠的位置。第一個電容的作用是濾除外界對CPU引腳的干擾,第二個電容的作用是消除CPU引腳對外界的影響。

3)ESR分量、泄漏特性及其他信息

以下討論如何通過閱讀電容的器件資料來獲得信息。

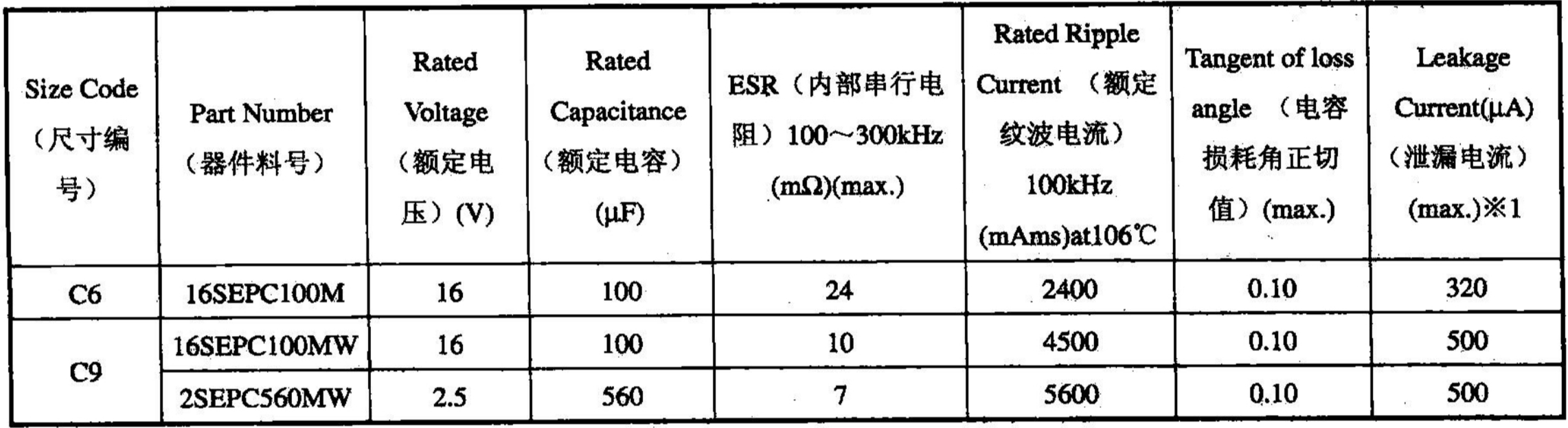

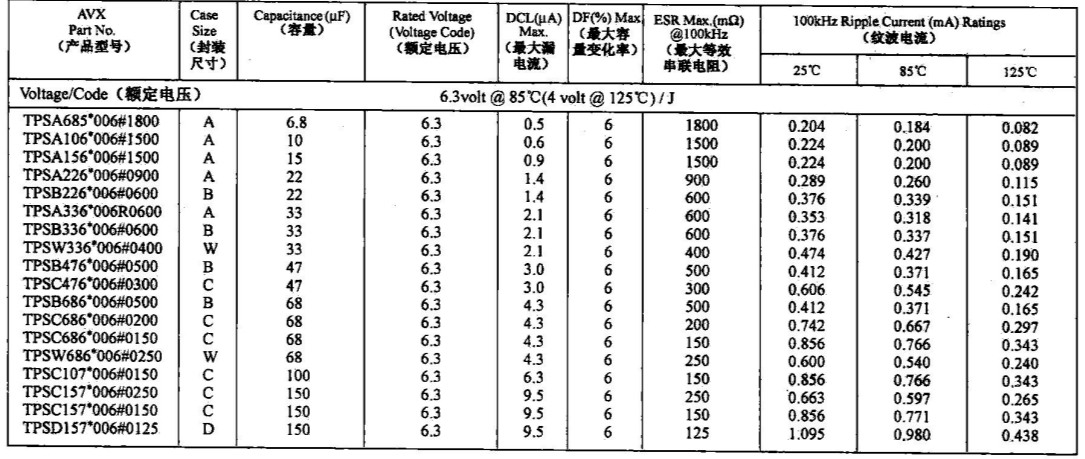

下表為截取自某電容的器件資料。

?Size Code:廠家制定的尺寸編號。

?Size Code:廠家制定的尺寸編號。

Part Number:廠家制定的器件料號,采購時需要向廠家提供該參數。

Rated Voltage:額定電壓,器件最高工作電壓不超過該值。

ESR:在100~300kHz頻帶范圍內,電容器內部串行電阻的最大值,該值隨著工作頻率而變化,因此需要根據實際應用的頻帶范圍取值。如果應用的頻帶范圍不在廠家提供的參數表中,需要向廠家咨詢。

Rated Ripple Current:本例中的電容一般用在單板的總電源處,因此需要能承受上下電時大電流的沖擊,此參數的值越大,表示承受大電流沖擊的能力越好。

Tangent of loss angle:電容損耗角正切值。理想電容工作時,產生無功功率Q(無損耗),由于電容內部存在ESR及泄漏電流,實際應用中會產生一定的損耗功率P,定義tan δ=P/Q,tan δ就稱為電容損耗角正切值。這個值越小,電容的功率損耗就越小。

Leakage Current:電容內部存在Rleak(見上圖),因此存在泄漏通路,該參數用于定義流過電容的泄漏電流。

【案例2.9】LDO電源應用中的濾波電容ESR問題

某單板上FPGA供電選用Linear公司的LDO電源芯片LT1963,輸出電壓1.5V。LT1963的外部濾波電容選取10μF,尺寸為0805。類型為X5R的陶瓷電容。在單板的調試中發現,上電時,在LDO輸出的1.5V電源上會出現一個瞬間高達1.8V的沖擊。最初設計者認為是外部電容容量不夠所致,增加一個相同的10μF陶瓷電容,現象依舊。仔細閱讀LDO芯片資料,發現資料提到,該LDO需要利用外部電容的ESR作為高頻補償,ESR太小的電容不足以滿足這個要求。資料要求外部電容的ESR不能超過3Ω,同時要求在電容值為10μF時,電容的ESR不可小于20mΩ。設計中使用的10μF陶瓷電容,其ESR在工作頻段內僅為6mΩ,無法滿足要求。將該電容替換為10μF的鉭電容,其ESR在100kHz時為2Ω。替換后,1.5V電源上電正常。

【討論】

提到電容的ESR,設計者往往想到的都是其負面影響。的確,較大的ESR具有兩個不利因素。第一,根據電容損耗角正切值的定義,較大的ESR會產生較大的損耗功率P,如果P大到一定程度,且單板上該類型的電容器件數目較多時,形成預算就不得不考慮電容上的損耗,這往往是電子設計工程師最不希望看到的。第二,對于高速電路設計,往往希望電容的阻抗越小越好。這有兩個含義,一方面,對于高頻信號的交流耦合,電容串聯在高頻信號上,目的是隔斷高頻信號接收端的直流分量,同時又希望高頻信號的衰減越小越好,如果電容的ESR較大,對于交流耦合的高頻信號,相當于在信號中間串聯了一個不小的電阻,將產生一定的衰減;另一方面,對于并聯在電源和地之間的濾波電容,其作用是為噪聲等于擾信號提供一個極低阻抗的分流路徑,ESR較大的電容,顯然無法起到這個作用。對于高速電路,即使ESR很小的電容,其ESR值仍不能滿足低阻抗要求,因此,在重要的電源濾波電路上,往往需要并聯多個電容,以最大程度地降低ESR。

不過情況也有例外,本例中電容的ESR就被用于LDO芯片的高頻補償。其原理在于,當LDO電源的負載電流發生瞬時變化時,利用ESR能立即產生電壓波動,從而引起LDO電源反饋電路的動作,以便LDO電源針對負載變化做出快速的調整。

理解要點:

① 電容器件并不是純粹的電容,而是帶有ESR、ESL、Rleak等分量的小型電路。

② ESL取決于電容器的類型和封裝,ESR取決于工作溫度、頻率、導線電阻等。

③ 大多數情況下,電容器的ESR越小,電路性能越好,但也有例外,設計時需要根據器件的要求進行選擇。

3. 濾波電容阻抗隨頻率變化特性的分析

高速電路設計需要考慮高頻和低頻兩種噪聲,針對這兩種噪聲,應選取不同的濾波電容。“低頻噪聲選用大電容,高頻噪聲選用小電容”,這是許多工程師達成的共識。在實際工作中,這種說法并不完全正確。我們將就這點進行一些探討,以便加深對電容選型的理解。

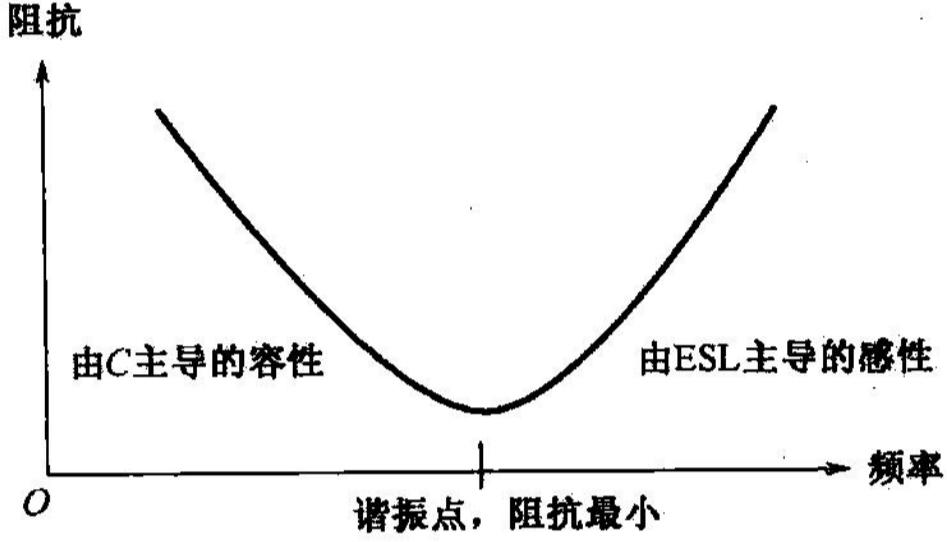

對電容器件而言,由于電容分量的存在,電容器的阻抗隨著頻率的升高而逐漸降低,這是電容器的本體屬性;ESL分量則使阻抗隨著頻率的升高而逐漸增加。這兩種作用正好相反。在電容分量和ESL分量的共同作用下,電容器的整體阻抗表現為,隨著頻率的升高,首先是電容分量起主導作用,使阻抗逐步變小,器件表現為電容的阻抗特性,濾波效果增強;當達到某一頻點時發生諧振,此時電容分量和ESL分量對阻抗的效果正好抵消,在諧振點上,電容器阻抗最小,等于ESR分量;此后,隨著頻率繼續升高,ESL分量起主導作用,使阻抗逐步增大,器件表現為電感的阻抗特性,濾波效果漸弱。濾波電容的作用機制是為噪聲等于擾提供一條低阻抗回路,在噪聲頻率點上,要求濾波電容的阻抗較小,即當噪聲頻率落在諧振點附近時,濾波效果最好。如下圖所示,諧振點由兩條曲線交會而成,左邊的曲線取決于電容器的容值C,右邊的曲線取決于電容器的ESL。由諧振頻率公式:F=ESLxC)^-1/2知,C和ESL越大,則諧振頻率越低,即電容對高頻干擾的濾波效果越差;C和ESL越小,諧振頻率越高,越適于濾除高頻干擾。

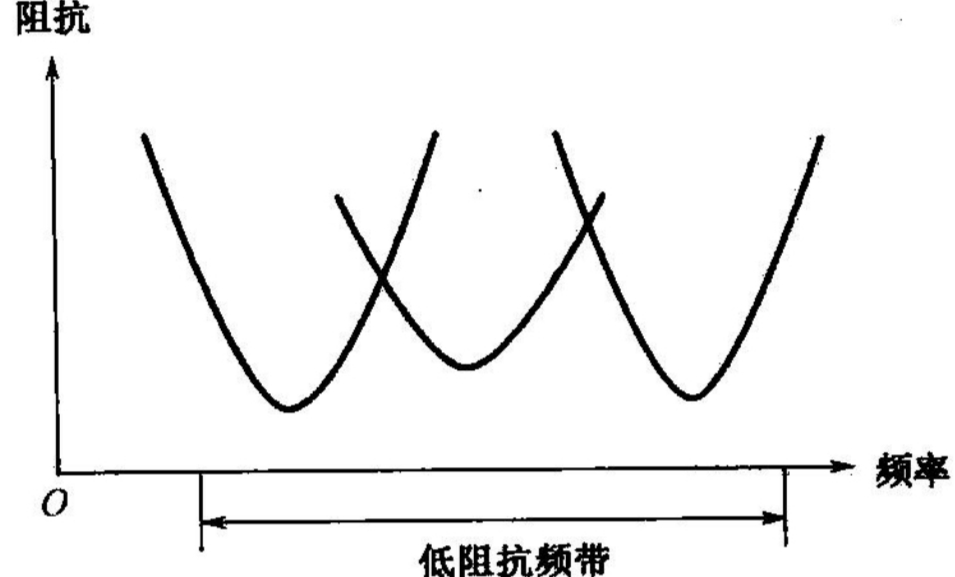

高速設計中,噪聲等于擾往往不是處在一個頻率點上,而是占據一段頻帶。在實際工作中,期望電路上每一處的噪聲頻帶都得到準確定位并分類,這就要求設計者在電路設計中,利用多種不同的電容構造一個比較寬的低阻抗頻帶,以盡可能地覆蓋噪聲頻帶。

如下圖所示,用三種電容并聯,其效果是構成一段比較寬的低阻抗頻帶。

【案例2.10】高頻電路中1μF+0.01μF是否能展寬低阻抗頻帶

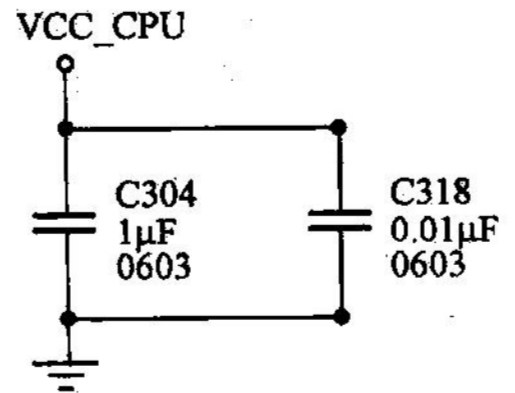

某單板使用0603封裝的1μF和0.01μF陶瓷電容各一個(下圖),為CPU片內鎖相環的電源濾波,設計者本意是利用兩種不同的電容達到展寬低阻抗頻帶的效果,但是這樣的設計是否能達到目的呢?

【討論】

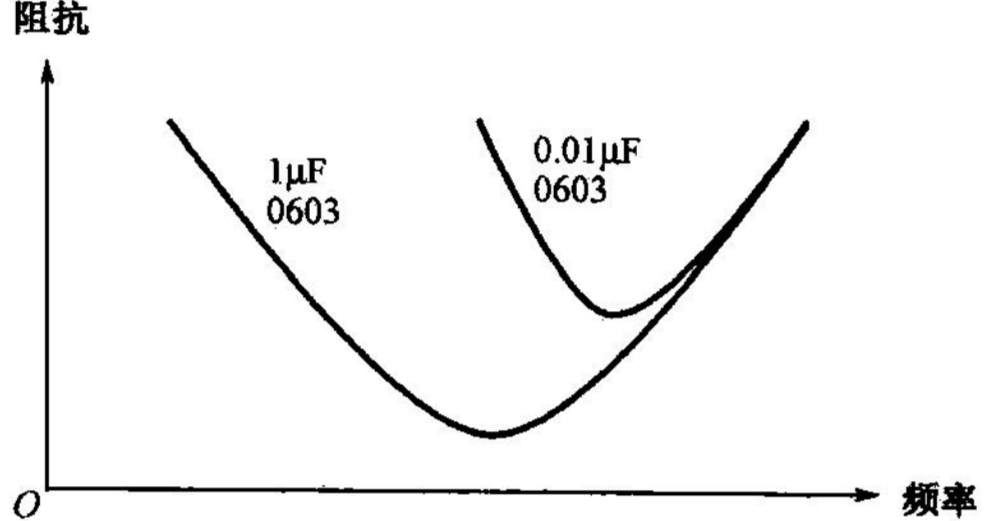

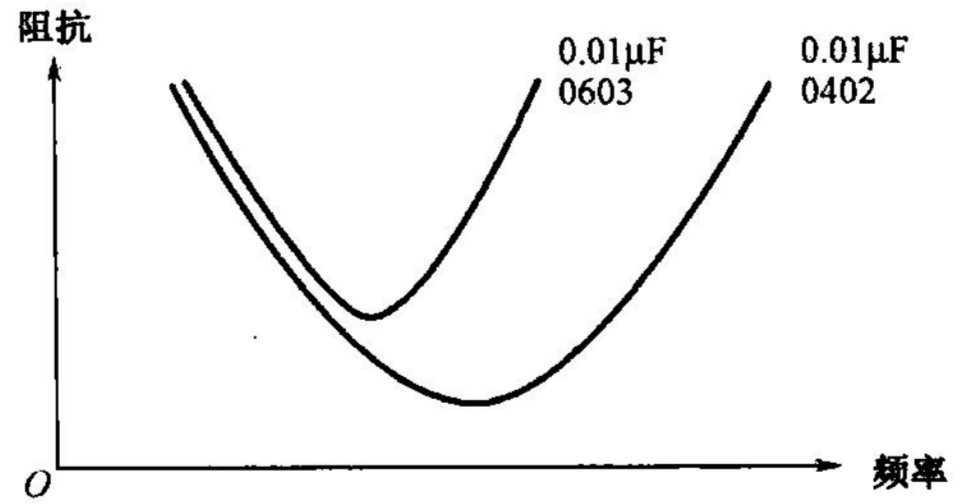

電容器的阻抗—頻率曲線由其電容分量和ESL分量共同決定,本例中的兩個電容容值不同,但類型和封裝都相同,因此ESL相同,并聯后的阻抗—頻率曲線如下圖所示,不能達到展寬低阻抗頻帶的目的。

針對本例,改進方法是,仍舊選擇1μF和0.01μF的陶瓷電容,不過封裝分別選取0603和0402,并聯后的阻抗—頻率曲線如下圖所示。

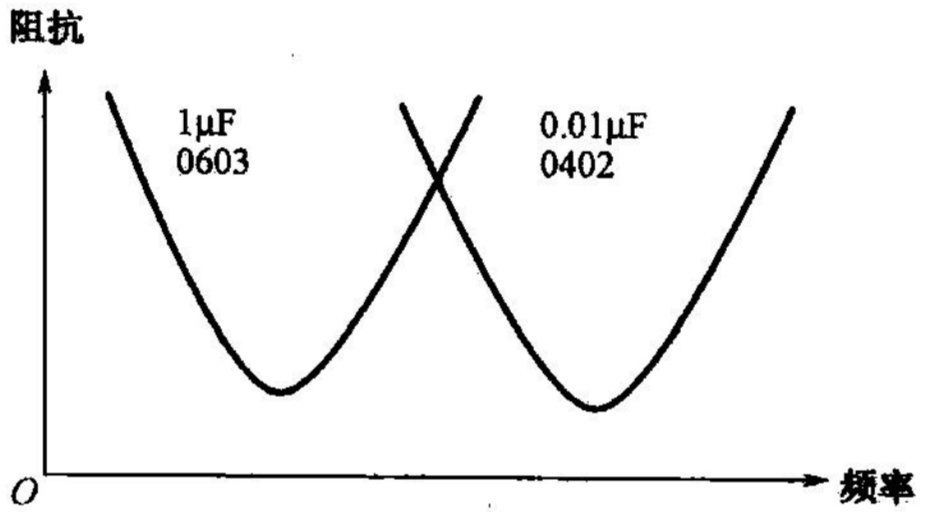

此處需做一些補充,設計者們常喜歡把若干相同的電容并聯在一起,共同為某電源濾波。這樣做的目的,一方面是起到去耦電容的本地“小池塘”作用(參見2.2.4節),另一方面是為了在諧振點上得到更低的阻抗。需要說明的是,這樣做,并沒有展寬低阻抗頻帶。其阻抗—頻率曲線如下圖所示。

下面來分析“低頻噪聲選用大電容,高頻噪聲選用小電容”這種說法。結合電容器的阻抗—頻率曲線圖,如果僅考慮電容器的電容分量,這種說法是正確的,因為電容分量越大,諧振點的頻率越低,適于濾除低頻噪聲,而電容分量越小,諧振點的頻率越高,適于濾除高頻噪聲。但如果同時考慮ESL分量,則未必正確,參見之前圖。0603封裝的0.01μF電容,其阻抗—頻率曲線完全被0603封裝的1μF電容的曲線包含,并沒有真正起到作用。

需要補充的是,當兩種電容器的類型與容值相同,只有封裝不同時,各自的阻抗—頻率曲線將如何表現?以0603和0402的0.01μF陶瓷電容為例,其阻抗—頻率曲線如下圖所示。顯然0402封裝的阻抗—頻率曲線能包含0603封裝的曲線。如果設計中將這兩種電容并聯后為同一電源濾波,除了降低濾波電路的阻抗外,0603封裝的電容其實沒有

?理解要點:

?理解要點:

① 電容器的阻抗—頻率變化曲線是一種洛益曲線。曲線的左邊取決于電容分量,右邊取決于ESL分量。

② 濾波電容并聯以展寬低阻抗頻帶時,不僅要考慮電容值搭配,還需要考慮封裝搭配。多個同型號的電容并聯時,雖不能展寬低阻抗頻帶,但可以減小諧振點處的阻抗。

2.2.3 高速電路設計常用電容及其應用要點

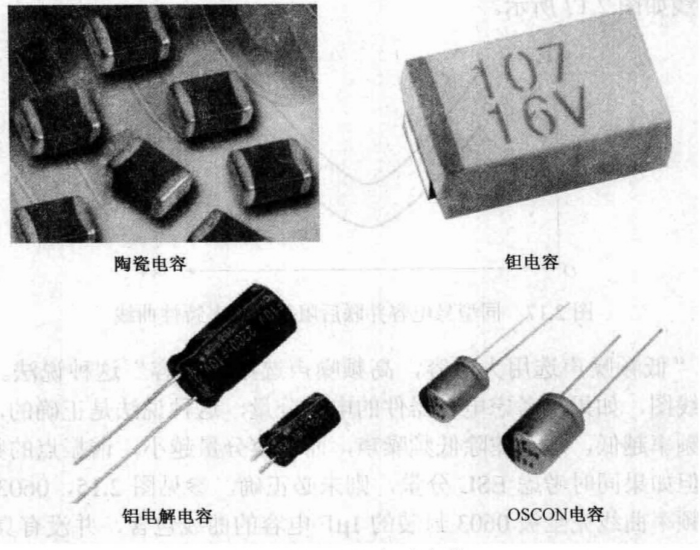

高速電路設計中最常用的電容有陶瓷電容(Ceramic Capacitor)、鉭電容(Tantalum Capacitor)、鋁電解電容(Aluminum Electrolytic Capacitor),以及最近開始流行的OSCON電容,如下圖所示。四種常用電容中,只有陶瓷電容是非極性電容,其他三種都屬于極性電容。

?1. 陶瓷電容及其應用要點

?1. 陶瓷電容及其應用要點

陶瓷電容是以陶瓷作為介質,在陶瓷的兩面噴涂金屬作為極板構成的,其優勢是體積小、價格低、穩定性好,但容量小。目前常用的陶瓷電容,其容值小的可以到幾十皮法,大的可以到幾十微法。

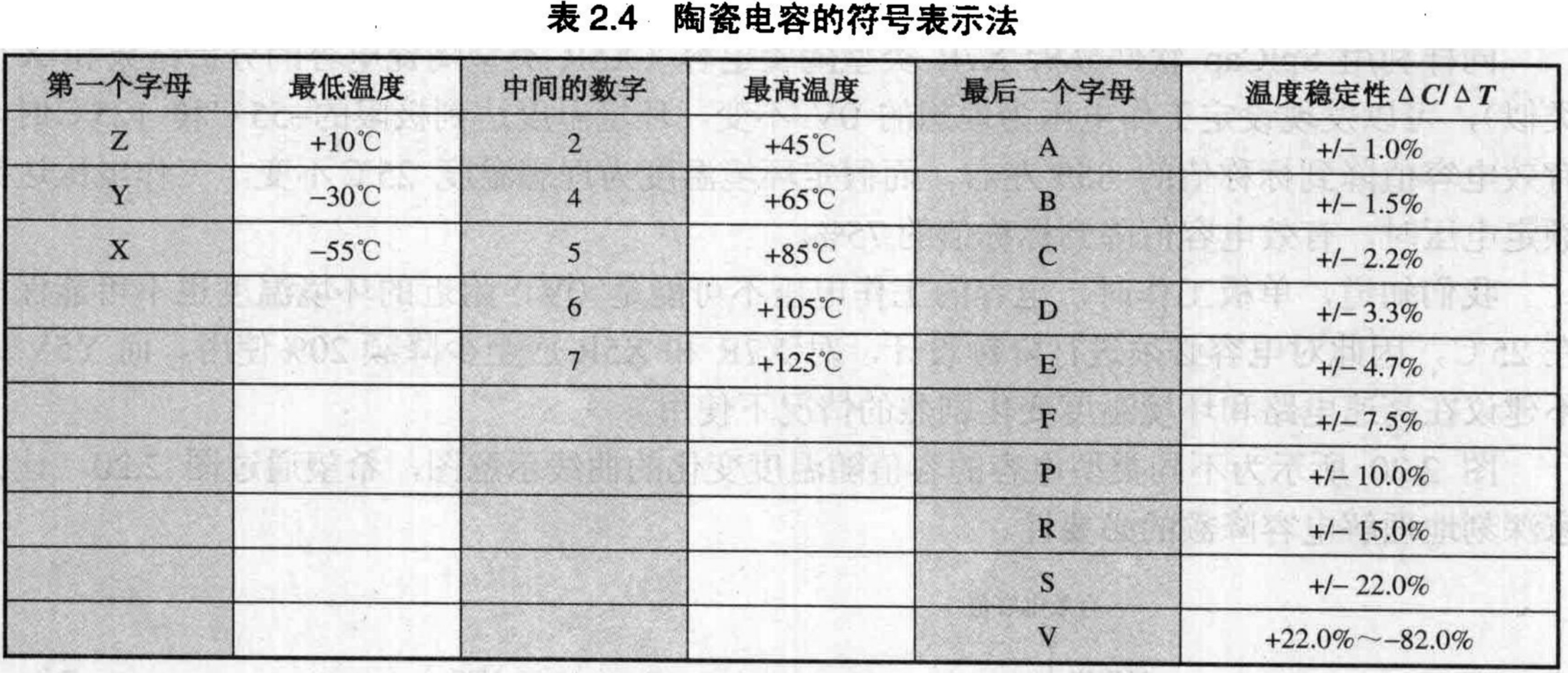

平時經常提到的X7R、X5R、Y5V等,就是陶瓷電容。那么這些符號的含義是什么?如下表所示為陶瓷電容的符號表示法。

高速電路設計中,常用到的陶瓷電容種類有NPO、X7R、X5R和Y5V。它們的區別主要在于填充介質不同,從而引起溫度、電壓穩定性的不同。

NPO是溫度補償型陶瓷電容,是電容量最穩定的一種陶瓷電容。工作溫度范圍為-55℃~+125℃,可以認為在這個范圍內,電容量基本保持不變。

X7R,表示工作溫度范圍為-55℃~+125℃,溫度穩定性為+/-15%的陶瓷電容。

X5R,表示工作溫度范圍為-55℃~+85℃,溫度穩定性為+/-15%的陶瓷電容。

Y5V,表示工作溫度范圍為-30℃~+85℃,溫度穩定性為+22%~-82%的陶瓷電容。

在高頻電路設計中,推薦選用NPO、X7R、X5R類型,盡量不選用Y5V類型。

【案例2.11】陶瓷電容選型錯誤導致單板丟數據包

某成熟的低端以太網交換機產品在進行降成本設計后,高溫55℃下測試丟包率時發現丟數據包。該問題只發生在降成本設計后的批次上,之前的產品批次均能正常工作。查詢改板記錄,發現設計人員為了節省成本,將單板上為交換芯片供電的電源的10μF濾波電容的類型由X7R更改為Y5V,電容廠家是AVX。根據廠家提供的軟件SpicCap,可以計算出在85℃時,電容容量僅為3.775μF,尚不到標稱容量值的40%。而在環境溫度55℃時,單板上該電容附近的溫度達到了近80℃,因此實際有效電容值相對標稱值大為減小,無法滿足濾波的要求,造成電源上噪聲過大。將電容類型更改為同容量的X7R后,問題得到解決。

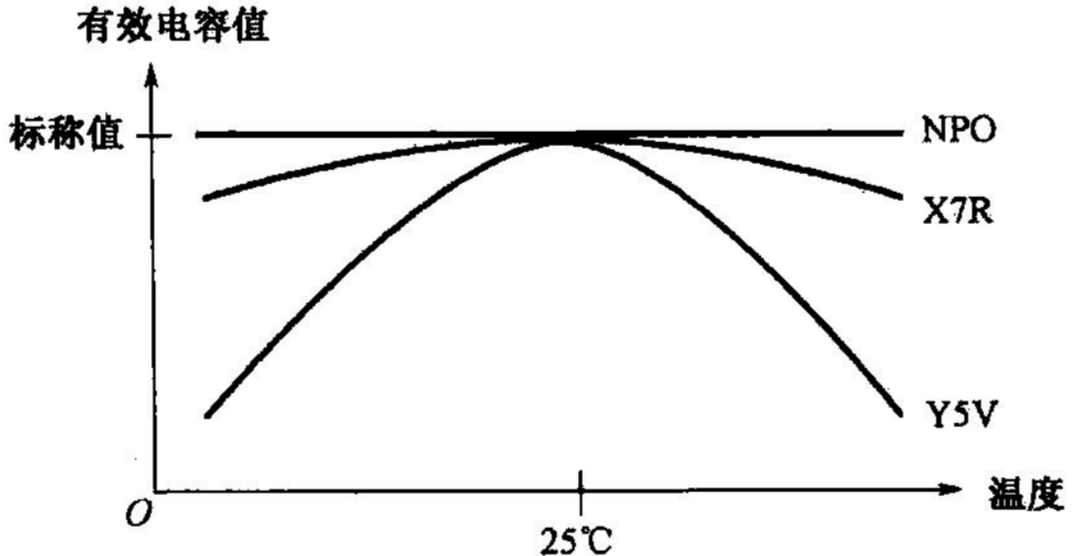

【討論】

對于X7R、X5R和Y5V這三種類型的陶瓷電容,標稱的電容量值都是在環境溫度25℃、工作電壓等于0V時得到的值。如果環境溫度和工作電壓發生改變,則有效電容值將會發生變化。三者的區別在于變化程度的不同,其中Y5V這種類型的電容,變化最為劇烈。

利用AVX公司的SpicCap軟件分析額定電壓10V、標稱值22μF的Y5V電容,理想狀態(即工作電壓0V,環境溫度25℃)下,有效值為標稱值(22μF)。如果保持其環境溫度為25℃不變,僅改變工作電壓,當工作電壓為5V時,有效電容值為4.4μF;當工作電壓達到額定電壓10V時,有效電容值僅為2.2μF。如果保持其工作電壓為理想的0V不變,僅改變環境溫度,可以發現當環境溫度相對于25℃升高和降低時,有效電容值都會減小,當環境溫度達到85℃時,有效電容值為8.36μF,為-30℃時,有效電容值為2.7μF。

同樣利用SpicCap軟件分析X7R類型陶瓷電容的分析結果和X7R類似),可以發現設定工作電壓為理想的0V不變,環境溫度達到額定的-55℃和125℃時,有效電容值降到標稱值的85%左右。而假定環境溫度為理想25℃不變,工作電壓達到額定電壓時,有效電容值降到標稱值的90%。

我們知道,單板工作時,電容的工作電壓不可能是0V,附近的環境溫度也不可能保持在25℃,因此對電容必須進行降額設計,對X7R和X5R應至少降額20%使用,而Y5V則不建議在高速電路和環境溫度變化劇烈的情況下使用。

下圖所示為不同類型電容的容值隨溫度變化的曲線示意圖,希望通過下圖,讓大家深刻地理解電容降額的必要性。

貼片式陶瓷電容的ESR一般都比較小,在高頻濾波中這是一個優勢,但有些時候,這也是一個劣勢,請參考案例2-9。

由于陶瓷電容容量一般都比較小,在高速電路的設計中,單獨使用陶瓷電容濾波是不適宜的,必須同時搭配使用鉭電容、鋁電解電容或者OSCON等類型的電容。

2. 鉭電容及其應用要點

鉭電容使用金屬鉭作為介質,基于鉭的固態特質,具有溫度特性好、ESL值小、高頻濾波性能好、體積小、節省PCB面積、容值較大等特點。因此鉭電容一般被應用在需要大容量電容濾波的場合,如為CPU等高耗能器件濾波。

鉭電容的缺點是耐電壓和耐電流的能力較弱。一般要求鉭電容的工作電壓相對額定電壓降額50%以上。遇到以下三種場合之一,鉭電容的額定電壓需降額70%以上使用:

(1)負載呈現較強的感性;

(2)串聯電阻小;

(3)瞬變電流較大。

其原因在于,感性負載或較小的串聯電阻會導致較大的瞬變電流,造成鉭電容的金屬鉭介質被擊穿。這使得在以下環節,鉭電容的失效概率增大:ICT測試、老化測試、系統開機瞬間、單板熱插拔瞬間。

?案例2-5中,在熱插拔子板的過程中,會產生較大的瞬變電流,而連接器附近電子板電源濾波的鉭電容電壓降額只有25%,沒有達到70%的要求,因此造成失效。

一般而言,容值越大的鉭電容,其ESR值往往越大。

下圖是摘取自AVX公司的鉭電容器件資料。10μF的鉭電容,其100kHz時的ESR最大值為1500mΩ;150μF的同系列鉭電容,ESR最大值僅為125mΩ。

?根據電容的等效電路,ESR相當于電容器件的串聯電阻,串聯電阻越小越容易造成電容失效。因此在應用中需要注意,對于大容量的電容,更需要電壓降額。從成本上來說,鉭電容的價格正比于容量和額定電壓的乘積,在使用大容量的鉭電容時,還需要增加電壓降額的比例,這勢必造成成本的上升。因而在設計中,往往將若干小容量的鉭電容并聯以提升大容量鉭電容相同的容量,這樣做,一方面有利于設計的可靠性,一方面也有利于成本的降低。

?根據電容的等效電路,ESR相當于電容器件的串聯電阻,串聯電阻越小越容易造成電容失效。因此在應用中需要注意,對于大容量的電容,更需要電壓降額。從成本上來說,鉭電容的價格正比于容量和額定電壓的乘積,在使用大容量的鉭電容時,還需要增加電壓降額的比例,這勢必造成成本的上升。因而在設計中,往往將若干小容量的鉭電容并聯以提升大容量鉭電容相同的容量,這樣做,一方面有利于設計的可靠性,一方面也有利于成本的降低。

需要注意,工作在瞬變電流較大的場合,鉭電容并不一定會發生失效。鉭電容本身有較好的自愈能力,只要外界環境的影響在一定范圍之內,鉭電容都能自我恢復。有時在單板的調試中會發現,單板突然莫名其妙地掉電,過一會兒后重新上電又能正常工作,有可能就是因為鉭電容暫時失效所致。因此,為了保證單板長期穩定的工作,必須嚴格執行鉭電容的電壓降額,同時在設計時需注意,在涉及熱插拔的電源濾波電路上,盡量避免使用鉭電容。

【案例2-12】根據電路要求進行鉭電容選型

某FPGA的I/O接口電源為1.8V,功耗0.9W,要求電源電壓的波動不超過5%。電源完整性仿真表明,其主要噪聲頻段將集中在100kHz~5MHz,根據以上需求選擇濾波電容的型號。

【討論】

由于噪聲頻帶集中在100kHz~5MHz,可初步判斷需要選擇鉭電容和陶瓷電容配合濾波,鉭電容主要濾除低頻段噪聲,陶瓷電容濾除高頻段噪聲。

該FPGA的I/O接口電源,最大電流為0.9W/1.8V=0.5A,假定其電流波動值ΔI不會超過最大電流的50%,即取ΔI=0.25A。

則該I/O接口電源的動態阻抗為Z=ΔV/ΔI=(1.8Vx5%)/0.25A=0.36Ω。

首先考慮低頻段的濾波,選用鉭電容,其ESL分量非常小,可以忽略,因此其阻抗主要由ESR和C構成,即ZCAP=|ESR+1/jωC|=(|ESR|^2+(1/ωC)^2)^1/2。

選擇AVX公司的22μF電容TPSB226M600,根據圖2.21所示器件資料,在100kHz時,其ESR最大值為0.6Ω,ZCAP=|0.36+1/(2x3.14x100x10^3x22x10^{-6})^2|^1/2=0.604Ω。

要求濾波電容的阻抗小于芯片動態阻抗,因此需兩片22μF電容并聯,并聯后阻抗為0.302Ω,小于動態阻抗,所以可以滿足低頻段濾波的要求。

其次,對于高頻段濾波,一般可以選用0402封裝、X5R類型、1μF的陶瓷電容。

結論,針對本例需求,設計上應采用2片22μF鉭電容TPSB226M600,與若干1μF陶瓷電容并聯(建議一個I/O接口電源引腳放置一個1μF陶瓷電容),為FPGA的I/O接口電源濾波。

高速電路中,噪聲頻段分布得比較廣泛,設計時需要將陶瓷電容和鉭電容配合起來共同完成濾波功能。

3. 鋁電解電容及其應用要點

鋁電解電容使用電解液作為介質,外殼的鋁制圓筒作為負極,內部插入一塊金屬板作為正極。鋁電容容量大、耐壓高,但溫度穩定性差、精度差、高頻濾波性能差,僅適用于低頻濾波。

在對鋁電容的介紹中提到,鋁電容不適用于有較大瞬變電流的場合,而在這種場合下,就需要用到鋁電解電容。例如,在單板的-48V緩啟動電路上,就需要用到鋁電解電容。

在應用中,鋁電解電容的電壓降額要求至少為20%。例如,在-48V緩啟動電路的濾波電路中,要求鋁電解電容的額定電壓60V以上。

鋁電解電容一般都是插裝式,因此ESR、ESL值都比較大,同時由于采用液體作為介質,在極高溫和極低溫環境下,性能也極不穩定。

案例2-4的硬盤停止工作的問題,就是一個典型的鋁電解電容在低溫下性能不穩定的案例。查詢鋁電解電容器件資料如下表所示。

上表中,第二、三欄分別提供了該電容在20℃和-10℃的ESR值,可以看出,在-10℃,鋁電解電容的ESR值相對常溫增大了一倍,而該案例的測試在-30℃進行,ESR相比-10℃時又會增大很多。即在-30℃,鋁電解電容的ESR值比常溫下的值可能大好幾倍,濾波性能大大降低。

從產品的長期穩定性來說,鋁電解電容也可能成為隱患。因為隨著產品使用時間的增加,鋁電解電容內部的電解液將逐漸干涸,容量逐漸減小,ESR逐漸增大,濾波效果減弱。所以在高速電路設計的電容選型中,應盡量避免選擇鋁電解電容。

4. OSCON電容及其應用要點

嚴格地說,OSCON并不是一種電容的類型,而是SANYO公司的一種性能比較好的電解電容的品牌。

OSCON電容外形酷似鋁電解電容,其優點在于,OSCON電容ESR較小、溫度穩定性相對鋁電解電容較好、價格相對鉭電容較低。缺點在于對絕大多數OSCON電容而言,引腳都是插裝形式,并且體積比較大。

在電路設計中,DC/DC電源的輸入和輸出部分往往需要布放大容量的鉭電容,成本較高。在這種情況下,可以同樣容值的OSCON電容取代,其成本僅為對應鉭電容的幾分之一。

5. 總結

本小節就高速電路設計中的常用電容類型做了詳細介紹,各種電容均有自己的優勢和劣勢,沒有哪一種類型能夠完全取代其他類型,因此在設計中,設計者們需要注意結合各種電容自身的特點,配合使用,以獲得最佳效果。

理解要點:

① 陶瓷電容體積小、價格低、穩定性好,但容量小,適用于高頻濾波。

② 鉭電容溫度穩定性好,ESL值小,高頻濾波性能好,體積小,能節省PCB面積,并且容量較大,但耐沖擊電壓和沖擊電流的能力較弱。

③ 鋁電解電容容量大,耐壓高,但溫度穩定性差,精度差,高頻濾波性能差,僅適用于低頻濾波。

④ 在電容應用中,應注意對阻抗—頻率特性曲線的理解。

2.2.4 去耦電容和旁路電容

在技術資料上,經常可以看到去耦(decouple)電容和旁路(bypass)電容這兩種名稱。它們都不是電容的類型,而是設計者根據電容所起的作用不同而進行的劃分。本小節不展開講解這兩種電容,只簡要介紹其作用。

去耦電容,其作用是為保證器件穩定工作而給器件電源提供的本地“小池塘”。在高速運行的器件上,會不斷產生迅速變化的電流需求,對于這種快速的需求,電源模塊無法及時給器件提供電流補充,只能依靠器件附近的電容給予解決。可以把電容理解成平抑濾波的小池塘,一旦小池塘附近的莊稼缺水,能立刻從小池塘得到補充,而無需求助遠方的水廠。去耦電容還有另一個作用,是為高速運行器件產生的高頻噪聲提供一條就近流入地平面的低阻抗路徑,以避免這些干擾影響該電源的其他負載。旁路電容,其作用是為前級(如電源產生的高頻噪聲等干擾)提供一條流到地平面的低阻抗路徑,以避免這些干擾影響正在高速工作的器件。

從以上描述可以看出,去耦電容和旁路電容沒有本質的區別,從應用上說,依據公式Z=1/(2πFxC),其中F是器件工作頻率,它們在高頻下的作用都是為電路中的干擾提供一條流回地平面的低阻抗回路。

![LINUX基礎 [四] - Linux工具](http://pic.xiahunao.cn/LINUX基礎 [四] - Linux工具)

:拾遺 - imgproc 基礎操作(上))

)