計算機組成原理——CPU與存儲器連接例題

設CPU共有16根地址線和8根數據線,并用(MREQ) ?作為訪存控制信號(低電平有效),(WR) ?作為讀/寫命令信號(高電平讀,低電平寫)。現有下列存儲芯片:1K4位RAM,4K8位RAM,2K*8位ROM,以及74138譯碼器和各種門電路,如下圖所示。畫出CPU和存儲芯片的連接圖。要求

(1) 主存地址空間分配:A000H ~ A7FFH為系統程序區;A800H ~ AFFFH為用戶程序區

(2) 合理選用上述存儲芯片,說明各選幾片

(3) 詳細畫出存儲芯片的片選邏輯

題目分析

1. CPU 和控制信號

- CPU:

- 16 根地址線 (A0~A15),尋址范圍 0000H~FFFFH(64KB)。

- 8 根數據線 (D0~D7)。

- 控制信號:

- (MREQ)?:訪存控制信號,低電平有效。

- (WR)?:讀/寫控制信號,高電平為讀,低電平為寫。

2. 存儲芯片

- 可選芯片:

- 1K×4 位 RAM(1024×4 位)。

- 4K×8 位 RAM(4096×8 位)。

- 2K×8 位 ROM(2048×8 位)。

- 工具:74138 譯碼器和各種門電路。

3. 地址空間分配

- 系統程序區:A000H~A7FFH(2KB)。

- 用戶程序區:A800H~AFFFH(2KB)。

4. 要求

- 合理選擇存儲芯片,說明選用幾片。

- 寫出每片存儲芯片的二進制地址范圍。

- 詳細畫出片選邏輯。

存儲芯片選擇與地址范圍

1. 地址空間分析

- 系統程序區 (A000H~A7FFH):

- A000H = 1010 0000 0000 0000。

- A7FFH = 1010 0111 1111 1111。

- 容量:A7FFH - A000H + 1 = 2KB(2048 字節)。

- A15~A11 = 10100,A10~A0 變化。

- 用戶程序區 (A800H~AFFFH):

- A800H = 1010 1000 0000 0000。

- AFFFH = 1010 1111 1111 1111。

- 容量:AFFFH - A800H + 1 = 2KB(2048 字節)。

- A15~A11 = 10101,A10~A0 變化。

2. 存儲芯片選擇

- 系統程序區 (2KB,ROM):

- 需要 2K×8 位 ROM,正好匹配。

- 選用 1 片 2K×8 位 ROM。

- 地址線:2K = 2048 = 2^11,需 A0~A10。

- 用戶程序區 (2KB,RAM):

- 需要 2KB,但沒有直接的 2K×8 位 RAM。

- 可選:

- 1K×4 位 RAM × 4 片,組合成 2K×8 位。

- 兩個 1K×4 位 RAM 組成 1K×8 位,兩個 1K×8 位再組成 2K×8 位。

- 4K×8 位 RAM × 1 片,僅用 2KB。

- 但浪費 2KB 容量,不夠經濟。

- 1K×4 位 RAM × 4 片,組合成 2K×8 位。

- 選用 4 片 1K×4 位 RAM,組合成 2K×8 位。

- 地址線:1K = 1024 = 2^10,單個 1K×4 位 RAM 需 A0~A9;兩組 1K×8 位共用 A10 區分。

3. 存儲芯片數量

- 1 片 2K×8 位 ROM。

- 4 片 1K×4 位 RAM。

4. 存儲芯片地址范圍

- 2K×8 位 ROM:

- A000H~A7FFH。

- 二進制:1010 0000 0000 0000 ~ 1010 0111 1111 1111。

- 1K×4 位 RAM × 4(組合成 2K×8 位):

- A800H~AFFFH。

- 分為兩組 1K×8 位:

- RAM1 和 RAM2 (A10 = 0):A800H~ABFFH。

- 二進制:1010 1000 0000 0000 ~ 1010 1011 1111 1111。

- RAM3 和 RAM4 (A10 = 1):AC00H~AFFFH。

- 二進制:1010 1100 0000 0000 ~ 1010 1111 1111 1111。

- RAM1 和 RAM2 (A10 = 0):A800H~ABFFH。

片選邏輯設計

1. 片選信號需求

- ROM:

- 地址范圍:A15~A11 = 10100。

- 片選條件:A15 = 1, A14 = 0, A13 = 1, A12 = 0, A11 = 0。

- RAM:

- 地址范圍:A15~A11 = 10101。

- 片選條件:A15 = 1, A14 = 0, A13 = 1, A12 = 0, A11 = 1。

- 細分:

- RAM1 和 RAM2:A10 = 0。

- RAM3 和 RAM4:A10 = 1。

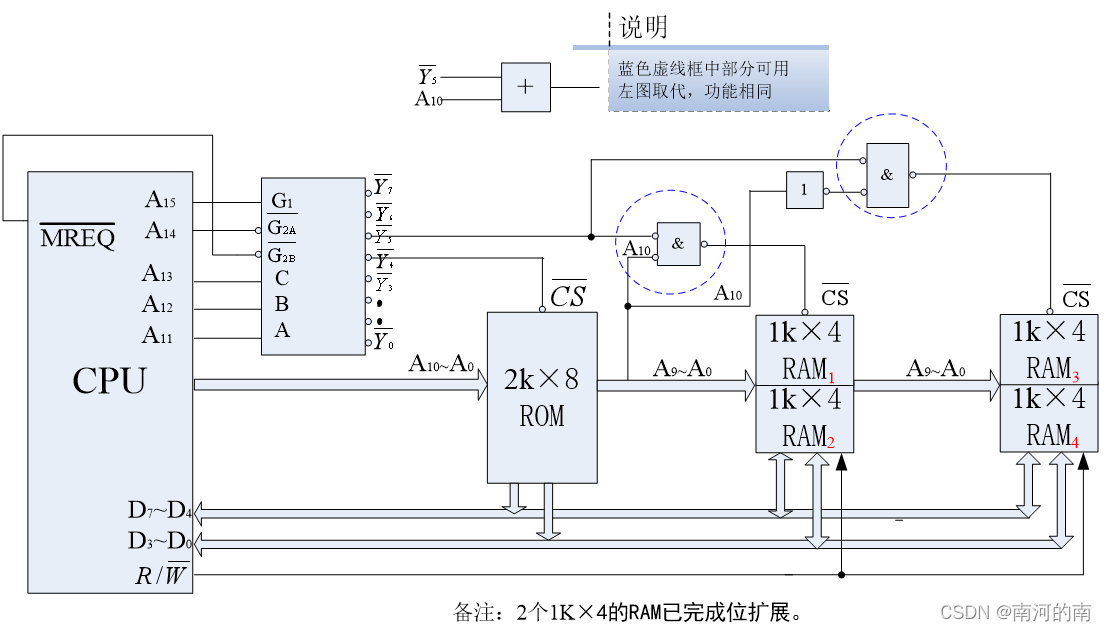

2. 74138 譯碼器連接

- 輸入:

- A = A11。

- B = A12。

- C = A13。

- 使能:

- G1 = A15(高電平有效)。

- G2A = (A14)?(低電平有效,需反相器)。

- G2B = (MREQ)?(低電平有效)。

- 輸出:

- Y4 (A13 A12 A11 = 100):A000H~A7FFH,接 ROM 的 CS?。

- Y5 (A13 A12 A11 = 101):A800H~AFFFH,接 RAM 的片選控制。

3. RAM 片選細分

- Y5 控制 A800H~AFFFH,需用 A10 進一步區分:

- RAM1 和 RAM2 的 CS?:Y5 AND (A10)?。

- RAM3 和 RAM4 的 CS?:Y5 AND A10。

4. RAM 讀寫控制

- RAM 寫使能 (WE)?:(MREQ)? AND (WR)?(需與門)。

- 讀操作:(WR)? = 1 時,RAM 輸出數據。

CPU 與存儲器連接圖設計

1. 地址線連接

- ROM:

- A0~A10 接 ROM 的地址引腳。

- RAM:

- RAM1RAM4:A0A9 接地址引腳。

- A10 用于片選區分。

2. 數據線連接

- ROM:

- D0~D7 接 ROM 的數據引腳。

- RAM:

- RAM1 和 RAM3:D0~D3。

- RAM2 和 RAM4:D4~D7。

3. 片選邏輯

- 74138 譯碼器:

- 輸入:A = A11, B = A12, C = A13。

- 使能:G1 = A15, G2A = (A14)?, G2B = (MREQ)?。

- 輸出:Y4 接 ROM CS?,Y5 接 RAM 片選。

- RAM 片選:

- RAM1 和 RAM2:Y5 AND (A10)?。

- RAM3 和 RAM4:Y5 AND A10。

4. 控制信號

- RAM (WE)?:(MREQ)? AND (WR)?。

連接圖描述

作圖如下:

以下是連接圖的文字描述:

-

CPU:

- A0~A15:地址線。

- D0~D7:數據線。

- (MREQ)? 和 (WR)?:控制信號。

-

2K×8 位 ROM:

- 地址:A0~A10。

- 數據:D0~D7。

- CS?:接 74138 的 Y4。

-

1K×4 位 RAM × 4:

- RAM1 和 RAM2(組成 1K×8 位):

- 地址:A0~A9。

- 數據:RAM1 (D0~D3),RAM2 (D4~D7)。

- CS?:Y5 AND (A10)?。

- RAM3 和 RAM4(組成 1K×8 位):

- 地址:A0~A9。

- 數據:RAM3 (D0~D3),RAM4 (D4~D7)。

- CS?:Y5 AND A10。

- WE?:(MREQ)? AND (WR)?。

- RAM1 和 RAM2(組成 1K×8 位):

-

74138 譯碼器:

- A = A11, B = A12, C = A13。

- G1 = A15, G2A = (A14)?(加反相器),G2B = (MREQ)?。

- Y4 接 ROM CS?。

- Y5 接兩個與門:

- 與門 1:Y5 AND (A10)? → RAM1 和 RAM2 的 CS?。

- 與門 2:Y5 AND A10 → RAM3 和 RAM4 的 CS?。

-

與門(RAM 寫控制):

- 輸入:(MREQ)? 和 (WR)?。

- 輸出:接 RAM1~RAM4 的 WE?。

回答總結

-

存儲芯片選擇:

- 1 片 2K×8 位 ROM。

- 4 片 1K×4 位 RAM。

-

二進制地址范圍:

- ROM:1010 0000 0000 0000 ~ 1010 0111 1111 1111 (A000H~A7FFH)。

- RAM1 和 RAM2:1010 1000 0000 0000 ~ 1010 1011 1111 1111 (A800H~ABFFH)。

- RAM3 和 RAM4:1010 1100 0000 0000 ~ 1010 1111 1111 1111 (AC00H~AFFFH)。

-

片選邏輯:

- 74138 譯碼器:

- 輸入:A11, A12, A13。

- 使能:A15, (A14)?, (MREQ)?。

- Y4 控制 ROM。

- Y5 結合 A10 控制 RAM:

- Y5 AND (A10)? → RAM1 和 RAM2。

- Y5 AND A10 → RAM3 和 RAM4。

- 74138 譯碼器:

拓展知識:片選原理

什么是片選?

片選(Chip Select, 簡稱 CS)是存儲器系統中用來選擇某個存儲芯片的控制信號。CPU 通常會連接多個存儲芯片(如 ROM 和 RAM),但在某一時刻,CPU 只會與一個存儲芯片進行通信(讀或寫數據)。片選信號的作用就是“激活”某個存儲芯片,讓它與 CPU 通信,而其他芯片保持“未選中”狀態。

- 片選信號:通常用 CS 或 CE(Chip Enable)表示,低電平有效時(CS? = 0),芯片被選中;高電平(CS? = 1)時,芯片未被選中。

- 片選的本質:通過地址線和控制信號,判斷當前 CPU 訪問的地址屬于哪個存儲芯片的范圍,從而激活對應的芯片。

片選的原理

1. 為什么需要片選?

- CPU 有 16 根地址線,可以尋址 64KB 的地址空間(0000H~FFFFH)。

- 但存儲器系統由多個芯片組成,每個芯片只占用一部分地址空間。例如:

- ROM:A000H~A7FFH(2KB)。

- RAM:A800H~AFFFH(2KB)。

- 當 CPU 訪問某個地址時(比如 A500H),需要判斷這個地址屬于哪個芯片的范圍:

- A500H 屬于 ROM(A000H~A7FFH),所以選中 ROM。

- 如果訪問 AC00H,屬于 RAM(A800H~AFFFH),則選中 RAM。

- 片選信號通過地址線的高位部分來判斷地址范圍,并生成對應的控制信號。

2. 片選信號如何生成?

- 地址解碼:通過地址線的高位部分,判斷當前地址屬于哪個芯片的范圍。

- 例如,A000H~A7FFH 的高位 A15~A11 = 10100,A800H~AFFFH 的高位 A15~A11 = 10101。

- 譯碼器:使用譯碼器(如 74138)將高位地址解碼,生成片選信號。

- 控制信號:結合 CPU 的控制信號(如 (MREQ)?),確保只有在訪存時才激活片選。

3. 片選的實現

- 硬件實現:通過譯碼器(如 74138)和邏輯門(如與門、或門)生成片選信號。

- 邏輯條件:

- 某個芯片被選中時,其 CS? = 0。

- 條件:當前地址在該芯片的范圍內,且 CPU 正在訪問存儲器((MREQ)? = 0)。

結合題目解釋片選原理

1. 存儲芯片和地址范圍

- ROM:2K×8 位,A000H~A7FFH。

- 2KB = 2048 字節,地址線 A0~A10(2^11 = 2048)。

- 高位:A15~A11 = 10100。

- RAM:4 片 1K×4 位 RAM,組合成 2K×8 位,A800H~AFFFH。

- 2KB,地址線 A0~A10。

- 高位:A15~A11 = 10101。

- 細分:

- RAM1 和 RAM2(1K×8 位):A800H~ABFFH,A10 = 0。

- RAM3 和 RAM4(1K×8 位):AC00H~AFFFH,A10 = 1。

2. 片選信號的生成

(1) 判斷地址范圍

- ROM:

- A15~A11 = 10100。

- 條件:A15 = 1, A14 = 0, A13 = 1, A12 = 0, A11 = 0。

- RAM:

- A15~A11 = 10101。

- 條件:A15 = 1, A14 = 0, A13 = 1, A12 = 0, A11 = 1。

- 細分:

- RAM1 和 RAM2:A10 = 0。

- RAM3 和 RAM4:A10 = 1。

(2) 使用 74138 譯碼器

- 74138 是一個 3-8 譯碼器:

- 輸入:A, B, C(3 位輸入)。

- 輸出:Y0~Y7(8 個輸出,低電平有效)。

- 使能:G1(高電平有效),G2A 和 G2B(低電平有效)。

- 連接方式:

- 輸入:A = A11, B = A12, C = A13。

- 使能:

- G1 = A15(A15 = 1 時,地址在 8000H~FFFFH)。

- G2A = (A14)?(A14 = 0 時,地址在 8000H~BFFFH)。

- G2B = (MREQ)?(訪存時有效)。

- 輸出:

- 當 A15 = 1, A14 = 0, (MREQ)? = 0 時,74138 工作。

- Y4 (A13 A12 A11 = 100):對應 A000H~A7FFH,接 ROM 的 CS?。

- Y5 (A13 A12 A11 = 101):對應 A800H~AFFFH,接 RAM 的片選控制。

(3) RAM 的片選細分

- Y5 控制整個 A800H~AFFFH(2KB),但 RAM 分為兩組(每組 1K×8 位),需要用 A10 進一步區分:

- RAM1 和 RAM2(A800H~ABFFH):A10 = 0。

- CS? = Y5 AND (A10)?。

- RAM3 和 RAM4(AC00H~AFFFH):A10 = 1。

- CS? = Y5 AND A10。

- RAM1 和 RAM2(A800H~ABFFH):A10 = 0。

- 這里需要兩個與門:

- 與門 1:輸入 Y5 和 (A10)?,輸出接 RAM1 和 RAM2 的 CS?。

- 與門 2:輸入 Y5 和 A10,輸出接 RAM3 和 RAM4 的 CS?。

3. 片選的工作過程

-

例子 1:CPU 訪問地址 A500H:

- A500H = 1010 0101 0000 0000。

- A15~A11 = 10100,符合 ROM 范圍。

- 74138:

- A15 = 1, A14 = 0, (MREQ)? = 0,譯碼器使能。

- A13 A12 A11 = 100,Y4 = 0。

- ROM 的 CS? = 0,ROM 被選中。

- Y5 = 1,RAM 未選中。

- CPU 通過 A0~A10(0101 0000 0000)訪問 ROM 內的具體地址。

-

例子 2:CPU 訪問地址 A900H:

- A900H = 1010 1001 0000 0000。

- A15~A11 = 10101,符合 RAM 范圍。

- 74138:

- A15 = 1, A14 = 0, (MREQ)? = 0,譯碼器使能。

- A13 A12 A11 = 101,Y5 = 0。

- Y4 = 1,ROM 未選中。

- Y5 = 0:

- A10 = 0,Y5 AND (A10)? = 0,RAM1 和 RAM2 的 CS? = 0,被選中。

- A10 = 0,Y5 AND A10 = 1,RAM3 和 RAM4 未選中。

- CPU 通過 A0~A9(001 0000 0000)訪問 RAM1 和 RAM2 內的具體地址。

片選的硬件實現

1. 74138 譯碼器

- 作用:將高位地址(A13~A11)解碼,生成 ROM 和 RAM 的片選信號。

- 連接:

- A = A11, B = A12, C = A13。

- G1 = A15, G2A = (A14)?, G2B = (MREQ)?。

- Y4 接 ROM 的 CS?。

- Y5 用于 RAM 的片選。

2. 邏輯門

- RAM 的片選需要細分:

- 用兩個與門結合 Y5 和 A10:

- Y5 AND (A10)? → RAM1 和 RAM2。

- Y5 AND A10 → RAM3 和 RAM4。

- 用兩個與門結合 Y5 和 A10:

- (A10)? 需要一個反相器生成。

3. 讀寫控制

- RAM 還需要讀寫控制:

- 寫使能 (WE)?:(MREQ)? AND (WR)?(用一個與門生成)。

- 讀操作:(WR)? = 1 時,RAM 輸出數據。

總結:片選的要點

- 片選的核心:通過地址解碼,判斷當前地址屬于哪個芯片的范圍,生成對應的 CS? 信號。

- 地址解碼:用高位地址(A15~A11)區分 ROM 和 RAM,A10 進一步細分 RAM。

- 譯碼器作用:74138 譯碼器將高位地址解碼為片選信號。

- 控制信號:結合 (MREQ)? 確保只有訪存時才激活片選。

題目中的片選邏輯(詳細說明)

1. ROM 片選

- 條件:A15 = 1, A14 = 0, A13 = 1, A12 = 0, A11 = 0, (MREQ)? = 0。

- 74138 輸出:Y4 = 0 時,ROM 被選中。

2. RAM 片選

- 條件:A15 = 1, A14 = 0, A13 = 1, A12 = 0, A11 = 1, (MREQ)? = 0。

- 74138 輸出:Y5 = 0。

- 細分:

- RAM1 和 RAM2:Y5 AND (A10)? = 0 時選中。

- RAM3 和 RAM4:Y5 AND A10 = 0 時選中。

3. 連接圖中的片選部分

- 74138 譯碼器:

- 輸入:A11, A12, A13。

- 使能:A15, (A14)?, (MREQ)?。

- 輸出:Y4 → ROM,Y5 → RAM。

- 與門:

- Y5 AND (A10)? → RAM1 和 RAM2。

- Y5 AND A10 → RAM3 和 RAM4。

再次結合題目總結

- 片選邏輯:

- ROM:Y4 直接控制。

- RAM:Y5 結合 A10 控制,分為兩組。

- A10 的作用:A10 用于區分 RAM 的兩個 1K×8 位塊(A800H~ABFFH 和 AC00H~AFFFH)。

- 74138 的作用:將 A15~A11 解碼,生成 ROM 和 RAM 的片選信號。

)

并發部署DeepSeek-V3-0324模型)

平滑處理的實現)

)

)

(字符串))