簡介

The AMD LogiCORE?IP Aurora 64B/66B core是一種可擴展的輕量級高數據速率鏈路層協議,用于高速串行通信。該協議是開放的,可以使用AMD設備技術實現。

Aurora 64B/66B是一種輕量級的串行通信協議,適用于多千兆位鏈路 (如下圖所示)。它用于使用一個或多個GTX、GTH或GTY收發器在設備之間傳輸數據。連接可以是全雙工 (兩個方向的數據) 或單工 (任一方向的數據)。

Aurora 64B/66B信道概覽

Aurora 64B/66B內核在連接到Aurora64B/66B渠道合作伙伴時會自動初始化渠道。初始化后,應用程序可以通過通道傳遞數據作為幀或數據流。Aurora 64B/66B框架可以是任何尺寸。高優先級請求能夠在任何時間中斷這些幀。有效數據字節之間的間隙會自動填充閑置,以保持鎖定并防止過多的電磁干擾。流控制在Aurora 64B/66B中是可選的,可用于限制linkpartner的傳輸數據速率,或通過通道發送簡短的高優先級消息。流在Aurora 64B/66B中實現為單個無休止的幀。每當數據未被發送時,發送閑置以保持鏈路存活。過多的位錯誤、斷開連接或設備故障會導致內核重置并嘗試初始化新通道。Aurora 64B/66B核心可以支持多通道信道的接收中的最多兩個符號偏斜。Aurora 64B/66B協議使用64B/66B編碼。與8B的25% 開銷相比,64B/66bencoding具有非常低 (3%) 的傳輸開銷,因此理論上可以提高性能。

Aurora 64B/66B核心框圖

通道邏輯: 通道邏輯模塊的實例驅動每個GT收發器。該通道邏輯初始化每個單獨的收發器,處理控制字符的編碼和解碼,并執行錯誤檢測

通道邏輯: 通道邏輯模塊的實例驅動每個GT收發器。該通道邏輯初始化每個單獨的收發器,處理控制字符的編碼和解碼,并執行錯誤檢測。

全局邏輯: 內核中的全局邏輯模塊執行用于通道初始化的通道綁定。在操作期間,通道跟蹤由Aurora 64B/66B協議定義的未就緒空閑特性,并監視所有通道邏輯模塊的錯誤。

RX用戶界面: AXI4-Stream接收 (RX) 用戶界面將數據從通道移動到應用程序,并執行流量控制功能。

TX用戶界面: AXI4-Stream傳輸 (TX) 用戶界面將數據從應用程序移動到信道,并執行流量控制TX功能。標準時鐘補償模塊嵌入在核心內部。該模塊控制時鐘補償 (CC) 的周期性傳輸。

核操作的最大頻率取決于支持的線路速率和設備的速度等級。

吞吐量:Aurora 64B/66B核心吞吐量取決于收發器的數量、收發器類型和所選收發器的目標線路速率。對于GTH收發器,吞吐量分別從單通道設計到16通道設計的0.48 Gbps到254.06 Gbps不等。note:為了在使用VIVADO的默認合成策略時獲得更好的定時性能,請將線路速率從IP/收發器支持的最大線路速率降低約30%。當啟用CRC_MODE時,將線路速率降低50%。使用另一種合適的合成策略,用戶可以實現IP中支持的最大線路速率。?

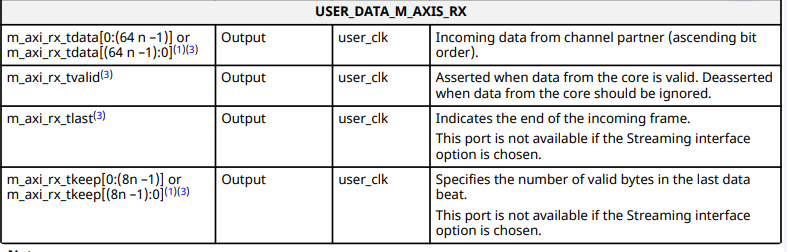

端口說明:

頂層文件實例化Aurora 64B/66B lanemodule、TX和RX AXI4-Stream模塊、全局邏輯模塊以及GTX、GTH、orGTY收發器包裝器。此頂級包裝文件在示例設計文件中與時鐘、復位電路、幀生成器和檢查器模塊一起實例化。

下圖顯示了Aurora 64B/66B AXI4-Stream數據接口位排序的n字節示例。

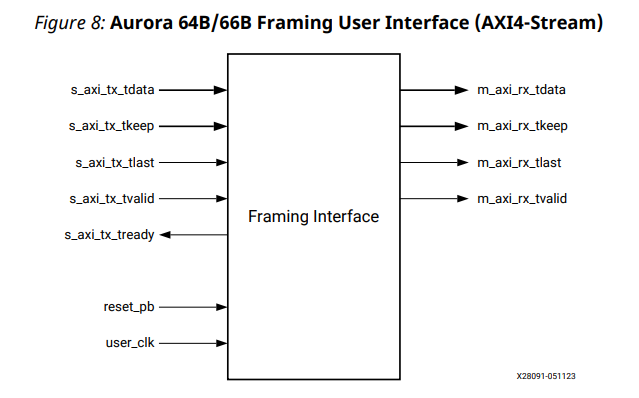

成幀用戶界面 (如下圖所示) 符合AMBA AXI4-StreamProtocol規范 (ARM IHI 0051A),并包含發送和接收成幀用戶數據所需的信號。成幀接口的詳細描述如下。

僅當s_axi_tx_tready和s_axi_tx_tvalid均被斷言時,Aurora 64B/66B核心才對數據進行采樣。用戶應用程序可以在任何時鐘周期 (帶暫停的數據傳輸) 取消斷言s_axi_tx_tvalid,以忽略該周期的AXI4-Stream輸入。如果這發生在幀的中間,則通過Aurora 64B/66B信道發送空閑符號。AXI4-Stream數據僅在成幀時有效。忽略幀外的數據。要結束aframe,當數據的最后一個字 (或部分字) 在thes_axi_tx_tdata端口上時,斷言s_axi_tx_tlast,并使用s_axi_tx_tkeep指定最后數據節拍中的有效字節數。(就是AXI-S的傳輸模式)

在framing中,每個幀以數據塊開始,并以包含幀的最后字節的分隔符塊結束。每當數據不可用時,就插入空閑塊。塊是8個字節的加擾數據或具有2位控制報頭 (總共66位) 的控制信息。

(幀傳輸過程為AXI傳輸模式大致一致,具體內容在file:///D:/NKUiversity/相關論文/xilinx資料/pg074-aurora-64b66b-en-us-12.0.pdf。16-20頁,之后有成幀效率)

流接口:

流接口 (如下圖所示) 允許在沒有幀分隔符的情況下進行數據傳輸,因此操作簡單,同時使用的資源比framing interface少。

在數據流中,Aurora 64B/66B通道用作管道。流式Aurora 64B/66Binterface期望填充整個s_axi_tx_tdata端口寬度 (八個字節的整數倍) 的數據。當s_axi_tx_tvalid被取消斷言時,除傳輸時鐘補償序列外,在保留的字之間會產生間隙。

當數據到達Aurora 64B/66B通道的RX端時,如果不立即讀取,則會丟失。如果這是不可接受的,則必須將緩沖器連接到RX接口以保存數據,直到可以使用。

下圖顯示了一個典型的流數據傳輸,開始時沒有斷言兩個就緒信號,以表明用戶邏輯和核心都沒有準備好傳輸數據。

在下一個時鐘周期中,內核通過斷言s_axi_tx_tready表示它已準備好傳輸數據。一個周期后,用戶邏輯斷言s_axi_tx_tvalid信號,并將數據放在s_axi_tx_tdata總線上,表明它已準備好傳輸數據。因為現在兩個信號都被斷言了,所以如下圖所示的數據0從用戶邏輯傳輸到核心。數據1按以下時鐘周期傳輸。在本例中,內核釋放它的就緒信號s_axi_tx_treready,并且直到下一個時鐘周期才傳輸數據。當再次斷言s_axi_tx_tready信號時,用戶應用程序在下一個時鐘周期取消斷言s_axi_tx_tvalid,并且在斷言兩個信號之前不傳輸數據。

下圖顯示了一個典型的流數據接收示例,可以看到,在rx_valid有效的時候才會接收數據

時鐘接口:

參考gtx收發器

流量控制接口:

狀態、控制和收發器接口:

Aurora 64B/66B核心的狀態和控制端口允許用戶應用程序監控通道并使用GTX、GTH和GTY收發器的內置功能。介紹狀態接口、控制接口、收發模塊串口的示意圖和端口說明。DRP接口允許通過符合AXI4-Lite協議或本機動態重新配置端口(DRP)接口讀取和更新串行收發器參數和設置

? ?(接口說明在page 38-41)主要是動態重新配置高速收發器

? ?(接口說明在page 38-41)主要是動態重新配置高速收發器

reset_pb:?按鈕重置。在example design 中作為的top層重置輸入。驅動內核內部的支持重置邏輯所需。

pma_init:收發器PMA_INIT復位信號通過一個無抖動器連接到頂層。系統地重置收發器的所有物理編碼子層(PCS)和物理介質附件(PMA)子組件。信號使用init_clk_in去抖動至少6個init_clk周期。有關詳細信息,請參閱相關收發器用戶指南中的重置部分。

可以理解為這兩個信號都是復位信號。

drp_clk_in:用戶可配置的參數僅適用到 7 系列 FPGA 設計。默認值為100兆赫。drp_clk頻率可以從50 MHz 至 x MHz,其中 x 是設備和速度取決于等級。

init_clk_in:信號用于注冊和去抖動pma_init信號。首選的init_clk范圍是50 ~ 200mhz。核心設置的默認init_clk頻率為50mhz,用于7系列設計,

note:收發器控制和狀態接口中的端口必須按照相應的GT用戶指南進行驅動。使用表12所示的輸入信號:收發器控制和狀態接口端口使用不當可能會導致IP核的不可預知行為

auror64B/66B內核中的錯誤信號:

設備問題和通道噪聲可能導致極光64B/66B通道運行錯誤。64B/66B編碼方法允許Aurora 64B/66B核心檢測信道中發生的位錯誤。內核通過在檢測到這些錯誤的每個周期中斷言soft_err信號來報告這些錯誤。

該核心還監視每個高速串行GTX和GTH收發器的硬件錯誤,如緩沖區溢出和鎖丟失。通過斷言hard_err信號來報告硬件錯誤。災難性的硬件錯誤也可以表現為軟錯誤的爆發。Aurora 64B/66B協議規范(SP011)中描述的塊同步算法決定是否將軟錯誤突發視為硬錯誤。

無論何時檢測到硬錯誤,內核都會自動重置自身并嘗試重新初始化。在大多數情況下,當導致硬錯誤的硬件問題得到解決時,這允許重新建立Aurora 64B/66B通道。軟錯誤不會導致重置,除非在短時間內出現某些觸發塊同步狀態機的錯誤。

硬錯誤:1.TX溢出/下流:TX數據彈性緩沖區存在溢出或下流情況。當用戶時鐘和參考時鐘源不在同一頻率上工作時,就會出現這種情況。2.RX溢出/下流:RX數據時鐘校正和通道綁定FIFO存在溢出或下流情況。當兩個通道伙伴的時鐘源頻率不在±100ppm范圍內時,就會出現這種情況

軟錯誤:短時間內發生的軟錯誤太多。1.如果檢測到太多無效同步標頭,對齊塊同步狀態機將自動嘗試重新對齊。軟錯誤不會轉化為硬錯誤。2.無效的同步頭:64位塊上的2位頭不是有效的控制頭或數據頭。3.無效的同步頭:64位塊上的2位頭不是有效的控制頭或數據頭。

初始化:

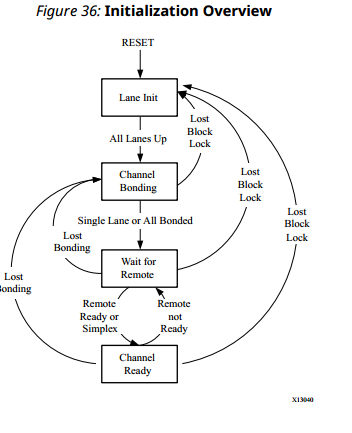

上電、復位、硬錯誤后,內核自動初始化(下圖)。通道兩側的核心模塊執行Aurora 64B/66B初始化過程,直到通道準備好使用。lane_up總線指示通道中的哪些通道已經完成了過程的通道初始化部分。lane_up信號可以用來幫助調試多通道信道中的設備問題。Channel_up只有在核心完成整個初始化過程之后才會斷言。

Aurora 64B/66B內核可以在斷言channel_up之前接收數據。應該只使用用戶界面m_axi_rx_tvalid信號來限定傳入的數據。因為在斷言channel_up之后才會發生傳輸,所以channel_up可以反轉并用于重置驅動全雙工信道的TX端的模塊。如果用戶應用模塊需要在接收數據之前復位,則可以使用反向lane_up信號來實現此目的。在所有的lane_up信號被斷言之前,數據不能被接收。

時鐘:

良好的時鐘對64B/66B核心的正確運行至關重要。核心需要一個低抖動參考時鐘來驅動GTX、GTH或GTY收發器中的高速TX時鐘和時鐘恢復電路。核心還需要至少一個鎖定頻率的并行時鐘,以便與用戶應用程序進行同步操作。時鐘架構圖:

gt_refclk (clkp/clkn)是一個專用的外部時鐘,由振蕩器生成,并通過專用的IBUFDS提供。

時鐘接口具體與開發板的連接還需要熟悉。明天再看看GTX收發器

(本文僅對用賽靈思手冊的前半部分,后部分有IP核GUI頁面的說明解釋,調試以及遷移應用等,較為全面,暫時用不到,僅做學習之用)

加:

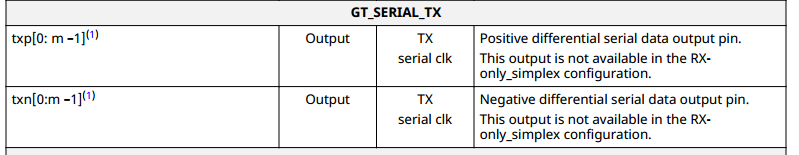

? ? 正/負差分串行數據輸出引腳。

? ? 正/負差分串行數據輸出引腳。

Q AND A:

1.drp_clk是用來設置參數進行調試用,和gt_ref_clk無關(大概是這個意思)

2.采用init_clk 與開發板上的時鐘沒有關系,50mhz是允許最低的時鐘頻率,有最低的功耗,開發板上的時鐘是提供給fpga一個時鐘源。fpga內部自己可以規定時鐘。

與usememo())

用法詳解)