?個人名片:

🎓作者簡介:嵌入式領域優質創作者

🌐個人主頁:妄北y📞個人QQ:2061314755

💌個人郵箱:[mailto:2061314755@qq.com]

📱個人微信:Vir2025WBY🖥?個人公眾號:科技妄北

🖋?本文為妄北y原創佳作,獨家首發于CSDN🎊🎊🎊

💡座右銘:改造世界固然偉大,但改造自我更為可貴。

專欄導航:

妄北y系列專欄導航:

物聯網嵌入式開發項目:大學期間的畢業設計,課程設計,大創項目,各種競賽項目,全面覆蓋了需求分析、方案設計、實施與調試、成果展示以及總結反思等關鍵環節。📚💼💡

QT基礎入門學習:對QT的基礎圖形化頁面設計進行了一個簡單的學習與認識,利用QT的基礎知識進行了翻金幣小游戲的制作。🛠?🔧💭

Linux基礎編程:初步認識什么是Linux,為什么學Linux,安裝環境,進行基礎命令的學習,入門級的shell編程。🍻🎉🖥?

深耕Linux應用開發:分享Linux的基本概念、命令行操作、文件系統、用戶和權限管理等,網絡編程相關知識,TCP/IP 協議、套接字(Socket)編程等,可以實現網絡通信功能。常見開源庫的二次開發,如libcurl、OpenSSL、json-c、freetype等💐📝💡

Linux驅動開發:Linux驅動開發是Linux系統不可或缺的組成部分,它專注于編寫特殊的程序——驅動程序。這些程序承載著硬件設備的詳細信息,并扮演著操作系統與硬件間溝通的橋梁角色。驅動開發的核心使命在于確保硬件設備在Linux系統上順暢運作,同時實現與操作系統的無縫集成,為用戶帶來流暢穩定的體驗。🚀🔧💻

Linux項目開發:Linux基礎知識的實踐,做項目是最鍛煉能力的一個學習方法,這里我們會學習到一些簡單基礎的項目開發與應用,而且都是畢業設計級別的哦。🤸🌱🚀

非常期待與您一同在這個廣闊的互聯網天地里,攜手探索知識的海洋,互相學習,共同進步。🌐💫🌱 熠熠星光,照亮我們的成長之路

?? 歡迎訂閱本專欄,對專欄內容任何問題都可以隨時聯系博主,共同書寫屬于我們的精彩篇章!??

?

?

文章介紹:

📚本篇文章將深入剖析EDA學習的精髓與奧秘,與您一同分享相關知識!🎉🎉🎉

若您覺得文章尚可入目,期待您能慷慨地送上點贊、收藏與分享的三連支持!您的每一份鼓勵,都是我創作路上源源不斷的動力。讓我們攜手并進,共同奔跑,期待在頂峰相見的那一天,共慶輝煌!🚀🚀🚀

🙏衷心感謝大家的點贊👍、收藏?和評論??,您的支持是我前進的動力!

前些天發現了一個巨牛的人工智能學習網站,通俗易懂,風趣幽默,忍不住分享一下給大家。點擊跳轉到網站:??????人工智能教程

目錄:

1.大家在3—8譯碼器時,采用了原理圖的輸入形式,是否還可以采用其他方式嗎?

在設計和實現3-8譯碼器時,通常會采用原理圖的形式來表示電路的邏輯結構。原理圖是一種圖形化的表示方法,它使用標準的邏輯符號來表示各個邏輯門和它們之間的連接關系。然而,除了原理圖之外,還有其他幾種方式可以用來表示和實現3-8譯碼器,比如可以通過邏輯表達式來描述3-8譯碼器的功能,真值表列出了所有可能的輸入組合及其對應的輸出狀態,使用硬件描述語言,如VHDL或Verilog,可以編寫代碼來描述3-8譯碼器的行為,可以通過布爾代數來簡化邏輯表達式,可以使用軟件工具來仿真3-8譯碼器的行為。

2.EDA技術在本課程中指的是什么技術,都有哪些技術優勢,本課程采用的硬件描述語言程序由哪幾部分組成,都有些什么作用。

(1)EDA技術:

即電子設計自動化技術,是指利用計算機輔助設計軟件來完成電子系統設計的過程。EDA技術涵蓋了從電路設計、仿真、驗證到物理實現(如布局布線)的整個流程。

(2)EDA技術優勢:

提高設計效率、保證設計質量、 支持復雜設計、促進設計重用、 優化設計性能、跨學科集成。

硬件描述語言(HDL)是用于描述電子系統硬件結構的編程語言,常見的HDL有VHDL和Verilog。一個典型的HDL程序通常由以下幾部分組成:庫和包的聲明、實體聲明、 結構體聲明、配置聲明、測試平臺。

(3)每部分的作用如下:

- 庫和包的聲明:提供設計所需的標準資源和功能。

- 實體聲明:定義模塊的外部接口,是模塊與外部世界交互的橋梁。

- 結構體聲明:實現模塊的具體功能,是模塊的核心部分。

- 配置聲明:在多個實現方案中選擇一個,用于設計的靈活性和可維護性。

- 測試平臺:驗證設計的正確性,確保設計在實際應用中能夠按預期工作。

3.FPGA和CPLD名稱

(1)FPGA

?FPGA的全稱是Field-Programmable Gate Array,即現場可編程門陣列。FPGA是一種集成電路,它包含大量的可編程邏輯塊和可配置的互連資源。用戶可以通過編程來配置這些邏輯塊和互連資源,以實現特定的數字邏輯功能。FPGA的特點包括高度的靈活性、可重配置性和并行處理能力。

(2)CPLD

CPLD的全稱是Complex Programmable Logic Device,即復雜可編程邏輯器件。CPLD也是一種集成電路,它由多個可編程邏輯塊(通常稱為宏單元)組成,這些邏輯塊通過可編程互連矩陣連接。CPLD相對于FPGA來說,規模較小,結構更為簡單,但同樣可以通過編程來實現各種邏輯功能。CPLD通常用于需要較少邏輯資源和較低成本的應用。

4.硬件描述語言HDL主要有哪些?優缺點是什么?

(1)VHDL

VHDL(VHSIC Hardware Description Language)是一種標準化的硬件描述語言,最初由美國國防部開發。

優點:

- 標準化:VHDL是一個IEEE標準,具有良好的文檔和廣泛的支持。

- 強大的建模能力:VHDL支持多種建模風格,包括行為級、數據流級和結構級。

- 嚴格的類型檢查:VHDL的類型系統嚴格,有助于減少設計錯誤。

- 可讀性和可維護性:VHDL代碼通常被認為更易于閱讀和維護。

缺點:

- 冗長:VHDL的語法相對冗長,有時需要編寫更多的代碼來完成相同的任務。

- 學習曲線:對于初學者來說,VHDL的學習曲線可能比較陡峭。

(2)Verilog

Verilog是一種廣泛使用的硬件描述語言,由Gateway Design Automation公司開發,后被Cadence Design Systems收購。

優點:

- 簡潔:Verilog的語法相對簡潔,代碼量通常比VHDL少。

- 易于學習:對于有編程背景的人來說,Verilog可能更容易學習。

- 廣泛采用:Verilog在業界有廣泛的應用和支持。

缺點:

- 類型系統較弱:Verilog的類型系統不如VHDL嚴格,可能導致一些設計錯誤。

- 可讀性:一些設計者認為Verilog代碼的可讀性不如VHDL。

(3)SystemVerilog

SystemVerilog是Verilog的擴展,增加了許多高級功能,旨在提高設計和驗證的效率。

優點:

- 增強的驗證功能:SystemVerilog提供了豐富的驗證功能,如斷言、接口和面向對象編程。

- 向后兼容:SystemVerilog與Verilog兼容,可以逐步采用。

- 提高生產力:通過高級功能,SystemVerilog可以提高設計和驗證的生產力。

缺點:

- 復雜性:SystemVerilog的功能豐富,但也增加了復雜性。

- 工具支持:雖然SystemVerilog得到了廣泛支持,但某些工具可能不完全支持所有功能。

(4)SystemC

SystemC是一種基于C++的硬件描述語言,用于系統級設計和建模。

優點:

- C++基礎:SystemC基于C++,對于有C++背景的設計者來說,學習曲線較低。

- 系統級建模:SystemC支持從系統級到門級的完整設計流程。

- 性能建模:SystemC可以進行性能分析和優化。

缺點:

- 工具支持:與VHDL和Verilog相比,SystemC的工具支持可能較少。

- 資源消耗:SystemC仿真可能需要更多的計算資源。

? ? ? ? 每種HDL都有其特定的應用場景和優勢,選擇哪種語言通常取決于項目需求、設計團隊的經驗和可用工具的支持。

5.自頂向下技術設計思路

自頂而下的設計方法使系統被分解為各個模塊的集合之后,可以對設計的每個獨立模塊指派不同的工作小組。這些小組可以工作在不同地點,甚至可以分屬不同的單位,最后將不同的模塊集成為最終的系統模型,并對其進行綜合測試和評價。

首先,設計說明書明確了功能需求和性能目標。隨后,通過建立HDL行為模型,我們以抽象的方式捕捉了設計的意圖和行為。這一模型隨后通過HDL行為仿真得到驗證,確保其邏輯的正確性。

接下來,設計進入HDL-RTL級建模階段,將抽象的行為模型轉化為更具體的寄存器傳輸級描述。前端功能仿真進一步驗證了RTL模型的正確性。邏輯綜合階段將RTL描述轉換為門級網表,這是設計從描述到實現的轉折點。

為了確保設計的可靠性,測試向量生成和功能仿真是必不可少的步驟,它們幫助我們發現并修正潛在的邏輯錯誤。結構綜合進一步優化了門級網表,以滿足時序和面積的約束。門級時序仿真則驗證了設計的時序行為,確保其在實際硬件中的正確運行。

最后,硬件測試階段將設計從仿真環境帶入現實世界,通過實際的硬件測試驗證設計的物理實現。這一系列步驟構成了一個完整的設計流程,確保了從概念到實現的每一步都經過嚴格的驗證和測試,最終完成設計。

6.設計輸入:

圖像輸入:圖形輸入通常包括原理圖輸人、狀態圖輸入和波形圖輸入三種常用設計方法。

狀態圖輸入設計方法就是根據電路的控制條件和不同的轉換方式,用繪圖的方法,在EDA工具的狀態圖編輯器上繪出狀態圖,然后由EDA編譯器和綜合器將此狀態變化流程圖形編譯綜合成電路網表。

波形圖輸人設計方法則是將待設計的電路看成是一個黑盒子,只需告訴EDA具黑盒子電路的輸入和輸出時序波形圖,EDA工具即能據此完成黑盒子電路的設計。

原理圖輸入設計方法是一種類似于傳統電子設計方法的原理圖編輯輸入方式,即在EDA軟件的圖形編輯界面上繪制能完成特定功能的電路原理圖。

HDL文本輸入:這種方式與傳統的計算機軟件語言編輯輸入基本一致。就是將使用了某種硬件描述語言的電路設計文本,如 VHDL 或 Verilog HDL 的源程序,進行編輯輸入。

7. 仿真電路的級別

按仿真電路描述級別的不同,HDL仿真器可以單獨或綜合完成以下各級仿真:系統級仿真,行為級仿真,RTL級仿真,門級時序仿真。

行為級仿真是在設計的最高抽象層次上進行的仿真,它主要關注電路的行為和功能,而不是具體的實現細節。在這個階段,設計通常使用高級硬件描述語言(HDL)如VHDL或Verilog來描述,這些描述更接近于算法或流程圖,而不是實際的硬件結構。

RTL級仿真是介于行為級和門級之間的仿真,它關注的是寄存器之間的數據傳輸和邏輯操作。在這個階段,設計已經被細化到寄存器傳輸級,使用HDL的描述更加具體,包含了寄存器、組合邏輯和時序邏輯等硬件元素。

8.CPLD的結構:

CPLD(Complex Programmable Logic Device)是一種可編程邏輯器件,它由多個邏輯塊(通常稱為宏單元或邏輯陣列塊)組成,這些邏輯塊通過可編程互連資源連接在一起。CPLD的結構設計旨在提供靈活的邏輯實現和快速的信號傳播路徑。以下是CPLD的基本結構組成部分:

-

邏輯陣列塊(LABs):

- CPLD的核心是邏輯陣列塊,每個LAB包含多個宏單元。

- 每個宏單元通常包含一組可編程的邏輯元件(如查找表LUT、多路復用器、觸發器等),可以實現復雜的邏輯功能。

- LABs之間的連接通過可編程互連資源實現。

-

宏單元(Macrocell):

- 宏單元是CPLD的基本構建塊,每個宏單元能夠實現一定的邏輯功能。

- 宏單元通常包括組合邏輯部分和時序邏輯部分,組合邏輯部分可以是一個或多個查找表,而時序邏輯部分通常是一個觸發器。

-

可編程互連資源:

- 可編程互連資源包括全局布線和局部布線網絡。

- 全局布線網絡連接不同的LABs,而局部布線網絡連接同一個LAB內的宏單元。

- 這些互連資源允許設計者根據需要配置信號路徑,實現所需的邏輯功能。

-

I/O單元:

- I/O單元負責處理CPLD與外部電路之間的輸入輸出信號。

- 每個I/O單元通常包含一個或多個可編程的輸入緩沖器、輸出驅動器和輸出使能控制。

- I/O單元可以配置為輸入、輸出或雙向模式。

-

配置存儲器:

- CPLD的配置信息存儲在非易失性存儲器中,如EEPROM或Flash存儲器。

- 這些存儲器保存了CPLD的邏輯配置和互連信息,使得CPLD在上電后能夠自動加載配置并運行設計好的邏輯。

CPLD的這種結構使得它非常適合實現中小規模的邏輯設計,具有快速的信號傳播速度和較低的功耗。由于其可編程性,CPLD在原型設計和小批量生產中非常有用,允許設計者在不改變硬件的情況下修改邏輯功能。

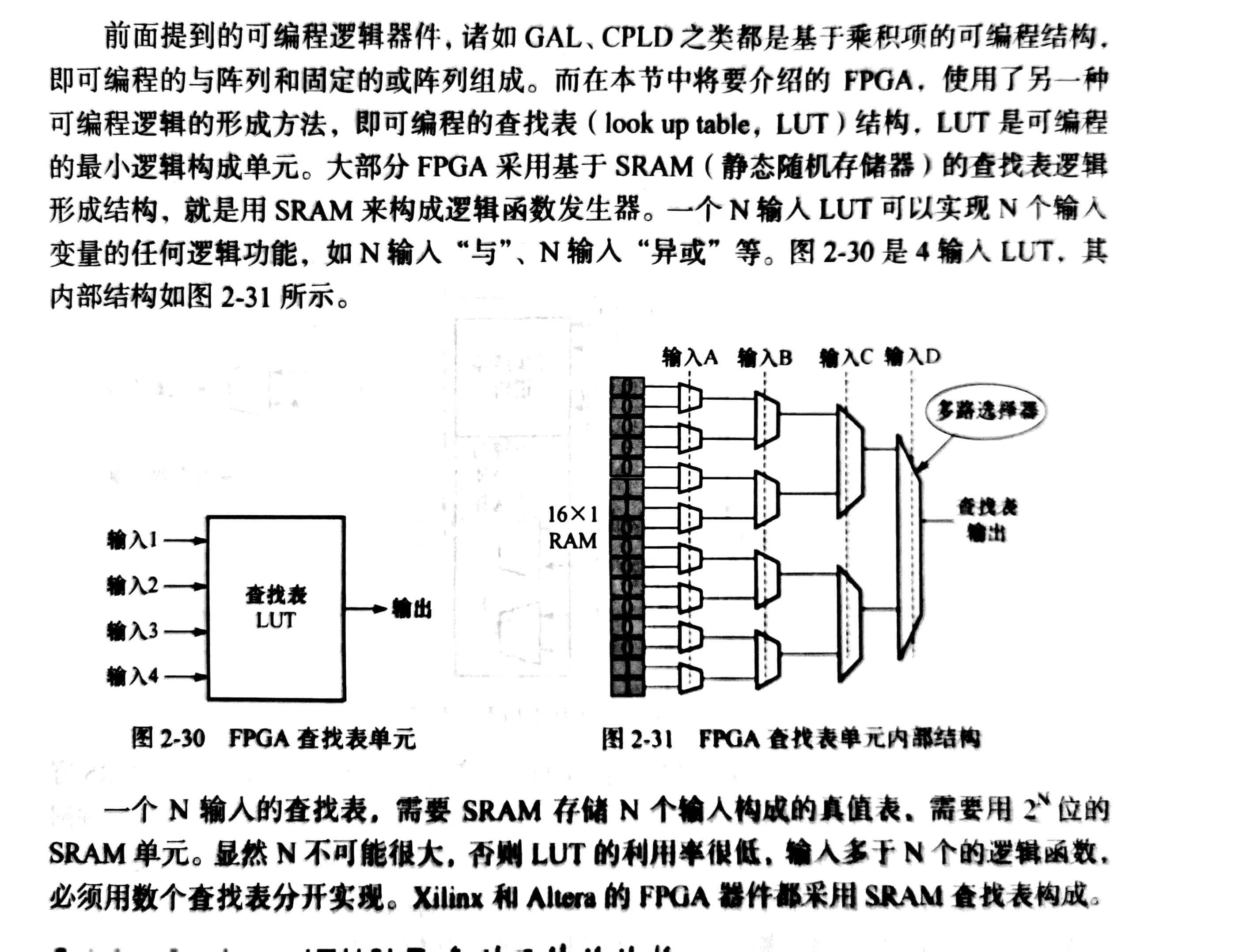

9.查找表邏輯結構

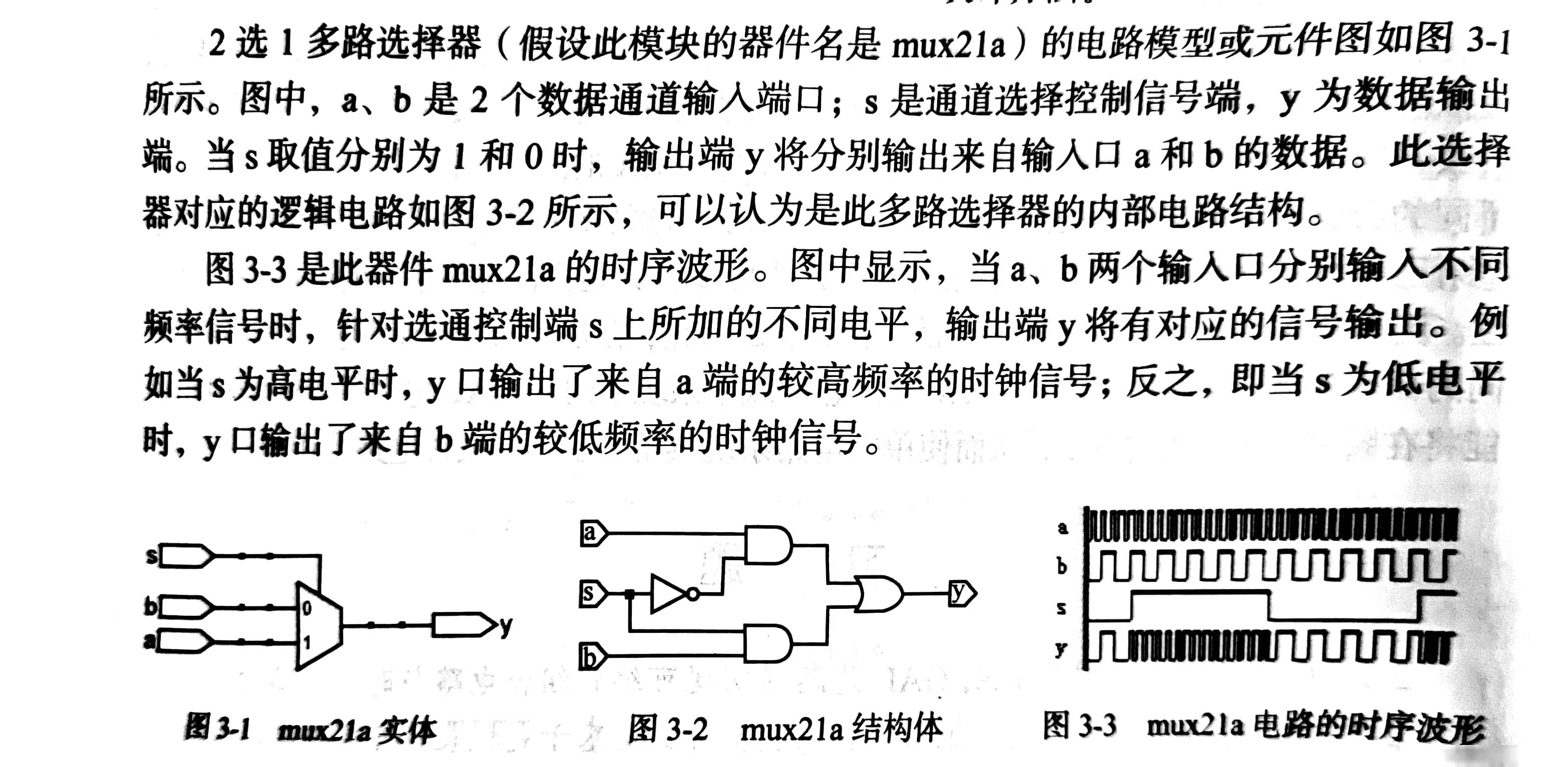

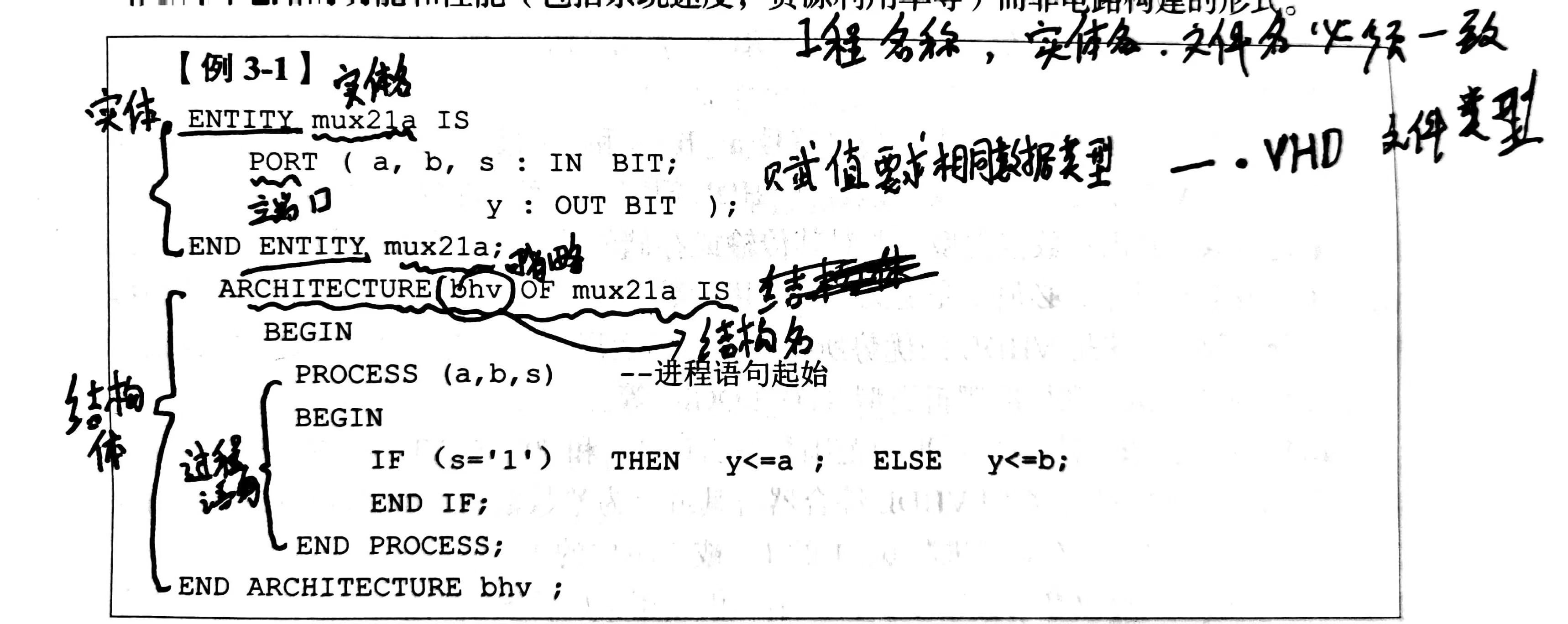

10.多路選擇器的VHDL描述

11.半加器的VHDL描述?

SO是和值的數據輸出端,CO則是進位數據的輸出端口。

![]()

12. 有哪幾種運算符?

算術運算符、關系運算符、邏輯運算符、位運算符、移位運算符、連接運算符、條件運算符、賦值運算符、范圍運算符

13.宏功能模塊是什么?基本操作有哪些?

宏功能模塊(Macrofunction)通常指的是預定義的、可重用的硬件模塊,這些模塊實現了特定的功能,如加法器、乘法器、計數器、狀態機等。

基本操作如下:

-

實例化:在設計中實例化宏功能模塊,將其作為一個組件使用。實例化時需要指定模塊的端口映射,即將設計中的信號與宏功能模塊的輸入輸出端口連接起來。

-

配置:根據設計需求配置宏功能模塊的參數,如位寬、時鐘頻率、初始狀態等。

-

連接:將宏功能模塊的輸入端口連接到其他模塊或信號,將輸出端口連接到需要使用其輸出的模塊或信號。

-

控制:通過控制信號或狀態機來控制宏功能模塊的運行,如啟動、停止、復位等。

-

測試:在仿真環境中對宏功能模塊進行測試,驗證其功能是否符合設計要求。

14.基本時序元件包括哪些?

-

觸發器(Flip-Flop):

- D觸發器(D Flip-Flop):在時鐘邊沿(通常是上升沿)捕獲輸入數據(D)并將其存儲在輸出端(Q)。

- JK觸發器(JK Flip-Flop):具有兩個輸入(J和K),在時鐘邊沿根據J和K的狀態改變輸出狀態。

- T觸發器(T Flip-Flop):具有一個輸入(T),在時鐘邊沿根據T的狀態切換輸出狀態。

- SR觸發器(SR Flip-Flop):具有兩個輸入(S和R),在時鐘邊沿根據S和R的狀態設置或重置輸出狀態。

-

鎖存器(Latch):

- D鎖存器(D Latch):在使能信號(通常是高電平)有效時捕獲輸入數據(D)并將其存儲在輸出端(Q)。

- SR鎖存器(SR Latch):具有兩個輸入(S和R),在使能信號有效時根據S和R的狀態設置或重置輸出狀態。

-

寄存器(Register):

- 并行寄存器:用于存儲一組數據位,通常由多個D觸發器組成,可以在時鐘邊沿同時捕獲和輸出所有數據位。

- 移位寄存器:用于存儲和移位數據,可以在時鐘邊沿將數據向左或向右移動一位或多位。

-

計數器(Counter):

- 二進制計數器:用于計數,可以遞增或遞減,通常由多個觸發器組成,每個觸發器代表一個二進制位。

- BCD計數器:用于計數,輸出為二進制編碼的十進制數(BCD碼)。

-

狀態機(State Machine):

- 摩爾型狀態機(Moore Machine):輸出僅取決于當前狀態,與輸入無關。

- 米利型狀態機(Mealy Machine):輸出取決于當前狀態和輸入。

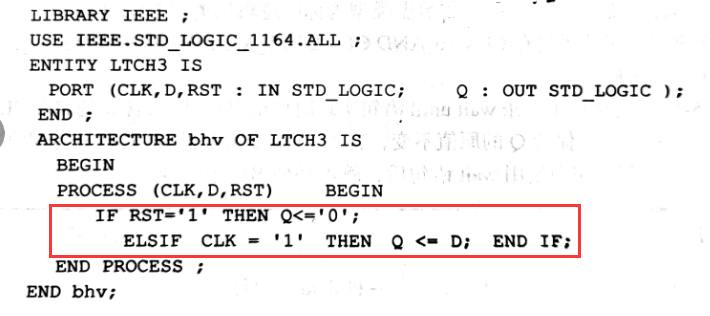

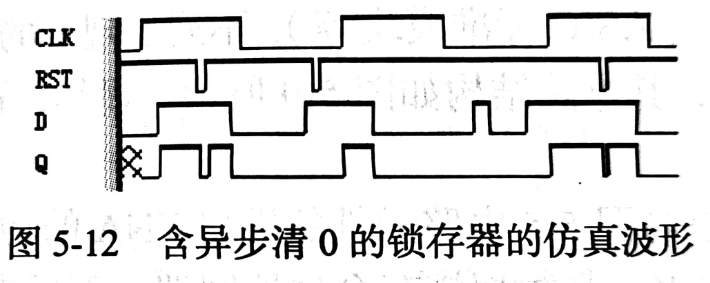

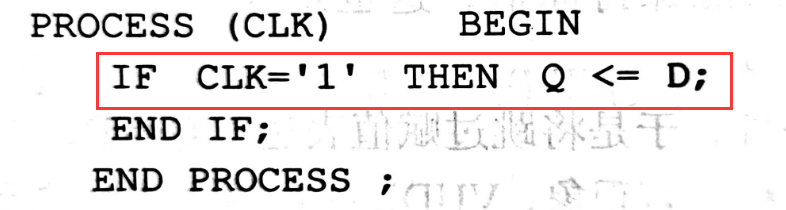

15.核心代碼與波形判斷

📝大佬覺得本文有所裨益,不妨輕點一下👍給予鼓勵吧!

??????本人雖努力,但能力尚淺,若有不足之處,懇請各位大佬不吝賜教,您的批評指正將是我進步的動力!😊😊😊

💖💖💖若您認為此篇文章對您有所幫助,煩請點贊👍并收藏🌟,您的支持是我前行的最大動力!

🚀🚀🚀任務在默默中完成,價值在悄然間提升。讓我們攜手共進,一起加油,迎接更美好的未來!🌈🌈🌈

?

?

?

)

詳細安裝和使用教程)

)

)