愛德萬測試(Advantest)的V93000系列測試系統是一個高度模塊化和可擴展的平臺,專為復雜和高性能的半導體器件測試而設計,包括系統級芯片(SoC)、存儲器、射頻(RF)和混合信號器件等。在Advantest 93000(通常被稱為V93000或V93K)測試機中,CLOCK DOMAIN的概念主要與多通道測試中的時鐘管理和同步相關。以下是對CLOCK DOMAIN在Advantest 93000測試機中的詳細解釋:

-

CLOCK DOMAIN的基本概念:

- CLOCK DOMAIN是指由特定時鐘信號驅動的硬件組件或測試通道的集合。在V93000測試機中,這些通道可能需要進行同步測試,以確保測試的準確性和一致性。

-

CLOCK DOMAIN的類型:

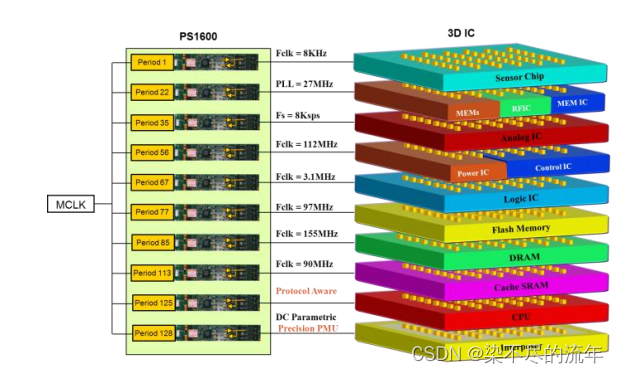

- SINGLE CLOCK DOMAIN:在這種模式下,模擬模塊與通道模塊共享主時鐘MCLK(Master Clock)。此時,模擬采樣頻率(FS)受到時鐘頻率除以某個因子(N)的限制。

- MULTIPLE CLOCK DOMAIN:在此模式下,不同的測試通道或模塊可以使用不同的時鐘源。這允許更靈活的時鐘設置和更高的采樣頻率。

-

時鐘源和時鐘板:

- V93000測試機中的時鐘源通常由一個或多個時鐘板提供。每個時鐘板可以產生多個獨立的MCLK線,分配到不同的測試卡槽上。

- 時鐘板由軟件控制,可以為不同的測試需求提供不同類型的時鐘源。時鐘板的作用包括頻率發生、控制功能碼、時鐘的路由和信號分配、參考信號、繼電器控制和電源線路等。

-

時鐘管理和同步:

- 在進行多通道測試時,CLOCK DOMAIN的管理和同步變得尤為重要。測試人員需要確保所有相關的通道或模塊都使用正確的時鐘源,并在需要時進行精確的同步。

- Advantest 93000測試機提供了強大的時鐘管理和同步功能,以確保測試的準確性和一致性。這些功能可能包括時鐘分配、時鐘相位調整、時鐘同步控制等。

-

實際應用:

- 在進行SSD主控芯片的高溫測試等復雜測試中,CLOCK DOMAIN的管理和同步尤為重要。測試人員需要根據測試需求配置適當的CLOCK DOMAIN,并確保所有相關的通道或模塊都使用正確的時鐘源和同步設置。

-

注意事項:

- 在配置CLOCK DOMAIN時,測試人員需要仔細考慮測試需求和硬件限制,以避免時鐘沖突或同步問題。

- 如果在測試過程中出現時鐘相關的問題,測試人員需要檢查CLOCK DOMAIN的配置和同步設置,并進行相應的調整。

? ? ?7.V93000測試機中時鐘域特性的詳細說明:

1)時鐘域靈活性:V93000平臺支持clock-domain-per-pin技術,這意味著每個測試引腳都可以獨立配置其時鐘信號。這項功能使得測試系統能夠模擬芯片內部不同工作頻率的時鐘域,對于驗證跨時鐘域信號傳輸的正確性至關重要。

2)精確時鐘控制:系統提供了精細的時鐘控制能力,允許用戶定義、生成和分配不同的時鐘信號到各個測試引腳,包括時鐘頻率、相位關系、占空比調整等,這對于測試含有異步或準同步時鐘域設計的器件尤為關鍵。

3)跨時鐘域測試能力:鑒于多時鐘域設計中常見的問題(如亞穩態、時序違例等),V93000通過其先進的測試算法和硬件能力,可以執行復雜的跨時鐘域測試向量,以驗證數據傳輸的完整性和時序合規性。

4)Protocol Engine-per-Pin:結合時鐘域功能,每引腳的協議引擎可以針對不同接口協議進行精確測試,確保在多時鐘域環境中協議層面上的正確交互。

5)SmartLoop與PRBS-per-pin:這些特性進一步增強了時鐘域測試的效率和精度,允許對單個引腳進行循環回送測試或偽隨機二進制序列(PRBS)測試,這對于驗證時鐘域邊界上的信號質量和傳輸錯誤非常有用。

7)動態配置與測試優化:V93000測試機支持在測試過程中動態更改時鐘配置,這使得測試工程師能更靈活地應對不同測試場景,優化測試覆蓋率,同時減少測試時間和成本。

)

和 Python 庫 SymPy 進行符號數學計算的教程)