目錄

- 1.結構描述(structural modeling)的內容:

- 2.實例

微信公眾號獲取更多FPGA相關源碼:

1.結構描述(structural modeling)的內容:

- 用門來描述器件的功能

- 基于基本元件和底層模塊例化語句

- 最接近實際的硬件結構

- 主要使用元件的定義、使用聲明以及元件例化來構建系統

- primitives(基本單元) : Verilog語言已定義的具有簡單邏輯功能的功能模型(models)

2.實例

Verilog HDL不同于C語言這類程序語言,在寫Verilog HDL代碼時,一定要清楚是在描述硬件,而不是在編寫程序。

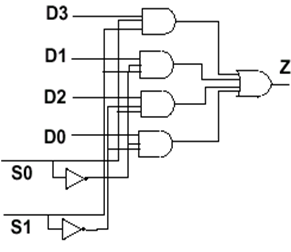

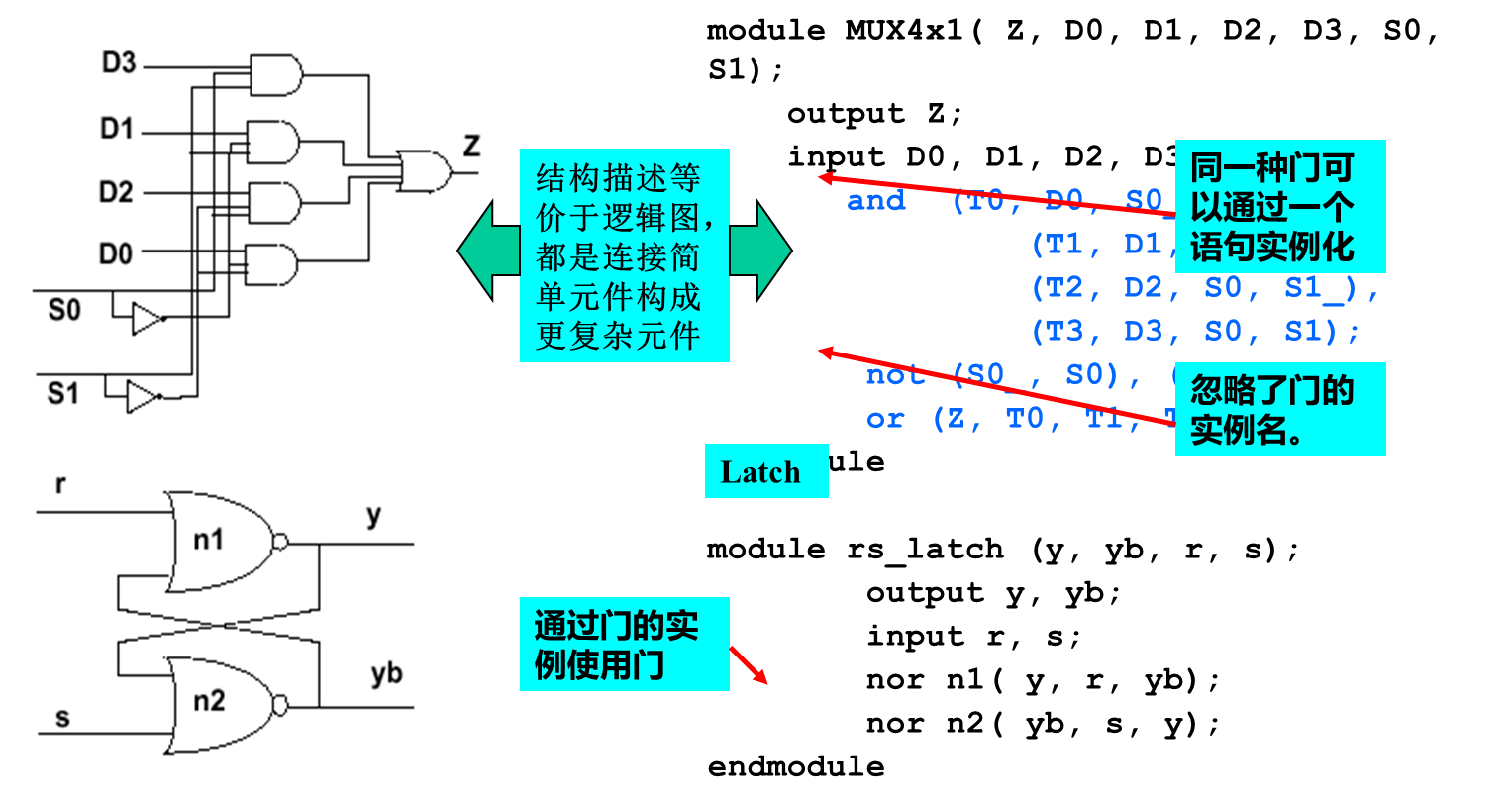

上圖電路圖可用如下硬件語言描述:

module MUX4x1( Z, D0, D1, D2, D3, S0, S1);output Z;input D0, D1, D2, D3, S0, S1;and (T0, D0, S0_, S1_),(T1, D1, S0_, S1),(T2, D2, S0, S1_),(T3, D3, S0, S1);not (S0_, S0), (S1_, S1);or (Z, T0, T1, T2, T3);

endmodule

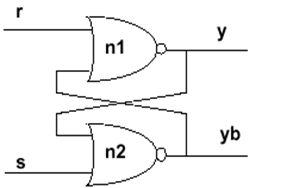

上圖的RS觸發器,可用如下硬件語言描述:

module rs_latch (y, yb, r, s);output y, yb;input r, s;nor n1( y, r, yb);nor n2( yb, s, y);

endmodule

- Verilog結構描述表示一個邏輯圖

- 結構描述用已有的元件構造。

- 結構描述等價于邏輯圖。它們都是連接簡單元件來構成更為復雜的元件。Verilog使用其連接特性完成簡單元件的連接。

- 在描述中使用元件時,通過建立這些元件的實例來完成。

- 上面的例子中MUX是沒有反饋的組合電路,使用中間或內部信號將門連接起來。描述中忽略了門的實例名,并且同一種門的所有實例可以在一個語句中實例化。

- 上面的鎖存器(latch)是一個時序元件,其輸出反饋到輸入上。它沒有使用任何內部信號。它使用了實例名并且對兩個nor門使用了分開的實例化語句。

微信公眾號獲取更多FPGA相關源碼:

)

)

)

內容 5 元數據)