文章目錄

- 一、計算機內存結構

- 1、內存的基本組成

- 2、內存的類型

- 3、內存的結構層次

- 4、CPU架構

- 5、局部性原理

- 6、總結

前言

在探討計算機的運行效率和數據處理能力時,內存結構無疑是一個至關重要的部分。內存,作為計算機系統中的關鍵組件,承擔著存儲數據和指令以供處理器(CPU)快速訪問的重要任務。

一、計算機內存結構

1、內存的基本組成

計算機內存的基本組成單元是存儲單元。每個存儲單元由一個電容和一個晶體管組成,其中電容用于存儲數據,而晶體管則負責控制數據的讀取和寫入。這種設計使得內存能夠在計算機運行時快速、準確地存取數據。

2、內存的類型

- 靜態隨機存取存儲器(SRAM):SRAM使用觸發器來存儲數據,因此具有較快的讀寫速度。然而,由于其制造成本較高,SRAM通常被用于高速緩存(Cache)等需要快速訪問的場景。

- 動態隨機存取存儲器(DRAM):DRAM使用電容來存儲數據,雖然讀寫速度稍慢于SRAM,但其制造成本較低,因此被廣泛應用于主存儲器(內存條)中。DRAM需要周期性地進行刷新以保持數據的穩定性。

3、內存的結構層次

計算機內存結構通常呈現出一種層次化的特點,從高到低依次為:寄存器、高速緩存(Cache)、主存儲器(內存條)和輔助存儲器(如硬盤、固態硬盤等)。

- 寄存器:寄存器是離CPU最近的存儲單元,其讀寫速度最快。CPU可以直接訪問寄存器中的數據,無需經過其他存儲層次。寄存器通常用于存儲CPU正在處理的數據和指令。

- 高速緩存(Cache):高速緩存位于CPU和主存儲器之間,用于緩存主存儲器中常用的數據和指令。當CPU需要訪問數據時,首先會檢查高速緩存中是否存在所需數據。如果存在,則直接從高速緩存中讀取數據,從而提高了數據的訪問速度。高速緩存通常分為多個層次,如L1 Cache、L2 Cache和L3 Cache等。

- 主存儲器(內存條):主存儲器是計算機系統中的主要內存,用于存儲正在運行的程序和數據。主存儲器通常由多個存儲體組成,每個存儲體中有許多存儲單元。每個存儲單元可以存儲一個二進制數或一串二進制代碼(稱為存儲字)。存儲字的長度可以是8位、16位、32位等。主存儲器通過地址線、數據線和控制線等接口與CPU相連,實現數據的快速讀寫。

- 輔助存儲器:輔助存儲器包括硬盤、固態硬盤等存儲介質,用于存儲大量數據和程序。與主存儲器相比,輔助存儲器的讀寫速度較慢,但容量較大且價格相對較低。輔助存儲器中的數據在需要時會被加載到主存儲器中供CPU處理。

4、CPU架構

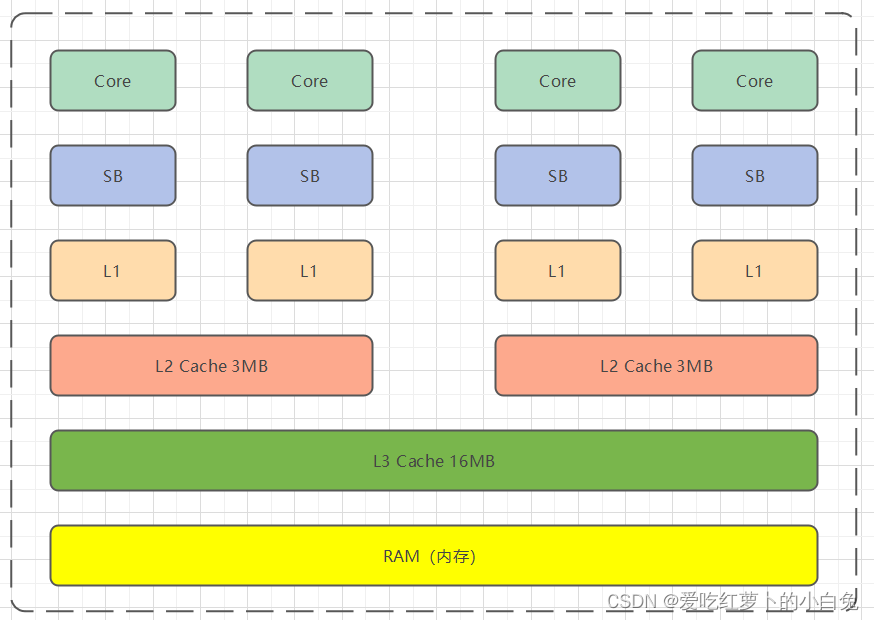

下面是一個的多核CPU架構圖,如下:

- Core:每個Core獨享SB與L1

- SB(Store Buffer):Store Buffer是一個緩沖區,用于暫存CPU的寫操作,它允許CPU把數據先寫入Store Buffer,然后繼續執行其他操作,而不是等待數據被寫入緩存或內存后再進行下一步。這樣設計的好處是顯著降低了內存寫延遲對CPU性能的影響。

- L1 Cache:存儲了CPU近期可能訪問的數據和指令,且兩個L1 Cache獨享一個L2 Cache

注意:上面的CPU架構只是部分CPU采用的架構,并不能代表全部。

為什么需要使用Cache?

如果沒有Cache,CPU每執行一條指令就要到內存中取數據。執行一條指令只需要幾個時鐘周期,而取指令需要上百個時鐘周期,這就將導致CPU大部分時間都處于等待狀態,進而導致執行效率低下,引入了Cache主要解決CPU等待問題。

使用Cache會引入一些新的問題,例如:Cache的一致性、Cache的缺失等,為了解決這些問題,各CPU平臺(ARM/X86/IA64)都有自己的解決方案。軟件層面(編譯器)也會有對應的優化,這導致了CPU執行的程序并不是你寫的那個版本,只是從結果上看不出差異而已。

5、局部性原理

在計算機存儲結構中,局部性原理是一個重要的概念。局部性原理包括時間局部性和空間局部性兩個方面。時間局部性指的是如果一個數據項被訪問了,那么它在不久的將來很可能還會被再次訪問;空間局部性指的是如果一個數據項被訪問了,那么與其相鄰的數據項也很可能被訪問。基于局部性原理,計算機內存結構通常采用緩存機制來提高數據的訪問速度。

6、總結

計算機內存結構是計算機系統中的核心組成部分,其性能直接影響到計算機的運行效率和數據處理能力。通過對內存的基本組成、類型、結構層次以及局部性原理等概念的深入剖析,可以更好地理解計算機內存的工作原理和重要性。

:Vue模板語法)

)

)

)

![whisper報錯:hp, ht, pid, tid = _winapi.CreateProcess [WinError 2] 系統找不到指定的文件。](http://pic.xiahunao.cn/whisper報錯:hp, ht, pid, tid = _winapi.CreateProcess [WinError 2] 系統找不到指定的文件。)