文章目錄

- 1.關聯VS Code

- 2.Diamond工程目錄

- 3.Led Demo開發流程

- 4.燒寫bit文件

- 5.傳送門

1.關聯VS Code

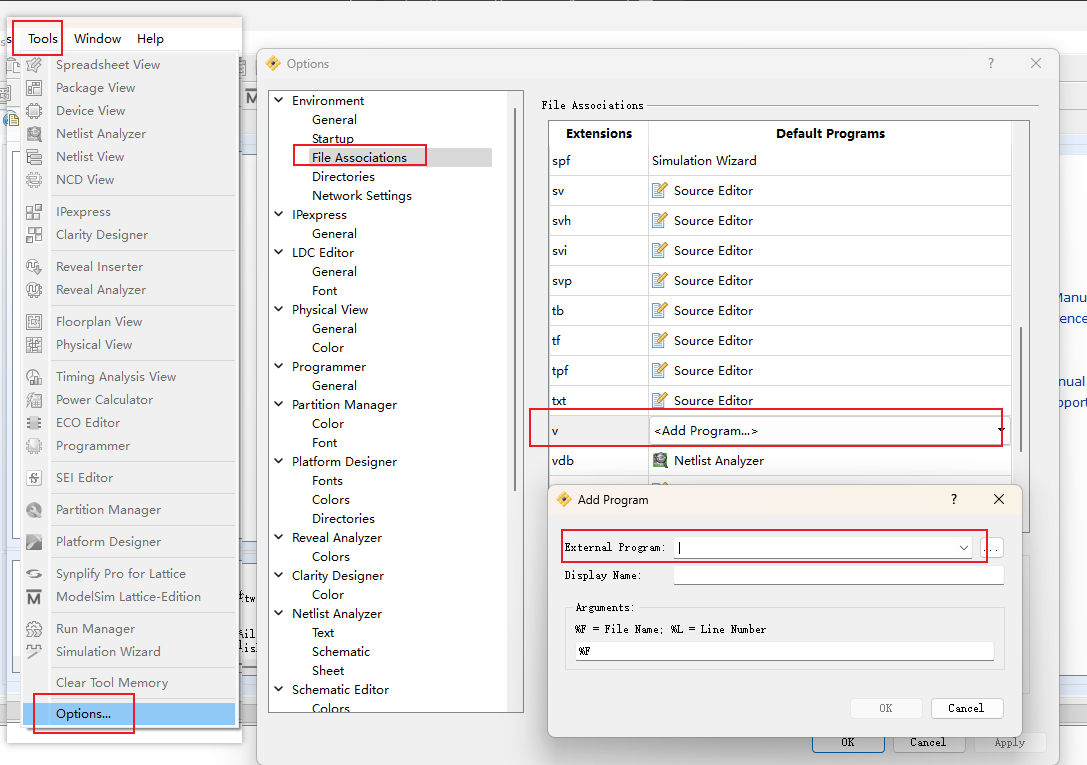

和Vivado一樣,Diamond也可以使用第三方的編輯器,VS Code編輯器因為可以安裝各種插件,并且對verilog開發的支持也算完善,所以很受歡迎。關于VS Code具體插件和漢化包參考Vivado關聯VS Code文本編輯器。具體操作如下,選擇tools–>Options–>File Associations,然后選擇v文件,點擊打開將VS Code安裝路徑選上即可。

2.Diamond工程目錄

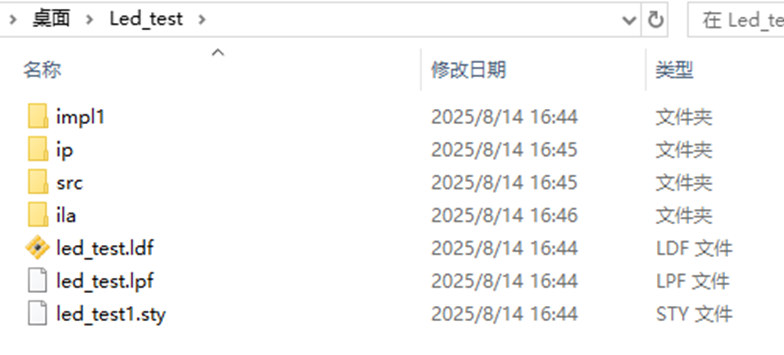

如圖所示,Diamond不會像Vivado一樣有相對整潔的目錄,所以通常會在工程目錄下根據自己的習慣建立子文件夾以便于工程管理。我的習慣是src文件放源文件即.v文件,ip目錄放工程中用到的IP核生成的文件,ila放Diamond的在線監測工具reveal的相關文件。

3.Led Demo開發流程

寫一個兩個led交替閃爍的程序熟悉Diamond的開發流程。具體操作如下:

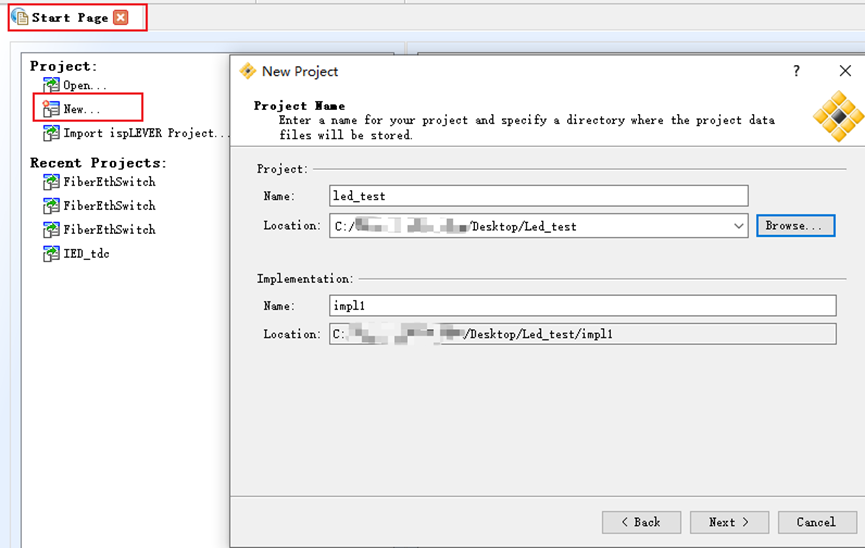

①在Start Page界面選擇New,然后輸入工程名字和保存路徑,點擊Next。

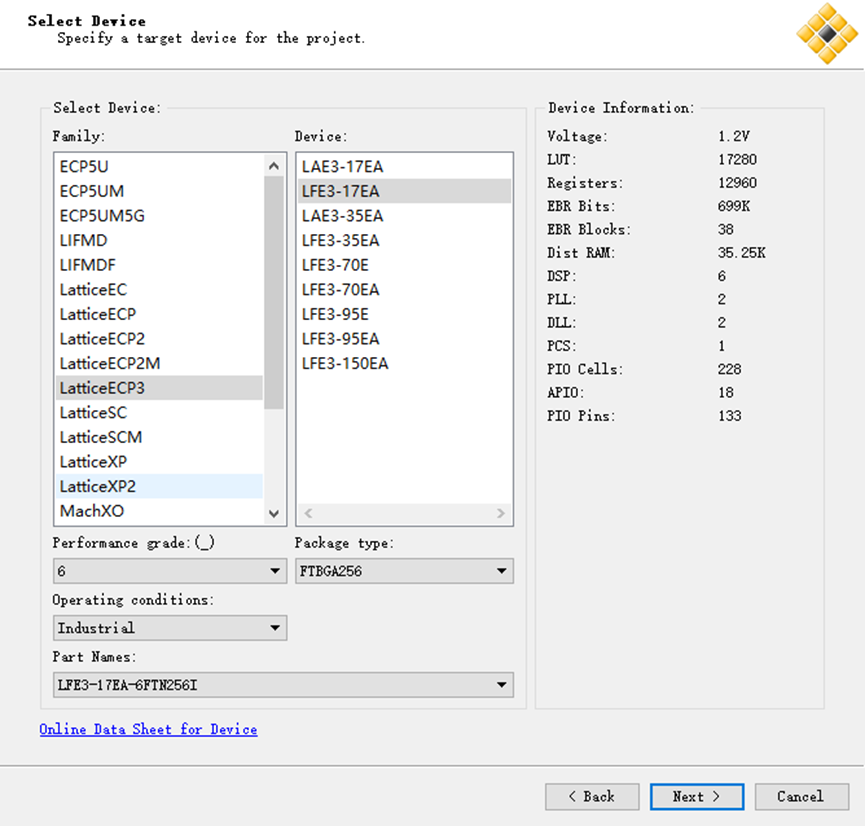

②選擇相應的FPGA型號,點擊Next

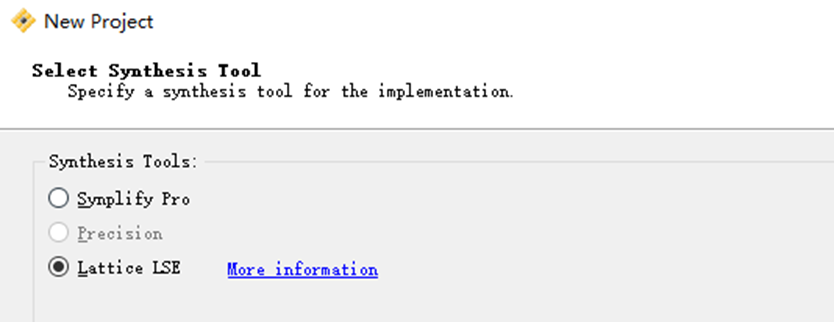

③任選一個綜合工具,點擊Next

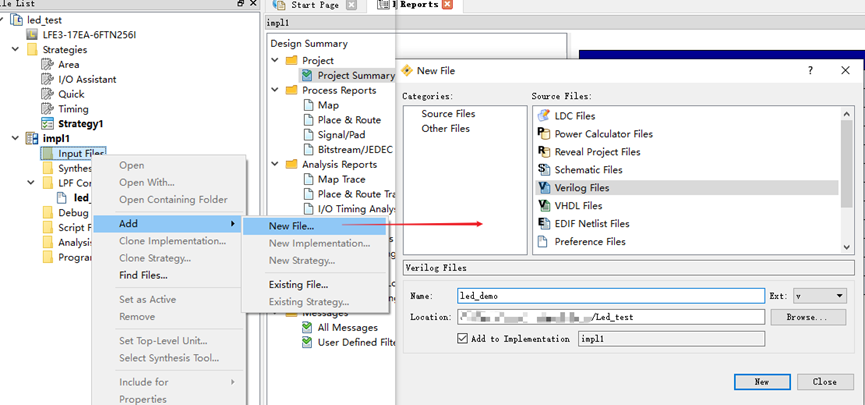

④隨后郵件Input File,選擇Add–>New File選擇Verilog Files 輸入名字和保存位置即可。

⑤雙擊源文件,打開vs code編輯器,輸入以下代碼,可以看到工程實現是led1和led2交替閃爍。

module LED_demo

(

input clk_i, //輸入系統時鐘

input rst_n, //輸入復位信號

output led1, //輸出led1

output led2 //輸出led2,與led1取反

);

parameter CLK_DIV_PERIOD=125_000_000;

reg clk_div=0;

assign led1=clk_div;

assign led2=~clk_div;

reg[23:0] led_cnt=0; //分頻用的計數器

always@(posedge clk_i or negedge rst_n)beginif(!rst_n)beginled_cnt<=0;end else if(led_cnt==(CLK_DIV_PERIOD-1)) beginled_cnt<=0;end else beginled_cnt<=led_cnt+1'b1;end

endalways@(posedge clk_i or negedge rst_n)beginif(!rst_n)beginclk_div<=0;end else if(led_cnt<(CLK_DIV_PERIOD>>1)) begin clk_div<=0;end else beginclk_div<=1;end

end

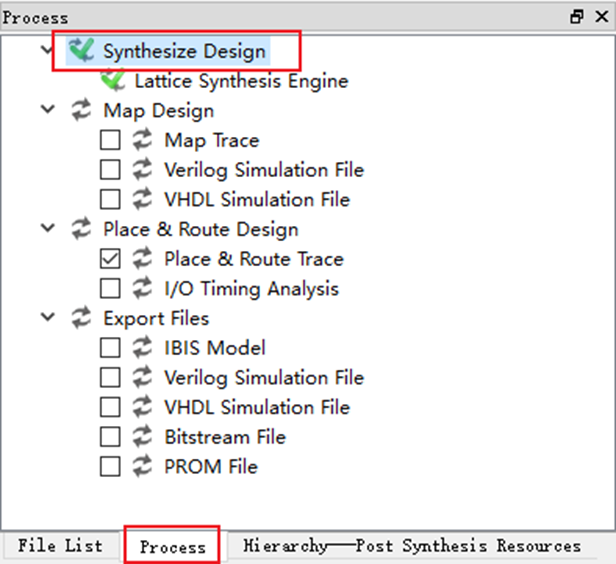

endmodule⑥隨后點擊Sythesis Design,知道出現綠色對勾顯示綜合通過

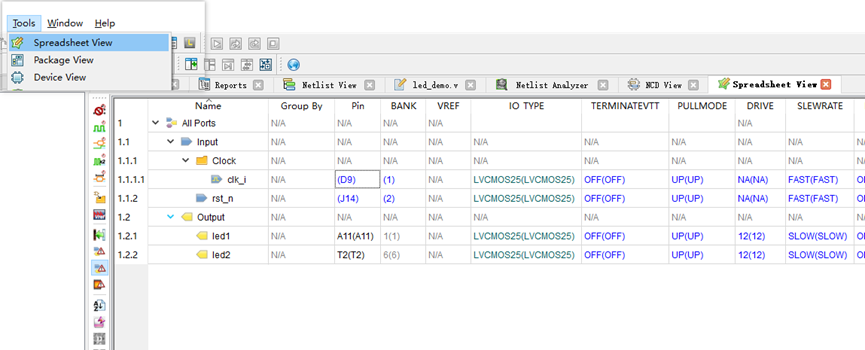

⑦點擊Tools–>Spreadsheet View為工程添加引腳約束信息。

⑧在Process界面點擊Bitstream File即可生成bit文件

4.燒寫bit文件

連接Jtag,給板子上電

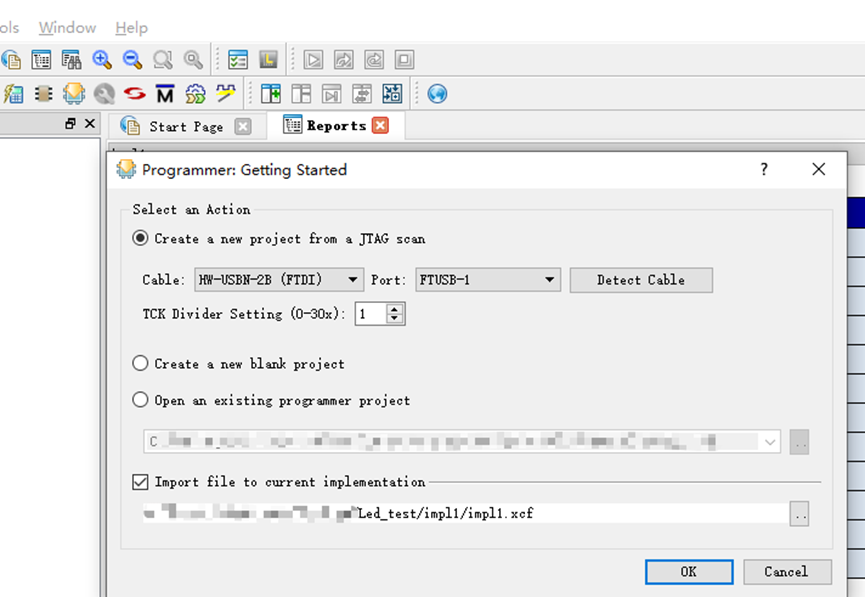

①選擇下圖中黃色箭頭向下的圖標,打開Programmer:Getting Started界面,選擇Create a new project from a JTAG scan,如圖中顯示的Port:FTUSB-1,這是我故意連了兩個JTAG,這里要對應好自己板子的port號,可單擊Detect Cable之后選擇對應Port。點擊OK進入下一步。

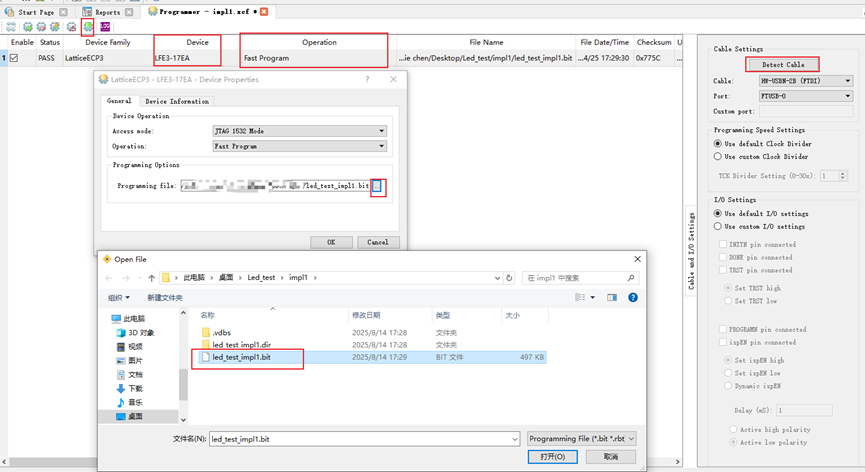

②點擊Device處選擇對應FPGA型號,單擊Fast Program,出現圖中界面選擇燒寫的bit文件,然后單擊綠色圖標下載程序。

5.傳送門

- 我的主頁

- Lattice進階之路匯總導航

- 上一篇:認識Lattice器件

| END |

📡文章原創,首發于CSDN論壇。

📡歡迎點贊??收藏??打賞💵💵!

📡歡迎評論區或私信指出錯誤💉,提出寶貴意見或疑問😱。

)