目錄

- 1、前言

- Aurora 64B66B是啥?

- 官方有Example,為何要用你這個?

- 工程概述

- 免責聲明

- 2、相關方案推薦

- 我已有的所有工程源碼總目錄----方便你快速找到自己喜歡的項目

- 我這里已有的 GT 高速接口解決方案

- 本方案在Aurora 8B10B上的應用

- 3、工程詳細設計方案

- 工程設計原理框圖

- 輸入Sensor之-->OV5640攝像頭

- Native視頻轉AXIS流

- AXIS視頻流重組

- Aurora 64B66B視頻傳輸傳輸架構

- Aurora 64B66BIP核簡介

- Aurora 64B66B 基本結構

- Aurora 64B66B 發送流程

- Aurora 64B66B 接收流程

- Aurora 64B66B 時鐘架構

- Aurora 64B66B IP核調用和使用

- AXIS視頻流恢復

- AXIS視頻流寫緩存

- AXIS視頻流讀緩存

- HDMI視頻輸出架構

- 點對點視頻發送端工程源碼架構

- 點對點視頻接收端工程源碼架構

- 4、vivado工程源碼1詳解-->Kintex7--325T,點對點OV5640視頻轉SFP光口發送

- 5、vivado工程源碼2詳解-->Kintex7--325T,點對點SFP光口接收OV5640視頻轉HDMI

- 6、vivado工程源碼3詳解-->Zynq7100,點對點OV5640視頻轉SFP光口發送

- 7、vivado工程源碼4詳解-->Zynq7100,點對點SFP光口接收OV5640視頻轉HDMI

- 8、工程移植說明

- vivado版本不一致處理

- FPGA型號不一致處理

- 其他注意事項

- 9、上板調試驗證

- 準備工作

- Aurora 64B66B 視頻點對點傳輸效果演示

- 10、工程代碼的獲取

FPGA實現Aurora 64B66B視頻點對點傳輸,基于GTX高速收發器,提供4套工程源碼和技術支持

FPGA實現Aurora 64B66B圖像視頻傳輸

1、前言

Aurora 64B66B是啥?

Aurora 64B/66B 是Xilinx(現AMD)開發的高性能鏈路層協議,專為超高帶寬串行通信設計。它采用64B/66B編碼方案,提供比傳統8B/10B更高的有效帶寬利用率(97% vs 80%),主要應用于數據中心、5G基礎設施等需要100Gbps+傳輸的場景

Aurora 64B66B核心作用如下:

1、超高帶寬傳輸:支持25Gbps至112Gbps線速率

2、低協議開銷:僅3.125%的編碼開銷(對比8B/10B的25%)

3、多通道聚合:支持多達32通道綁定

4、前向糾錯:集成Reed-Solomon FEC增強可靠性

5、靈活拓撲:支持點對點、環網和星型結構

Aurora 64B66B主要工程應用如下:

博主之前實現過Aurora 8B10B編解碼,本博客用的則是Aurora 64B66B IP核,這兩種方法編解碼器區別如下:

Aurora 64B/66B vs 8B/10B 全面對比

官方有Example,為何要用你這個?

Xilinx官方的確有Aurora 64B66B IP核的Example例程;

然后呢?你看得懂嗎?你會照著模仿做自己的項目嗎?

如果你會,那么請劃走;

如果你不會,不妨看看下面的聊天記錄

這位朋友用了我的Aurora 64B66B數據回環傳輸工程,感覺少走了一年的彎路。。。

工程概述

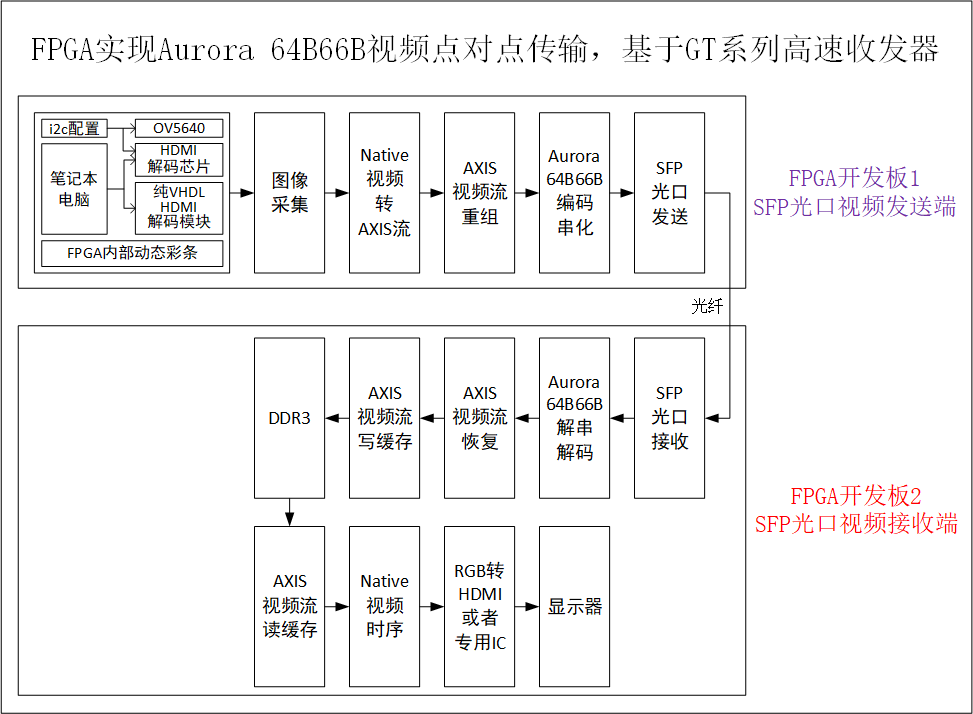

本設計使用Xilinx 7系列FPGA為平臺,基于GTX高速收發器實現Aurora 64B66B視頻點對點傳輸,所謂點對點傳輸,也就是兩塊FPGA開發板之間的相互傳輸;比如FPGA開發板1采集視頻并通過SFP光口輸出,FPGA開發板2通過SFP光口接收視頻然后轉HDMI輸出給顯示器;本設計旨在為讀者提供一套精簡版的、基于Aurora 64B66B編解碼的視頻點對點收發架構;

視頻發送端處理流程如下:

FPGA開發板1的視頻輸入源有多種,一種是板載的HDMI輸入接口,另一種是傳統攝像頭,包括OV7725、OV5640和AR0135;如果你的FPGA開發板沒有視頻輸入接口,或者你的手里沒有攝像頭時,可以使用FPGA邏輯實現的動態彩條模擬輸入視頻,代碼里通過parametr參數選擇視頻源,默認不使用動態彩條;FPGA首先對攝像頭進行i2c初始化配置,然后采集攝像頭視頻;然后采集視頻送入Xilinx官方的Video In To AXI4-Stream IP核實現Native視頻轉換到AXI4-Stream視頻流;然后AXI4-Stream視頻流再送入純verilog代碼實現的AXIS視頻流重組模塊實現信號重組,因為Aurora 64B66B發送接口不帶tuser信號,所以需要將tuser嵌入到數據流中傳輸;然后視頻流送入Xilinx官方的Aurora 64B66B IP核實現64B66B數據編碼,數據以高速差分信號輸出,經板載的SFP光口發送至遠端節點;

視頻接收端處理流程如下:

FPGA開發板2用板載的SFP光口的光纖接收視頻,經SFP-RX接口輸入高速差分信號再進入Xilinx官方的Aurora 64B66B IP核實現64B66B數據解碼,輸出AXI4-Stream視頻流;AXI4-Stream視頻流再送入純verilog代碼實現的AXIS視頻流重組模塊實現信號恢復,因為Aurora 64B66B接收接口不帶tuser信號,所以需要在嵌入數據中的tuser恢復出來;然后AXI4-Stream視頻流送入本博主自研的純verilog實現的、AXI4-Stream接口的圖像寫緩存模塊,實現視頻寫入DDR緩存操作;然后使用本博主自研的純verilog實現的、AXI4-Stream接口的圖像讀緩存模塊,實現視頻從DDR讀出操作;然后讀出的視頻送入純verilog實現的Native視頻時序模塊實現視頻同步;然后使用RGB轉HDMI模塊或者專用芯片實現RGB視頻流轉HDMI差分視頻信號;最后用顯示器顯示視頻即可;

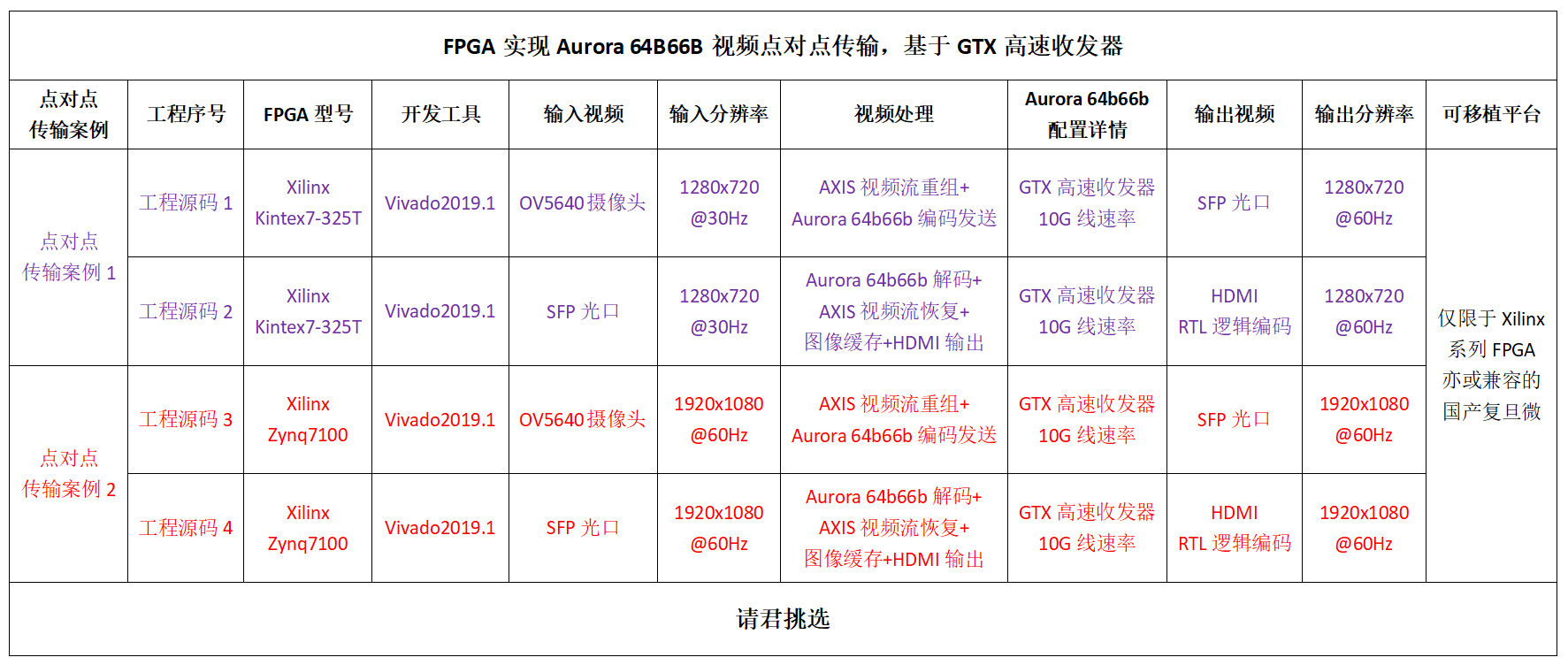

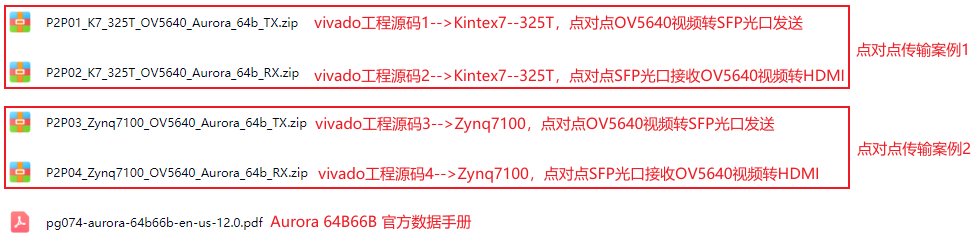

針對市場主流需求,本博客設計并提供4套工程源碼,具體如下:

現對上述4套工程源碼做如下解釋,方便讀者理解:

工程源碼1:點對點傳輸案例1的視頻發送端工程

開發板FPGA型號為Xilinx–>Kintex7–35T–xc7k325tffg676-2;此工程為點對點傳輸案例1的視頻發送端工程,即視頻Aurora 64B66B編碼轉SFP光口輸出;FPGA開發板1的輸入視頻為OV5640攝像頭或者動態彩條,默認使用OV5640;FPGA首先使用純Verilog實現的i2c總線對攝像頭進行初始化配置,分辨率配置為1280x720@30Hz;然后采集輸入視頻,將輸入的兩個時鐘傳輸一個RGB565像素的視頻采集為一個時鐘傳輸一個RGB888像素的視頻;然后采集視頻送入Xilinx官方的Video In To AXI4-Stream IP核實現Native視頻轉換到AXI4-Stream視頻流;然后AXI4-Stream視頻流再送入純verilog代碼實現的AXIS視頻流重組模塊實現信號重組,因為Aurora 64B66B發送接口不帶tuser信號,所以需要將tuser嵌入到數據流中傳輸;然后視頻流送入Xilinx官方的Aurora 64B66B IP核實現64B66B數據編碼,數據以高速差分信號輸出,經板載的SFP光口發送至遠端節點,輸出分辨率為1280x720@60Hz;由此形成Sensor+64B66B編碼+SFP光口的高端架構;該工程適用于視頻轉SFP光口光端機應用;

工程源碼2:點對點傳輸案例1的視頻接收端工程

開發板FPGA型號為Xilinx–>Kintex7–35T–xc7k325tffg676-2;此工程為點對點傳輸案例1的視頻接收端工程,即SFP光口視頻接收Aurora 64B66B解碼轉HDMI輸出;FPGA開發板2用板載的SFP光口的光纖接收視頻,經SFP-RX接口輸入高速差分信號再進入Xilinx官方的Aurora 64B66B IP核實現64B66B數據解碼,輸出AXI4-Stream視頻流;AXI4-Stream視頻流再送入純verilog代碼實現的AXIS視頻流重組模塊實現信號恢復,因為Aurora 64B66B接收接口不帶tuser信號,所以需要在嵌入數據中的tuser恢復出來;然后AXI4-Stream視頻流送入本博主自研的純verilog實現的、AXI4-Stream接口的圖像寫緩存模塊,實現視頻寫入DDR緩存操作;然后使用本博主自研的純verilog實現的、AXI4-Stream接口的圖像讀緩存模塊,實現視頻從DDR讀出操作;然后讀出的視頻送入純verilog實現的Native視頻時序模塊實現視頻同步;然后使用RGB轉HDMI模塊或者專用芯片實現RGB視頻流轉HDMI差分視頻信號;最后用顯示器顯示視頻即可,輸出分辨率為1280x720@60Hz;由此形成Sensor+64B66B編碼+SFP光口的高端架構;該工程適用于視頻轉SFP光口光端機應用;

工程源碼3:點對點傳輸案例2的視頻發送端工程

開發板FPGA型號為Xilinx–>Zynq7100–xc7z100ffg900-2;此工程為點對點傳輸案例2的視頻發送端工程,即視頻Aurora 64B66B編碼轉SFP光口輸出;FPGA開發板1的輸入視頻為OV5640攝像頭或者動態彩條,默認使用OV5640;FPGA首先使用純Verilog實現的i2c總線對攝像頭進行初始化配置,分辨率配置為1280x720@30Hz;然后采集輸入視頻,將輸入的兩個時鐘傳輸一個RGB565像素的視頻采集為一個時鐘傳輸一個RGB888像素的視頻;然后采集視頻送入Xilinx官方的Video In To AXI4-Stream IP核實現Native視頻轉換到AXI4-Stream視頻流;然后AXI4-Stream視頻流再送入純verilog代碼實現的AXIS視頻流重組模塊實現信號重組,因為Aurora 64B66B發送接口不帶tuser信號,所以需要將tuser嵌入到數據流中傳輸;然后視頻流送入Xilinx官方的Aurora 64B66B IP核實現64B66B數據編碼,數據以高速差分信號輸出,經板載的SFP光口發送至遠端節點,輸出分辨率為1280x720@60Hz;由此形成Sensor+64B66B編碼+SFP光口的高端架構;該工程適用于視頻轉SFP光口光端機應用;

工程源碼4:點對點傳輸案例2的視頻接收端工程

開發板FPGA型號為Xilinx–>Zynq7100–xc7z100ffg900-2;此工程為點對點傳輸案例2的視頻接收端工程,即SFP光口視頻接收Aurora 64B66B解碼轉HDMI輸出;FPGA開發板2用板載的SFP光口的光纖接收視頻,經SFP-RX接口輸入高速差分信號再進入Xilinx官方的Aurora 64B66B IP核實現64B66B數據解碼,輸出AXI4-Stream視頻流;AXI4-Stream視頻流再送入純verilog代碼實現的AXIS視頻流重組模塊實現信號恢復,因為Aurora 64B66B接收接口不帶tuser信號,所以需要在嵌入數據中的tuser恢復出來;然后AXI4-Stream視頻流送入本博主自研的純verilog實現的、AXI4-Stream接口的圖像寫緩存模塊,實現視頻寫入DDR緩存操作;然后使用本博主自研的純verilog實現的、AXI4-Stream接口的圖像讀緩存模塊,實現視頻從DDR讀出操作;然后讀出的視頻送入純verilog實現的Native視頻時序模塊實現視頻同步;然后使用RGB轉HDMI模塊或者專用芯片實現RGB視頻流轉HDMI差分視頻信號;最后用顯示器顯示視頻即可,輸出分辨率為1280x720@60Hz;由此形成Sensor+64B66B編碼+SFP光口的高端架構;該工程適用于視頻轉SFP光口光端機應用;

本博客詳細描述了FPGA實現Aurora 64B66B視頻點對點傳輸的設計方案,工程代碼可綜合編譯上板調試,可直接項目移植,適用于在校學生、研究生項目開發,也適用于在職工程師做學習提升,可應用于醫療、軍工等行業的高速接口或圖像處理領域;

提供完整的、跑通的工程源碼和技術支持;

工程源碼和技術支持的獲取方式放在了文章末尾,請耐心看到最后;

免責聲明

本工程及其源碼即有自己寫的一部分,也有網絡公開渠道獲取的一部分(包括CSDN、Xilinx官網、Altera官網等等),若大佬們覺得有所冒犯,請私信批評教育;基于此,本工程及其源碼僅限于讀者或粉絲個人學習和研究,禁止用于商業用途,若由于讀者或粉絲自身原因用于商業用途所導致的法律問題,與本博客及博主無關,請謹慎使用。。。

2、相關方案推薦

我已有的所有工程源碼總目錄----方便你快速找到自己喜歡的項目

其實一直有朋友反饋,說我的博客文章太多了,亂花漸欲迷人,自己看得一頭霧水,不方便快速定位找到自己想要的項目,所以本博文置頂,列出我目前已有的所有項目,并給出總目錄,每個項目的文章鏈接,當然,本博文實時更新。。。以下是博客地址:

點擊直接前往

我這里已有的 GT 高速接口解決方案

我的主頁有FPGA GT 高速接口專欄,該專欄有 GTP 、 GTX 、 GTH 、 GTY 等GT 資源的視頻傳輸例程和PCIE傳輸例程,其中 GTP基于A7系列FPGA開發板搭建,GTX基于K7或者ZYNQ系列FPGA開發板搭建,GTH基于KU或者V7系列FPGA開發板搭建,GTY基于KU+系列FPGA開發板搭建;以下是專欄地址:

點擊直接前往

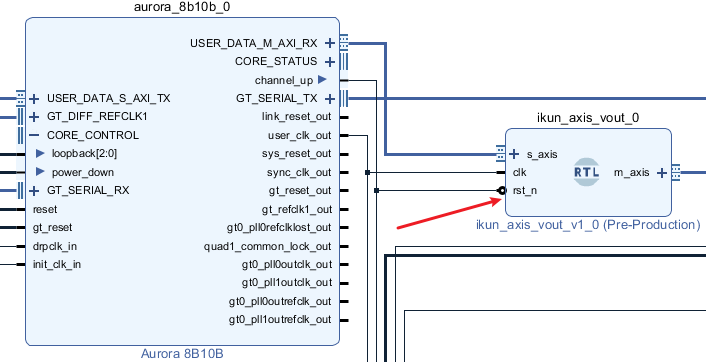

本方案在Aurora 8B10B上的應用

本方案在Aurora 8B10B上也有應用應用,可以參考我之前發布的博客,鏈接如下:

點擊直接前往

3、工程詳細設計方案

工程設計原理框圖

工程設計原理框圖如下:

輸入Sensor之–>OV5640攝像頭

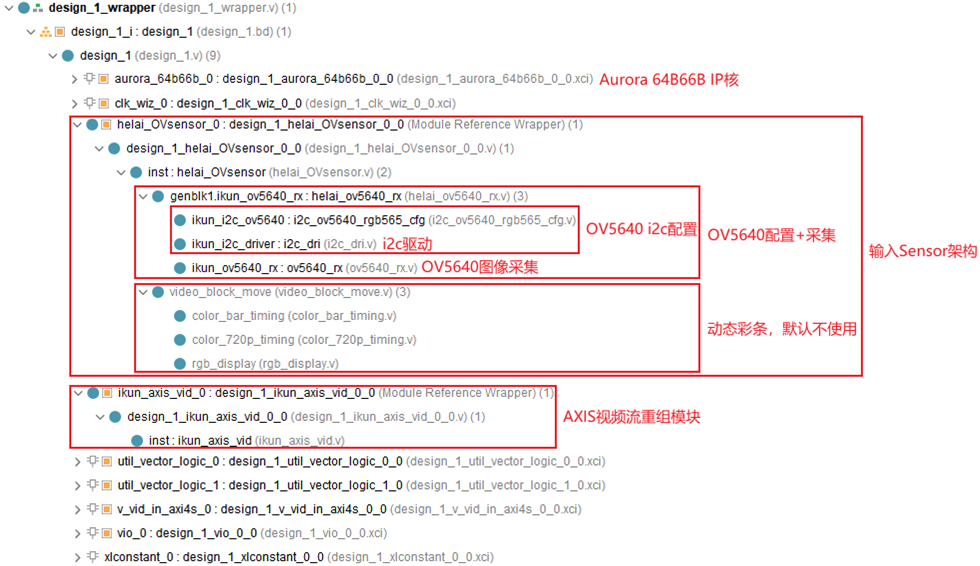

此模塊為點對點視頻發送端工程所獨有;輸入Sensor是本工程的輸入設備,其一為OV5640攝像頭,此外本博主在工程中還設計了動態彩條模塊,彩條由FPGA內部邏輯產生,且是動態移動的,完全可模擬Sensor,輸入源選擇Sensor還是彩條,通過Sensor模塊的頂層參數配置,默認選擇Sensor輸入;Sensor模塊如下:

SENSOR_TYPE=0;則輸出OV5640攝像頭采集的視頻;

SENSOR_TYPE=1;則輸出動態彩條的視頻;

OV5640攝像頭需要i2c初始化配置,本設計配置為1280x720@30Hz分辨率,本設計提供純verilog代碼實現的i2c模塊實現配置功能;此外,OV5640攝像頭還需要圖像采集模塊實現兩個時鐘輸出一個RGB565的視頻轉換為一個時鐘輸出一個RGB888視頻,本設計提供純verilog代碼實現的圖像采集模塊實現配置功能;動態彩條則由FPGA內部邏輯實現,由純verilog代碼編寫;將OV5640攝像頭配置采集和動態彩條進行代碼封裝,形成helai_OVsensor.v的頂層模塊,整個模塊代碼架構如下:

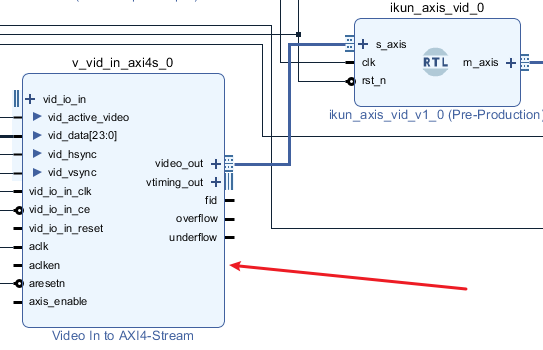

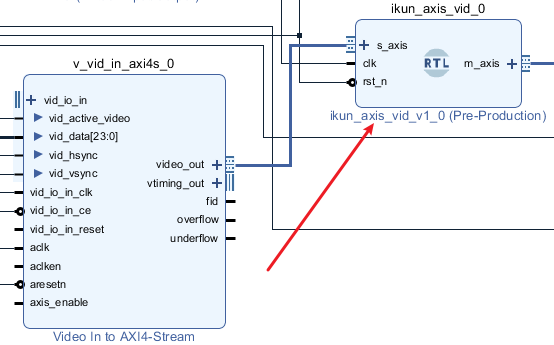

Native視頻轉AXIS流

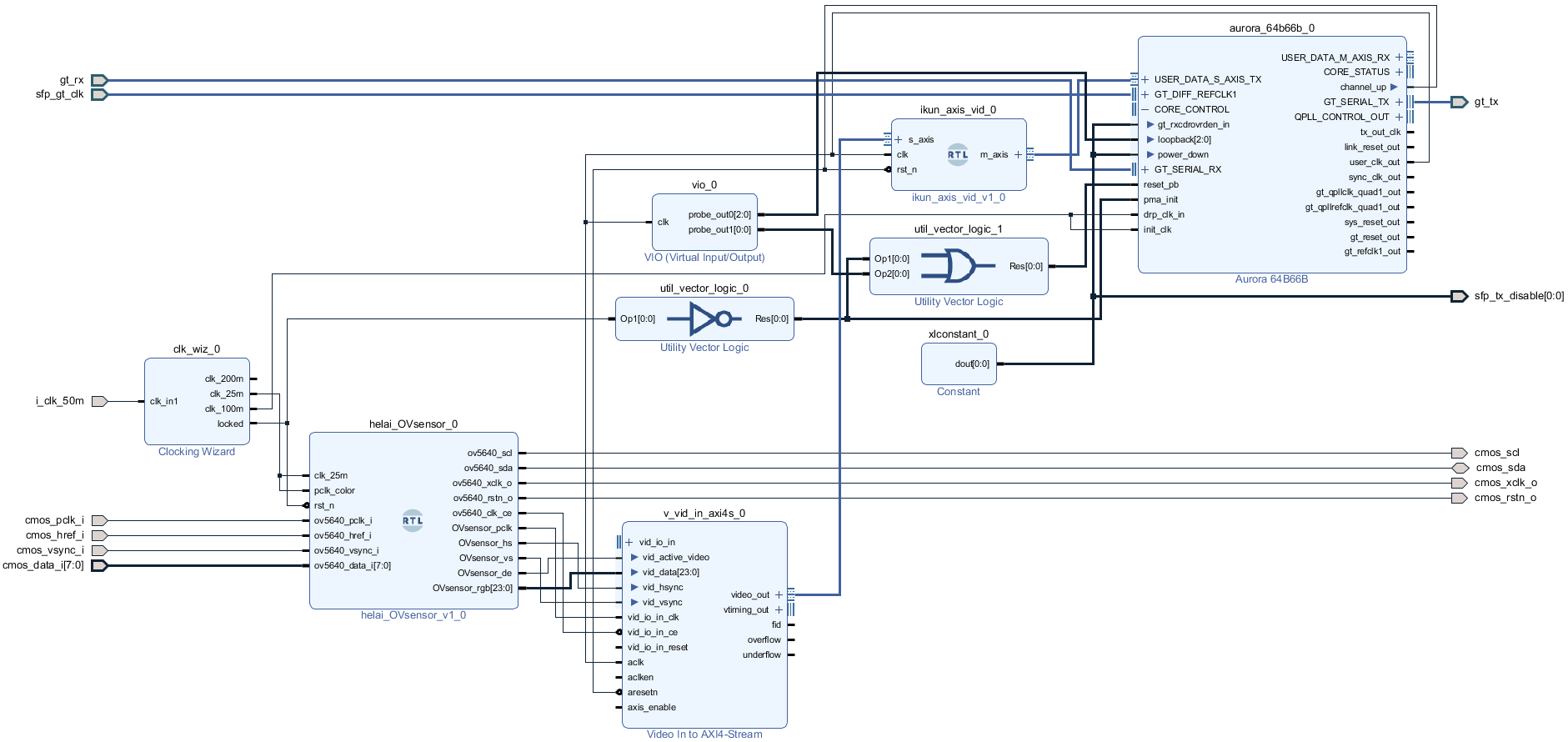

此模塊為點對點視頻發送端工程所獨有;然后采集視頻送入Xilinx官方的Video In To AXI4-Stream IP核實現Native視頻轉換到AXI4-Stream視頻流;如下:

AXIS視頻流重組

此模塊為點對點視頻發送端工程所獨有;然后AXI4-Stream視頻流再送入純verilog代碼實現的AXIS視頻流重組模塊實現信號重組,因為Aurora 8B10B發送接口不帶tuser信號,所以需要將tuser嵌入到數據流中傳輸;將AXIS視頻流重組模塊直接拖入Block Design中,如下:

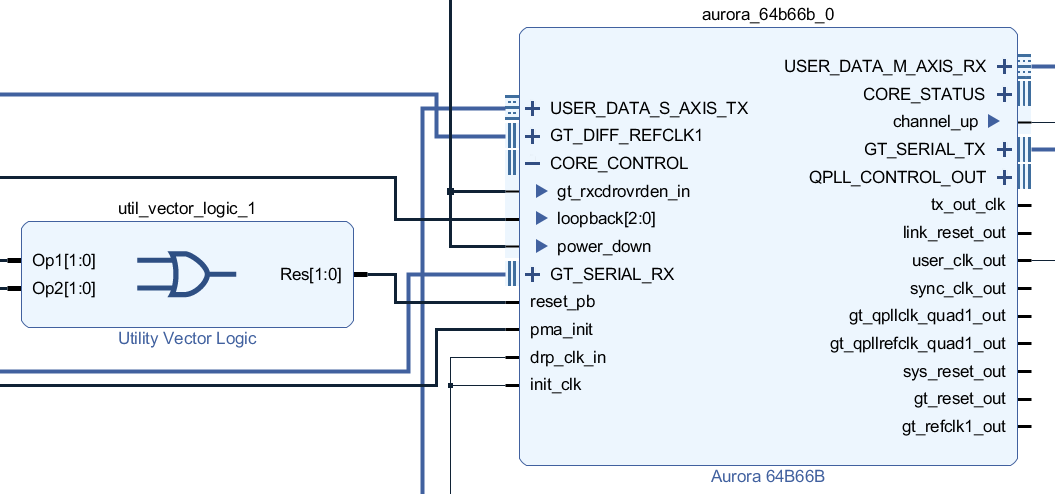

Aurora 64B66B視頻傳輸傳輸架構

Aurora 64B66B視頻傳輸傳輸架構在視頻點對點傳輸發送端和接收端都用到了;

然后視頻流送入Xilinx官方的Aurora 64B66B IP核實現64B66B數據編碼,數據以高速差分信號輸出,經板載的SFP光口進行回環傳輸;經SFP-RX接口輸入高速差分信號再進入Xilinx官方的Aurora 64B66B IP核實現64B66B數據解碼,輸出AXI4-Stream視頻流;本設計基于GTX高速收發器實現Aurora 64B66B圖像視頻傳輸,Aurora 64B66B在Block Design中如下:

Aurora 64B66B圖像視頻傳輸架構的核心是Aurora 64B66B IP核的例化和使用,所以本章節我們重點講解這個IP;

Aurora 64B66BIP核簡介

關于Aurora 64B66B IP核介紹最詳細的肯定是Xilinx官方的《pg074_Aurora 64B/66B LogiCORE IP Product Guide》,我們以此來解讀,《pg074》PDF文檔我已放在了資料包里;我用到的開發板FPGA型號為Xilinx–7系列FPGA;帶有多路GTX資源,每通道的收發速度為500 Mb/s到10.3125 Gb/s之間(GTX為例)。本設計使用的Aurora 64B66B IP核基于GTX高速收發器實現物理層和數據鏈路層;

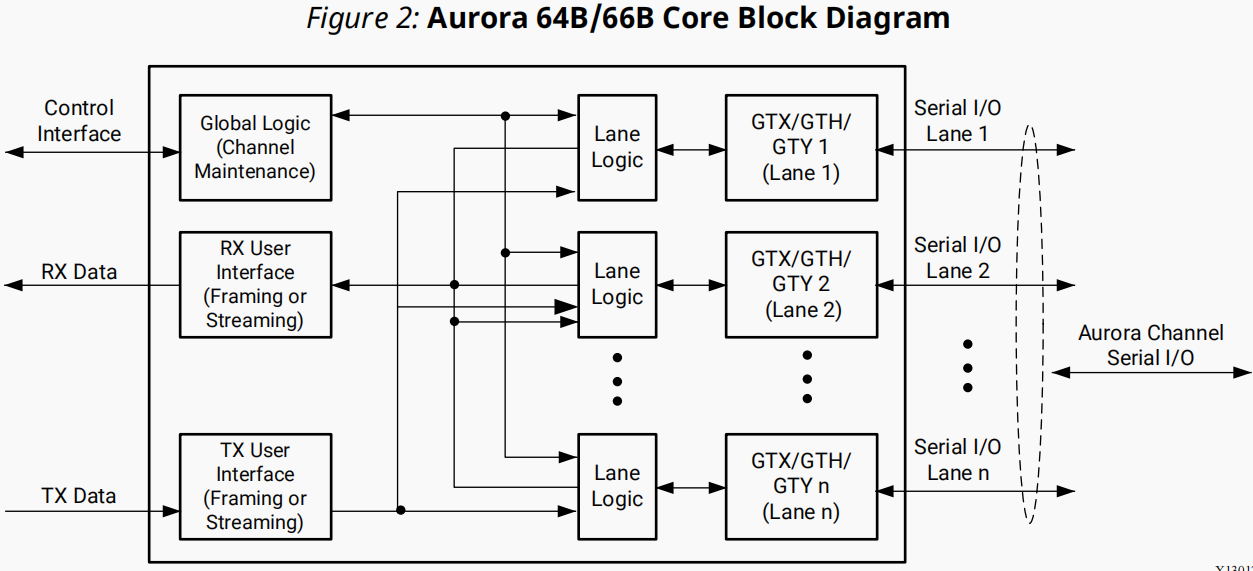

Aurora 64B66B 基本結構

根據《pg074_Aurora 64B/66B LogiCORE IP Product Guide》,Aurora 64B66B基本結構如下:

由上圖可知,Aurora 64B66B IP核由四個核心模塊構成,協同實現鏈路初始化、數據編解碼及流控制:

通道邏輯(Lane Logic)

功能:驅動每個GT收發器(GTX/GTH/GTY),初始化收發器硬件,處理64B66B編解碼、錯誤檢測(如CRC校驗)

關鍵操作:檢測控制字符(如空閑符、時鐘補償符),確保數據對齊

全局邏輯(Global Logic)

功能:管理多通道綁定(Lane Bonding),驗證通道同步狀態,生成隨機空閑字符維持鏈路活性,監控所有通道的錯誤(如hard_err硬件錯誤、soft_err位錯誤)

錯誤處理:檢測到嚴重錯誤時自動復位并重新初始化通道

發送用戶接口(TX User Interface)

接口類型:支持AXI4-Stream幀接口(帶tlast/tkeep)或流接口(簡化無幀控制)

功能:將應用層數據封裝為Aurora幀(添加SCP/ECP控制符),插入時鐘補償序列(每10,000字節插入12字節開銷)

接收用戶接口(RX User Interface)

功能:解析輸入數據流,剝離SCP/ECP控制符,恢復原始數據幀并通過AXI4-Stream輸出;支持流量控制(如UFC/NFC)

特點:無彈性緩沖,依賴實時流控避免溢出

用戶數據接口對比

Aurora 64B66B支持幀接口 (Framing) 流接口 (Streaming),對比如下:

Aurora 64B66B 發送流程

Aurora 64B66B用戶發送數據使用幀接口(AXI4-Stream),包括以下流程:

用戶發起傳輸

應用層置位s_axi_tx_tvalid并輸出數據至s_axi_tx_tdata,同時用s_axi_tx_tlast標識幀結束,s_axi_tx_tkeep標記末尾有效字節

IP核組幀

當s_axi_tx_tready與s_axi_tx_tvalid同時有效時,IP核采樣數據

組幀規則:

幀首添加2字節SCP(Start Channel Protocol)

幀尾添加2字節ECP(End Channel Protocol)

若數據字節數為奇數,末尾補PAD字符

插入控制序列

在數據間隙插入空閑字符或時鐘補償序列(CC),優先級高于數據傳輸

發送過程中可通過拉低s_axi_tx_tvalid暫停傳輸(流控)

串行化輸出

數據經GT收發器進行64B66B編碼,轉為串行信號通過物理鏈路發送

使用總結

以上流程為Aurora 64B66B IP核內部實現,開發者只需了解即可,無需關心起具體實現細節,開發者只需把發送數據轉換為AXI4-Stream數據流送入Aurora 64B66B用戶發送接口即可;

Aurora 64B66B 接收流程

數據解析

GT收發器接收串行數據,進行字對齊和64B66B解碼

通道邏輯檢測并剝離SCP、ECP、PAD及空閑字符,提取有效負載

幀恢復與輸出

恢復的數據通過AXI4-Stream接口輸出:

m_axi_rx_tvalid標識有效數據

m_axi_rx_tlast標識幀結束

m_axi_rx_tkeep標記幀末有效字節(僅當tlast有效時)

無流控信號:接收端無tready,需應用層實時消費數據

錯誤檢測

實時監測編解碼錯誤(置位soft_err)或幀結構錯誤(如連續SCP,置位frame_err)

使用總結

以上流程為Aurora 64B66B IP核內部實現,開發者只需了解即可,無需關心起具體實現細節,開發者只需把Aurora 64B66B IP核輸出的AXI4-Stream數據流送入自己的接收模塊即可進行具體分析和處理;

Aurora 64B66B 時鐘架構

Aurora 64B66B IP核涉及多時鐘域協同,關鍵時鐘信號如下:

時鐘交互要點:

跨時鐘域同步:INIT_CLK用于復位邏輯(gt_reset需同步至該時鐘域),避免亞穩態

用戶時鐘生成:USER_CLK由GT收發器的CDR(時鐘數據恢復)電路產生,確保與輸入數據同步

抖動要求:參考時鐘(GT_REFCLK)需滿足嚴格抖動限制(通常<1 ps RMS),否則高線速下鏈路失鎖

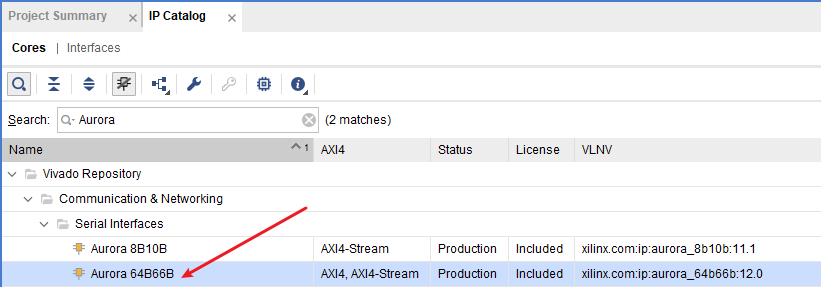

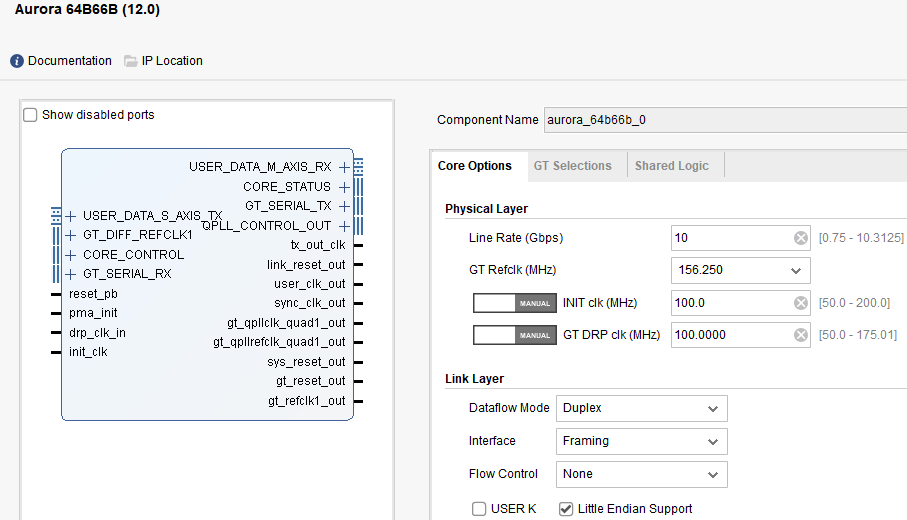

Aurora 64B66B IP核調用和使用

Aurora 64B66B IP核調用和使用很簡單,通過vivado的UI界面即可完成,如下:

然后配置如下:

具體配置要根據自己的項目需求而定,上圖只是博主的配置,僅供參考;

AXIS視頻流恢復

此模塊為點對點視頻接收端工程所獨有;AXI4-Stream視頻流再送入純verilog代碼實現的AXIS視頻流重組模塊實現信號恢復,因為Aurora 8B10B接收接口不帶tuser信號,所以需要在嵌入數據中的tuser恢復出來;將AXIS視頻流恢復模塊直接拖入Block Design中,如下:

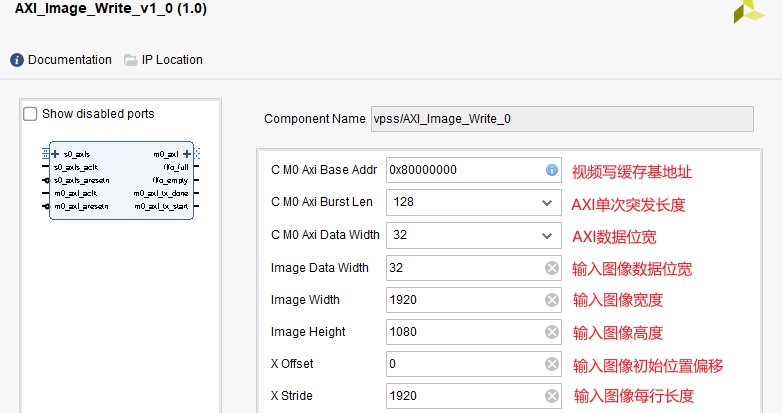

AXIS視頻流寫緩存

此模塊為點對點視頻接收端工程所獨有;然后AXI4-Stream視頻流送入本博主自研的純verilog實現的、AXI4-Stream接口的圖像寫緩存模塊,實現視頻寫入DDR緩存操作;AXIS視頻流寫緩存模塊代碼架構如下:

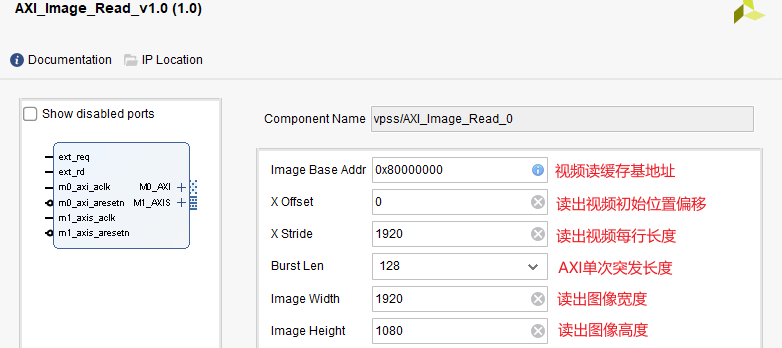

AXIS視頻流寫緩存模塊配置項如下:

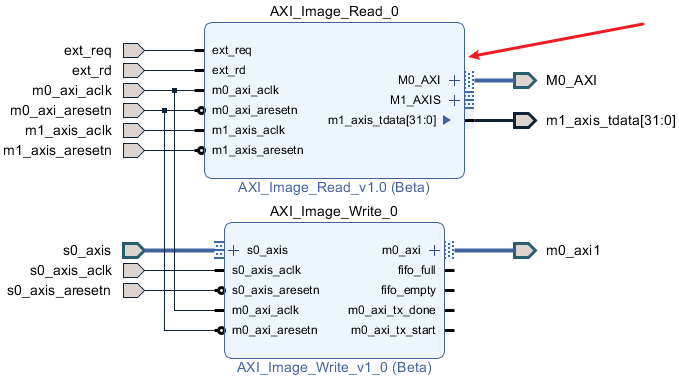

AXIS視頻流寫緩存模塊配置在Block Design中如下:

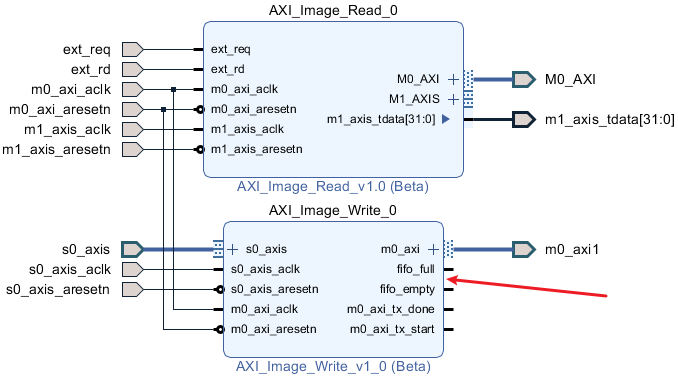

AXIS視頻流讀緩存

此模塊為點對點視頻接收端工程所獨有;然后使用本博主自研的純verilog實現的、AXI4-Stream接口的圖像讀緩存模塊,實現視頻從DDR讀出操作;AXIS視頻流寫緩存模塊代碼架構如下:

AXIS視頻流讀緩存模塊配置項如下:

AXIS視頻流讀緩存模塊配置在Block Design中如下:

HDMI視頻輸出架構

此模塊為點對點視頻接收端工程所獨有;緩存圖像從DDR3讀出后經過Native時序生成模塊輸出標準的VGA時序視頻,然后經過純verilog顯示的RGB轉HDMI模塊輸出HDMI差分視頻;最后送顯示器顯示即可;代碼例化如下:

點對點視頻發送端工程源碼架構

提供1套工程源碼,以工程源碼1為例,工程Block Design設計如下:

提供4套工程源碼,以工程源碼1為例,綜合后的工程源碼架構如下:

點對點視頻接收端工程源碼架構

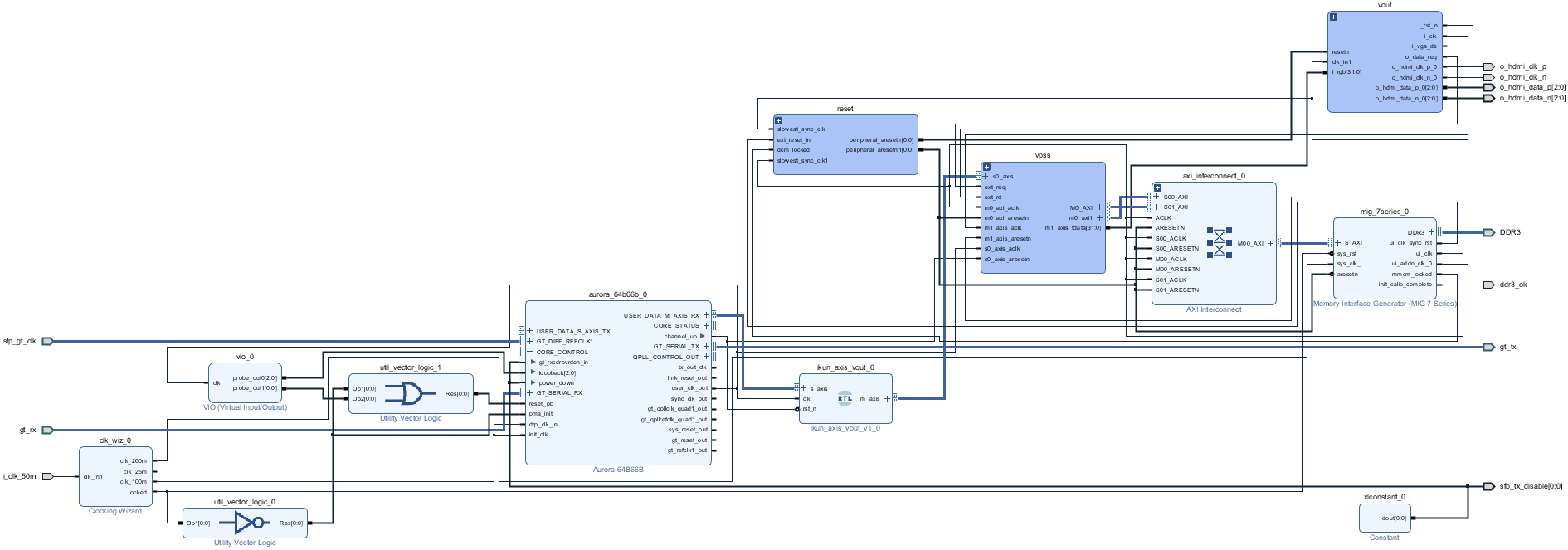

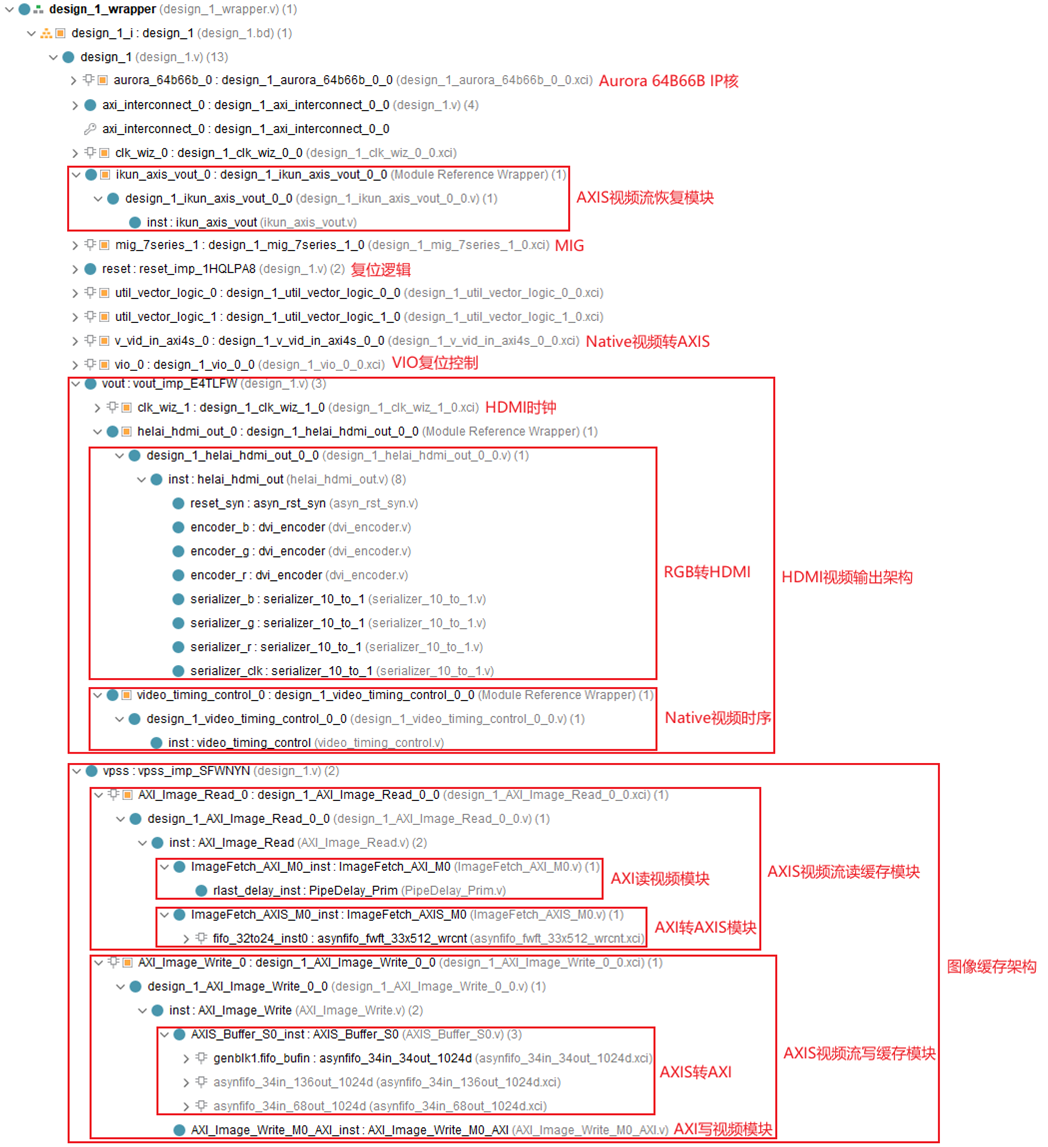

提供4套工程源碼,以工程源碼2為例,工程Block Design設計如下:

提供4套工程源碼,以工程源碼2為例,綜合后的工程源碼架構如下:

工程源碼3、4使用了Zynq7100;PL端時鐘由Zynq軟核提供,所以需要運行運行SDK以啟動Zynq,所以需要在SDK里運行一個簡單的hello world程序,SDK軟件代碼架構如下:

4、vivado工程源碼1詳解–>Kintex7–325T,點對點OV5640視頻轉SFP光口發送

開發板FPGA型號:Kintex7–325T–xc7k325tffg676-2;

FPGA開發環境:Vivado2019.1;

輸入:OV5640攝像頭或動態彩條,分辨率1280x720@30Hz;

輸出:SFP光口,分辨率1280x720@60Hz;

光編碼方案:Xilinx Aurora 64B66B IP核;

回環光口類型:1路SFP光口;

高速收發器類型:GTX,線速率10Gbps;

Aurora 64B66B用戶數據位寬:64 bit;

實現功能:FPGA實現Aurora 64B66B圖像視頻傳輸;

工程作用:此工程目的是讓讀者掌握FPGA實現Aurora 64B66B圖像視頻傳輸的設計能力,以便能夠移植和設計自己的項目;

工程Block Design和工程代碼架構請參考第3章節的《工程源碼架構》小節內容;

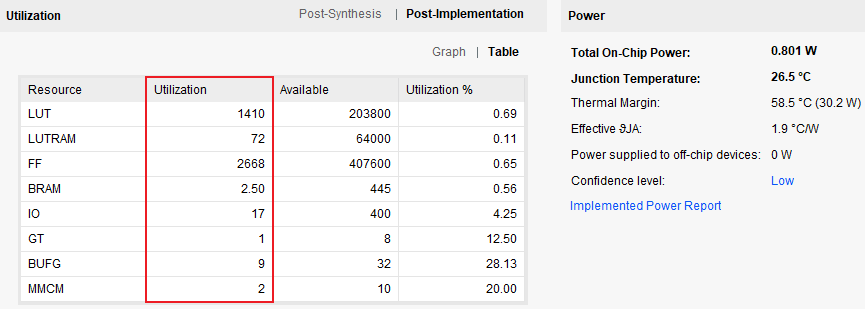

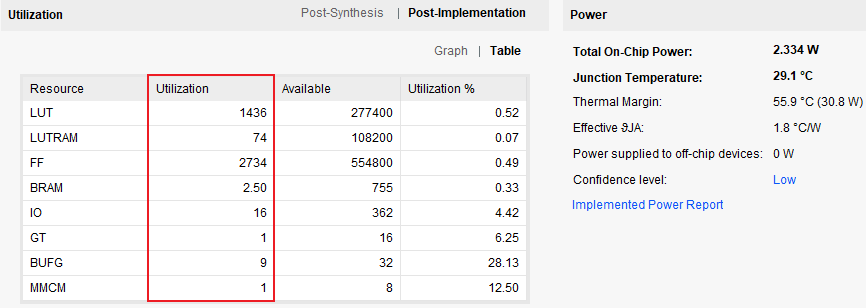

工程的資源消耗和功耗如下:

5、vivado工程源碼2詳解–>Kintex7–325T,點對點SFP光口接收OV5640視頻轉HDMI

開發板FPGA型號:Kintex7–325T–xc7k325tffg676-2;

FPGA開發環境:Vivado2019.1;

輸入:SFP光口,分辨率1280x720@60Hz;

輸出:HDMI,RTL邏輯編碼,分辨率1280x720@60Hz;

光編碼方案:Xilinx Aurora 64B66B IP核;

回環光口類型:1路SFP光口;

高速收發器類型:GTX,線速率10Gbps;

Aurora 64B66B用戶數據位寬:64 bit;

實現功能:FPGA實現Aurora 64B66B圖像視頻傳輸;

工程作用:此工程目的是讓讀者掌握FPGA實現Aurora 64B66B圖像視頻傳輸的設計能力,以便能夠移植和設計自己的項目;

工程Block Design和工程代碼架構請參考第3章節的《工程源碼架構》小節內容;

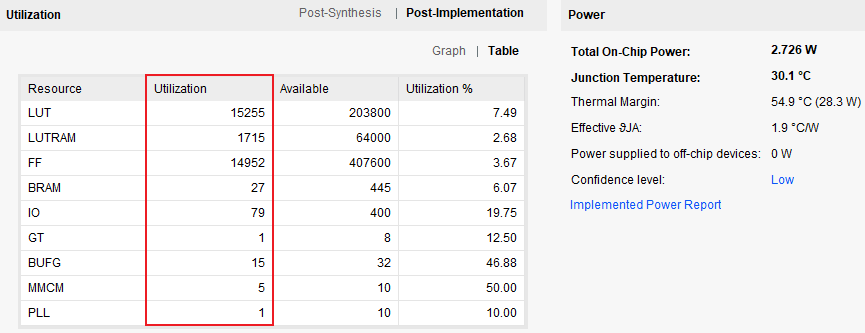

工程的資源消耗和功耗如下:

6、vivado工程源碼3詳解–>Zynq7100,點對點OV5640視頻轉SFP光口發送

開發板FPGA型號:Zynq7100–xc7z100ffg900-2;

FPGA開發環境:Vivado2019.1;

輸入:OV5640攝像頭或動態彩條,分辨率1280x720@30Hz;

輸出:SFP光口,分辨率1280x720@60Hz;

光編碼方案:Xilinx Aurora 64B66B IP核;

回環光口類型:1路SFP光口;

高速收發器類型:GTX,線速率10Gbps;

Aurora 64B66B用戶數據位寬:64 bit;

實現功能:FPGA實現Aurora 64B66B圖像視頻傳輸;

工程作用:此工程目的是讓讀者掌握FPGA實現Aurora 64B66B圖像視頻傳輸的設計能力,以便能夠移植和設計自己的項目;

工程Block Design和工程代碼架構請參考第3章節的《工程源碼架構》小節內容;

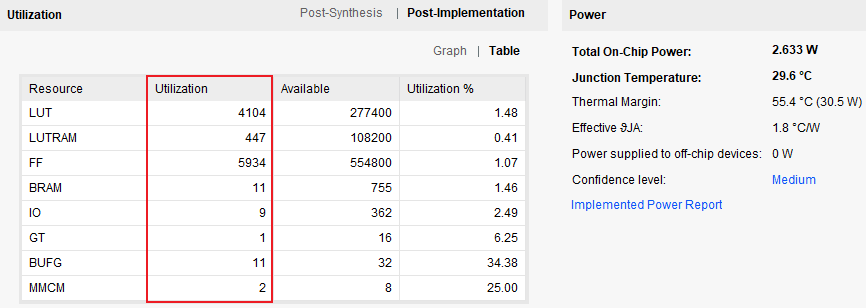

工程的資源消耗和功耗如下:

7、vivado工程源碼4詳解–>Zynq7100,點對點SFP光口接收OV5640視頻轉HDMI

開發板FPGA型號:Zynq7100–xc7z100ffg900-2;

FPGA開發環境:Vivado2019.1;

輸入:SFP光口,分辨率1280x720@60Hz;

輸出:HDMI,RTL邏輯編碼,分辨率1280x720@60Hz;

光編碼方案:Xilinx Aurora 64B66B IP核;

回環光口類型:1路SFP光口;

高速收發器類型:GTX,線速率10Gbps;

Aurora 64B66B用戶數據位寬:64 bit;

實現功能:FPGA實現Aurora 64B66B圖像視頻傳輸;

工程作用:此工程目的是讓讀者掌握FPGA實現Aurora 64B66B圖像視頻傳輸的設計能力,以便能夠移植和設計自己的項目;

工程Block Design和工程代碼架構請參考第3章節的《工程源碼架構》小節內容;

工程的資源消耗和功耗如下:

8、工程移植說明

vivado版本不一致處理

1:如果你的vivado版本與本工程vivado版本一致,則直接打開工程;

2:如果你的vivado版本低于本工程vivado版本,則需要打開工程后,點擊文件–>另存為;但此方法并不保險,最保險的方法是將你的vivado版本升級到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解決如下:

打開工程后會發現IP都被鎖住了,如下:

此時需要升級IP,操作如下:

FPGA型號不一致處理

如果你的FPGA型號與我的不一致,則需要更改FPGA型號,操作如下:

更改FPGA型號后還需要升級IP,升級IP的方法前面已經講述了;

其他注意事項

1:由于每個板子的DDR不一定完全一樣,所以MIG IP需要根據你自己的原理圖進行配置,甚至可以直接刪掉我這里原工程的MIG并重新添加IP,重新配置;

2:根據你自己的原理圖修改引腳約束,在xdc文件中修改即可;

3:純FPGA移植到Zynq需要在工程中添加zynq軟核;

9、上板調試驗證

準備工作

需要準備的器材如下:

FPGA開發板,沒有開發板可以找本博提供;

SFP光模塊和光纖;

我的開發板了連接如下:

Aurora 64B66B 視頻點對點傳輸效果演示

Aurora 64B66B光口視頻點對點傳輸效果演示如下:

FPGA實現Aurora 64B66B圖像視頻傳輸

10、工程代碼的獲取

代碼太大,無法郵箱發送,以某度網盤鏈接方式發送,

資料獲取方式:文章末尾的V名片。

網盤資料如下:

此外,有很多朋友給本博主提了很多意見和建議,希望能豐富服務內容和選項,因為不同朋友的需求不一樣,所以本博主還提供以下服務:

![[機器學習]08-基于邏輯回歸模型的鳶尾花數據集分類](http://pic.xiahunao.cn/[機器學習]08-基于邏輯回歸模型的鳶尾花數據集分類)