這里的 K 表示 千歐(kilo-ohm),而 F 在很多國產 EDA 軟件(比如立創EDA、Altium 的一些中文封裝庫)里用來標注精度(公差),

-

F 代表 ±1% 精度(英文 Fine tolerance)。

-

其他常見標法:

-

J → ±5%

-

K → ±10%

-

M → ±20%

-

-

10KF = 10 kΩ ±1%

MP2451 簡介

MP2451 是 Monolithic Power Systems(MPS)推出的一款高頻率(2 MHz)、最大輸出約 0.6 A 的降壓穩壓器,輸入電壓范圍從 3.3 V 至 36 V,廣泛用于汽車、工業、分布式電源等領域。它采用 SOT-23-6 或 TSOT-23-6 封裝,具備高效率、內部軟啟動、頻率衰減保護等特性

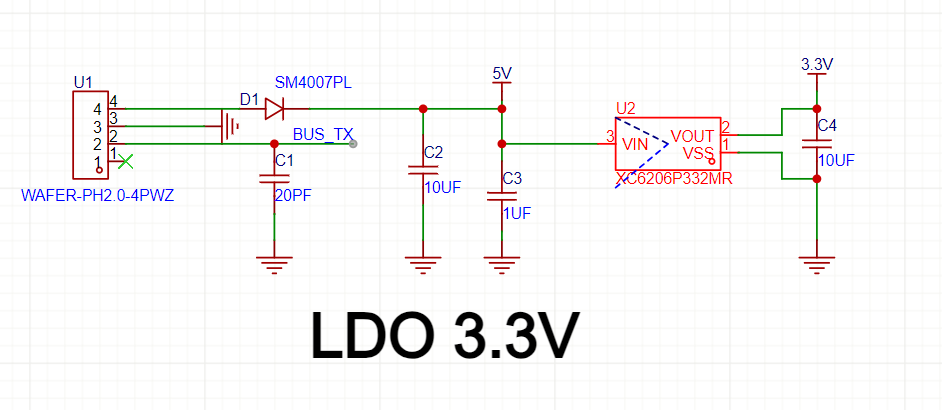

目前我用的5V轉3.3V的LDO電路,如圖所示:

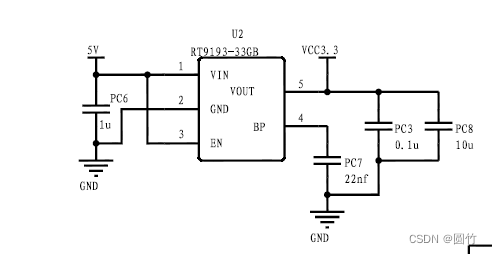

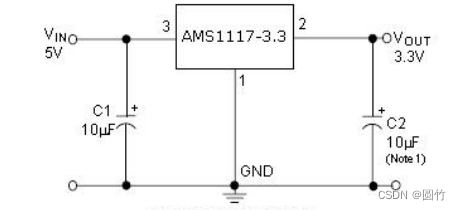

下面的是我借鑒的電路:RT9193和ASM1117

上述款為LDO穩壓器組成的5V轉3.3V電路,LDO電路相對于DCDC電路外圍電路簡單,僅需要幾個電容即可。則兩款電路都是常用的3.3V電路,只是價格稍有差異。

關于DCDC電路設計我的總結是一下幾點:

1.確定需求(輸入電壓,輸出電壓,負載電流);

2.選擇芯片(價格、封裝、供貨情況);

3.根據芯片規格書確定電路設計(輸入電容、輸出電容、輸出電感、輸出電壓配置等),需要考慮降額設計。

降額設計:降額設計(Derating Design)就是在電路設計時,不讓元器件長時間工作在它們的最大額定值附近,而是降低一定比例來使用,以提升可靠性和壽命。“元器件“吃七分飽”比“天天撐到極限”更耐用。”

PCB設計注意事項:

實際應用中PCBlayout中要注意的事項:

1)輸入電容盡量靠近Vin引腳,減少寄生電感的存在,因為輸入電流不連續,寄生電感引起的噪聲對芯片的耐壓以及邏輯單元造成不良影響 。輸出濾波電容盡量靠近Vout引腳;

2)功率回路盡可能的短粗,保持較小的環路面積,較少噪聲輻射。SW是噪聲源,保證電流的同時保持盡量小的面積,遠離敏感的易受干擾的位置。如,電感靠近SW引腳,遠離反饋線。輸出電容靠近電感,地端增加地過孔;

3)加粗地線寬度或者接地銅皮面積,如果不同層,要多打地孔;

4)反饋電阻盡量靠近FB引腳,從RFB到FB引腳的連線盡量短,因為這段線極易受到干擾,對輸出特性影響較大;大電流負載的FB在負載遠端取,反饋電容走線要就近取。

5)電感盡量選取屏蔽類型的,電感正下方所在區域不要有地線,電感量輻射容易影響地平面電平,電感下方的Bottom Layer布線影響不大。

6)芯片散熱要按設計要求,盡量在底下增加過孔散熱。

RFB到FB引腳的連線盡量短,因為這段線極易受到干擾,對輸出特性影響較大;大電流負載的FB在負載遠端取,反饋電容走線要就近取。

5)電感盡量選取屏蔽類型的,電感正下方所在區域不要有地線,電感量輻射容易影響地平面電平,電感下方的Bottom Layer布線影響不大。

6)芯片散熱要按設計要求,盡量在底下增加過孔散熱。

?

詳細請參考這篇文章:學習筆記之——DCDC降壓芯片基本原理及選型主要參數介紹-CSDN博客

DCDC芯片選型

DCDC Buck電源芯片選型_buck芯片選型-CSDN博客

電感的作用:“電感阻流變,儲能靠磁場,高頻它擋路,低頻它放行。”

1.儲能與釋放

-

電感本質上是將電能以磁場的形式儲存的元件。

-

當電流通過電感線圈時,會在周圍產生磁場;當電流變化時,磁場會變化,從而根據法拉第電磁感應定律在電感兩端產生感應電動勢(EMF)。

-

特點:電感會阻礙電流的變化(抗變化性),電流變化越快,感應電壓越大。

-

上升快 → 產生反向電壓阻止電流增大

-

下降快 → 產生正向電壓阻止電流減小

-

2.濾波與抗干擾

-

低通濾波:電感對高頻信號阻抗大、對低頻信號阻抗小,所以常用于平滑電流、去除高頻噪聲。

-

在開關電源(DCDC)中,電感與電容配合形成LC濾波器,降低紋波。

-

在電源輸入端,電感(或共模電感)可以抑制電磁干擾(EMI)。

3.諧振與信號處理

-

電感與電容并聯或串聯可以構成諧振電路(LC電路),用于無線電調諧、信號選擇、頻率合成等。

-

在射頻電路中,電感用于匹配阻抗、調節頻率。

4.典型應用:

-

DCDC開關電源:存儲能量并平滑輸出電流。

-

濾波電路:與電容配合去除高頻噪聲。

-

電機驅動:抑制電流突變,保護開關器件。

-

無線充電/射頻:與電容構成諧振回路。

LOAD 在電子、電路和工程中一般指 “負載”,意思是由電源、信號源等驅動或供電的對象。

它可以是一個元器件、一組電路、甚至是整個設備。

![[機器學習]08-基于邏輯回歸模型的鳶尾花數據集分類](http://pic.xiahunao.cn/[機器學習]08-基于邏輯回歸模型的鳶尾花數據集分類)