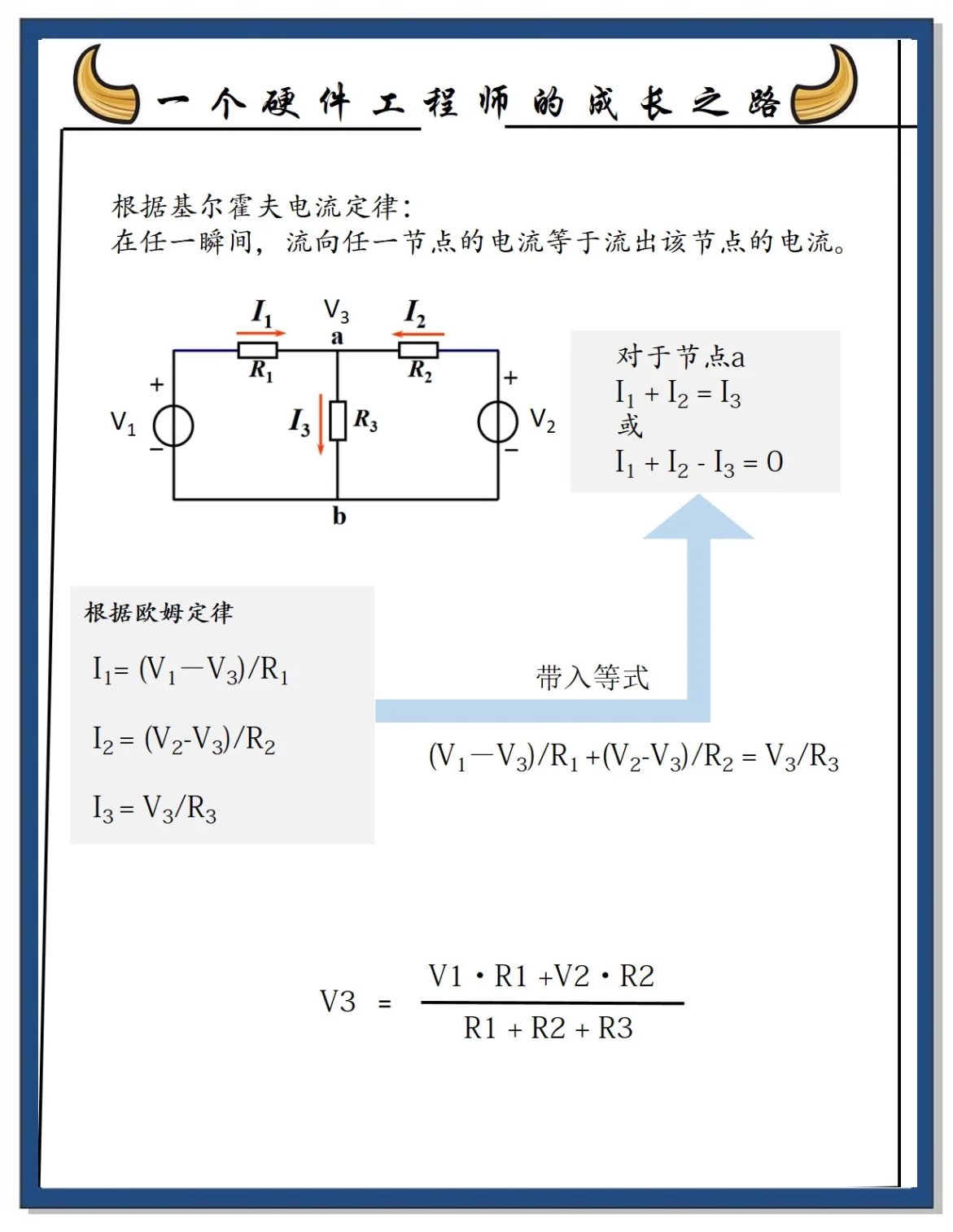

一、電路基礎:硬件設計的底層邏輯

1.1 基爾霍夫定律的硬件實現

// STM32驗證KVL定律(ADC采樣法)

void verify_kvl() {ADC_Enable(ADC1); // 啟用ADCfloat Vr1 = read_ADC(PA0) * 3.3 / 4096; // 讀取R1電壓float Vr2 = read_ADC(PA1) * 3.3 / 4096; // 讀取R2電壓float Vsrc = 3.3; // 電源電壓// KVL驗證: ΣV = Vsrc - Vr1 - Vr2 ≈ 0if(fabs(Vsrc - Vr1 - Vr2) < 0.05) {UART_Send("KVL驗證通過!誤差<50mV\n");} else {UART_Send("警告:電路存在異常損耗!\n");}

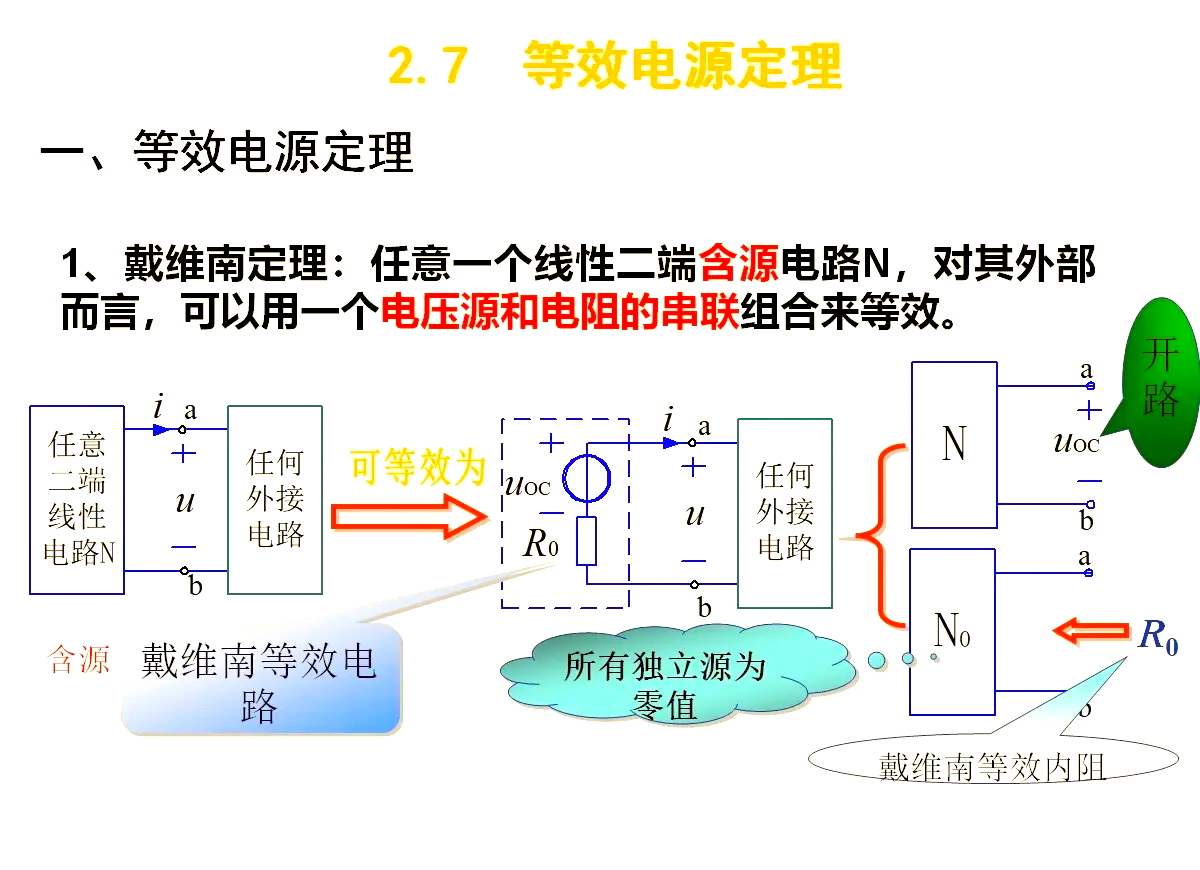

}1.2 戴維南等效的工程應用

鋰電池供電系統等效模型:

+-----------------+

[18650 3.7V]─┤ 內阻Rint=80mΩ ├───┬──[負載]+-----------------+ │[C=100μF] // 去耦電容│GND設計公式:

# Python計算最大輸出功率

def max_power(V_oc, R_int):return (V_oc**2) / (4 * R_int) # 當R_load = R_int時print(f"18650最大功率: {max_power(3.7, 0.08):.2f}W") # 輸出: 42.91W二、模擬電子:信號鏈設計精髓

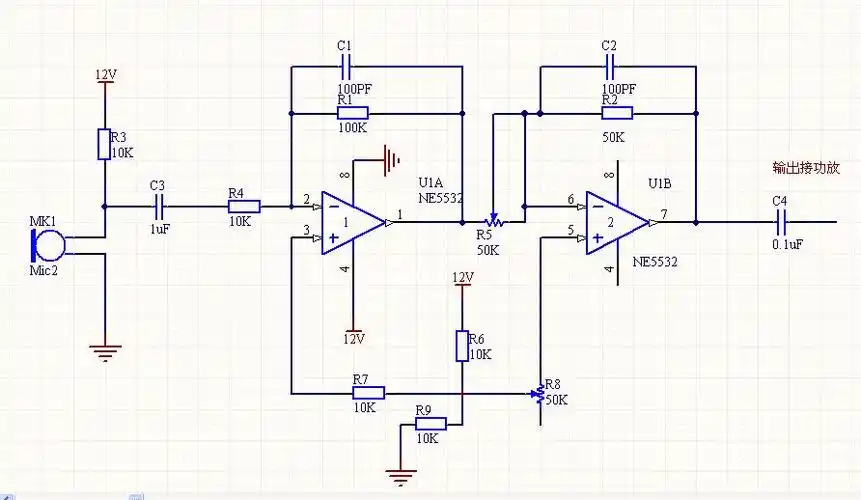

2.1 多級放大系統設計

麥克風→前置放大→功率放大→揚聲器:

text

復制

下載

[Mic]─┬─[2.2kΩ]─┐│ ▼├─[OPA2171]───[10kΩ]─┬─[LM386]─┬─[SPK]└───[1MΩ]?───[100nF]─┘ │[220μF]─┘

?

?

2.2 有源濾波器實戰

// Verilog實現數字濾波器 (FPGA版本)

module lowpass_filter(input clk, input [11:0] adc_data,output reg [11:0] filtered

);reg [31:0] accumulator;

parameter ALPHA = 0.05; // 截止頻率調整因子always @(posedge clk) beginaccumulator <= accumulator + (adc_data - accumulator) * ALPHA;filtered <= accumulator >> 16; // 位寬調整

end

endmodule三、數字系統:硬件加速之道

3.1 高速計數器設計

FPGA實現32位100MHz計數器:

module high_speed_counter(input clk_100m,input reset_n,output reg [31:0] count

);always @(posedge clk_100m or negedge reset_n) beginif(!reset_n) count <= 32'd0;else count <= count + 1'b1;

end// 時序約束(XDC文件)

create_clock -period 10 [get_ports clk_100m]

set_input_delay -clock clk_100m 2 [all_inputs]3.2 狀態機硬件實現

電機控制狀態機:

// C語言實現狀態機(ARM Cortex-M)

typedef enum {STOP, ACCEL, RUN, BRAKE

} MotorState;void motor_control() {static MotorState state = STOP;switch(state) {case STOP:if(start_btn) {PWM_SetDuty(10);state = ACCEL;}break;case ACCEL:if(current_speed >= target) {state = RUN;} else {PWM_Increase(1);}break;// ...其他狀態}

}四、電源設計:硬件系統的生命線

4.1 高效Buck電源設計

PCB布局關鍵點:

+---------+ +------------+│ Vin ├────?│ SW Node │?─[注意最小回路面積!]+---------+ +------┬-----+[10μF陶瓷] ▼[電感]▼+---------+ +------┴-----+│ GND ?─────┤ 輸出電容 │?──[3×22μF陶瓷]+---------+ +------------+4.2 電源完整性分析

# Python計算目標阻抗

def calc_target_impedance(dv, di, dt):return dv / (di/dt) # 瞬態響應要求# 示例:CPU核心供電需求

dv = 0.05 # 允許紋波50mV

di = 15 # 負載瞬變15A

dt = 1e-6 # 響應時間1μs

print(f"目標阻抗: {calc_target_impedance(dv, di, dt):.3f}Ω") # 3.33mΩ五、綜合項目:智能溫控系統

硬件架構:

[DS18B20]───[STM32]───[OLED]│ ├───[繼電器]─[加熱器]│ └───[ESP32]─┬─[手機APP]│ └─[云平臺][ADC]─[NTC熱敏電阻]關鍵代碼實現:

// 溫度控制PID核心算法

void PID_Update(float setpoint, float actual) {static float integral = 0;static float last_error = 0;float error = setpoint - actual;// PID參數const float Kp = 2.0, Ki = 0.01, Kd = 1.0;// 抗積分飽和處理if(fabs(error) < 5.0) {integral += error;}float derivative = error - last_error;float output = Kp*error + Ki*integral + Kd*derivative;// 輸出限幅output = constrain(output, 0, 100);PWM_SetDuty(output);last_error = error;

}硬件工程師生存法則

信號完整性(SI)黃金三原則:

關鍵信號:阻抗控制 ±10%

時鐘走線:長度匹配 ±50mil

高速差分:等長 ±5mil

電磁兼容(EMC)設計:

# EMC優化層級 1. 源頭抑制 → 2. 路徑阻斷 → 3. 受體保護│ │ │▼ ▼ ▼[斜率控制] [屏蔽罩] [濾波電路][展頻技術] [地分割] [布局優化]熱設計公式:

T_j = T_a + (P_d × θ_ja) ▏ ▏ T_j:結溫(℃) ▏ T_a:環境溫度(℃) ▏ P_d:器件功耗(W) ▏ θ_ja:熱阻(℃/W)

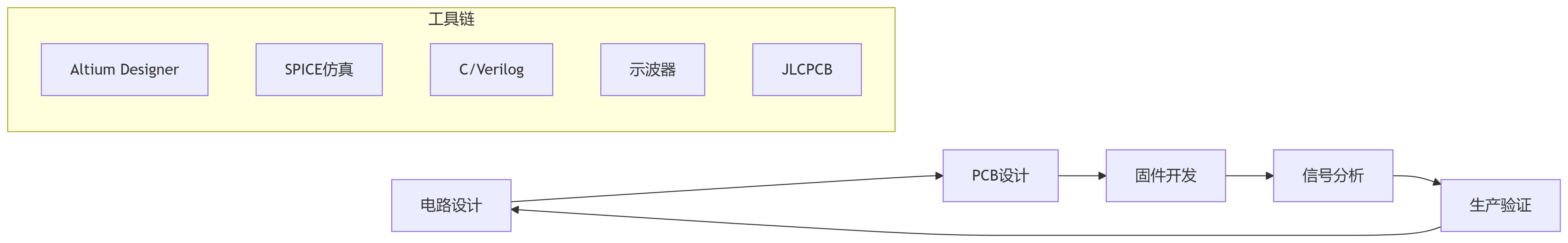

硬件開發技術棧

硬件工程師的終極信條:

“示波器不會說謊,但只有理解電磁場本質的人才能聽懂它的語言。真正的硬件大師,既能在SPICE仿真中預測納秒級的信號振鈴,也能在PCB上雕刻出滿足EMC標準的藝術品,更能用C語言賦予硅片以智能生命。”