哼?……這是什么意思?……

多年來,流行的觀點是 PCB 通孔本質上是電容性的,因此可以用集總電容器進行建模。雖然當信號的上升時間大于或等于過孔不連續性延遲的 3 倍時,這可能是正確的,但我將向您展示為什么不再適合這樣思考;繼續使用這種方法對高速通道進行建模甚至有風險。

讓我們通過說 via 是具有過大寄生電容或電感的傳輸線來開始討論。當過孔的阻抗等于連接到它們的傳輸線的特性阻抗時,它們被認為是透明的。在幾乎所有情況下,通過多層 PCB 的通孔都是電容性的,因為通孔桶和反焊盤之間存在分布電容。因此,它們最終的阻抗低于連接到它們的走線。與任何其他傳輸線一樣,當信號的上升沿遇到較低的阻抗時,它將在不連續性的長度上引起負反射。

回到正題,最好用圖 1 中總結的示例來演示。考慮在長 50 歐姆傳輸線的遠端有一個過孔。過孔有一個短的直通部分和一個長的短截線部分。通孔截面為 15 mils,短截線為 269 mils,總通孔長度為 284 mils。這對于現代背板設計來說并不罕見。

對于這種特定的過孔幾何形狀,阻抗為 33 歐姆,超出的過孔電容為 1.9pf。即使源極有 50ps 的快速上升時間,當信號到達遠端的過孔時,上升時間也會因有損電介質引起的色散而降低。在此示例中,在 23 英寸之后,上升時間已降至大約 230ps。

如果過孔不連續性的總延遲 (TD) 為 60 ps,則過孔處的 230 ps 上升時間大于 3TD (180ps)。正如預期的那樣,當使用等于過剩電容的集總電容器對過孔進行建模,并將其與傳輸線過孔模型進行比較時,使用 230ps 上升時間時,反射的 TDR 圖幾乎相同。

?

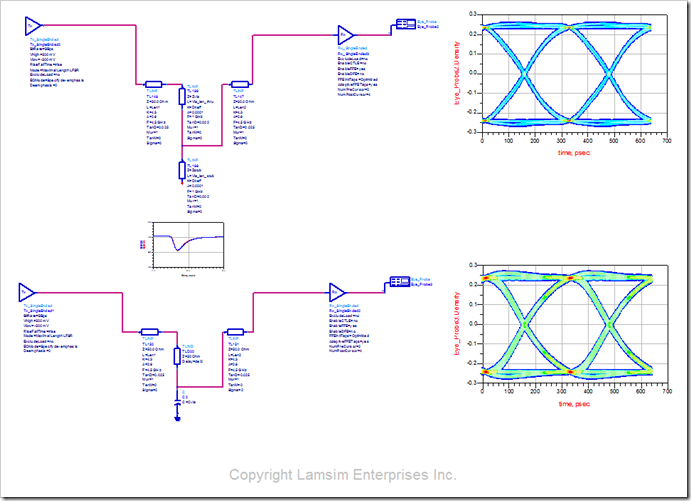

圖 1:23 英寸后的 Via 型號 TDR 比較。頂部拓撲將 33 歐姆傳輸線用于過孔的直通和短截線部分。底部拓撲結構對過孔進行建模,其中一條 50 歐姆傳輸線表示直通部分的延遲,一個 1.9pf 電容器表示過剩的電容。使用?Agilent ADS?進行建模和仿真。

到目前為止一切都很好,對吧?嗯,也許是這樣。了解的唯一方法是進一步探索此拓撲并比較眼圖。假設您的電路需要以 3.125 GB/s 的 XAUI 速率工作。您可以通過添加驅動程序和接收器來修改這兩個拓撲。仿真后,您最終會得到如圖 2 所示的眼圖。

?

圖 2 3.125Gb/s 時的眼圖比較。頂部拓撲將 33 歐姆傳輸線用于過孔的直通和短截線部分。底部拓撲結構對過孔進行建模,其中一條 50 歐姆傳輸線表示直通部分的延遲,一個 1.9pf 電容器表示過剩的電容。使用?Agilent ADS?進行建模和仿真。

還是好的。那么,你可能會問,你的意思是什么?

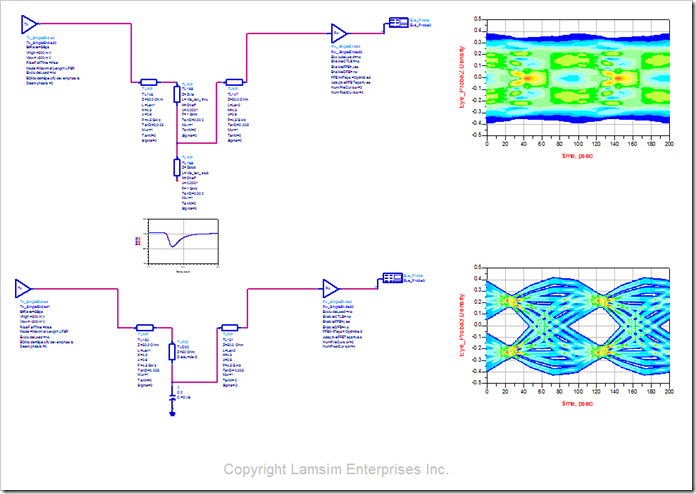

你說得對,你評論說有一個很好的反射匹配,眼睛睜得大大的。啊,但現在讓我們假設你想在未來以 10GB/s 的速度運行它。因此,您需要調高發射器的比特率,并再次仿真兩種拓撲。但這一次,您會得到一些意想不到的結果,如圖 3 所示。

?

圖 3 10Gb/s 時的眼圖比較。頂部拓撲將 33 歐姆傳輸線用于過孔的直通和短截線部分。底部拓撲結構對過孔進行建模,其中一條 50 歐姆傳輸線表示直通部分的延遲,一個 1.9pf 電容器表示過剩的電容。使用?Agilent ADS?進行建模和仿真。

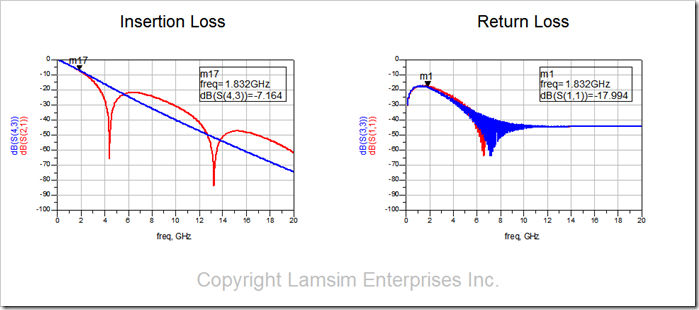

哎喲!這里發生了什么?查看 TDR,通道末端的反射看起來相同,那么為什么接收眼不匹配呢?要回答這個問題,我們真的需要看一下兩個通道的 S 參數圖。圖 4 顯示了兩種拓撲的插入和回波損耗。紅色是傳輸線模型,藍色是電容器模型。

?

圖 4 兩種拓撲的插入和回波損耗。紅色曲線是傳輸線過孔模型,藍色曲線是電容器模型。

插入損耗圖表示傳輸的輸出功率與頻率的關系,而回波損耗是反射功率與頻率的關系。在時域中,插入損耗和回波損耗分別等效于 TDT 和 TDR 圖。如您所見,Return loss 匹配得非常好;就像我們之前觀察到的 TDR 圖一樣,但只有當我們查看插入損耗圖時,圖 3 眼圖差異的真正原因才會很明顯。

請注意,第一個諧振零點位于大約 4.5 GHz。這個 null 表示四分之一波諧振頻率?fo,是由于長 269 mil 的過孔短截線。13.5GHz 的另一個零點是?fo?的 3 次諧波。短截線長度越長,諧振頻率越低。當比特率的一半或接近一半時存在 null,則眼睛將受到破壞。在我們的示例中,4.5GHz 大約是 10GB/s 的一半,從圖 3 中可以看出,結果眼圖是完全閉合的。

但 S 參數告訴我們更多。我們可以使用它們來確認之前使用的經驗法則,即信號的上升時間大于或等于通過過孔不連續性延遲的 3 倍。

如果您研究回波損耗圖,您會發現高達 1.83GHz 的匹配非常出色。這是 capacitor 模型適合的有效帶寬。換句話說,1.83GHz 的帶寬意味著您可以使用等效的電容器模型作為比特率高達 3.6GB/s 的過孔。

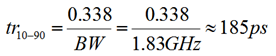

公式 1 通常用于將 3dB 帶寬轉換為等效的 10-90 上升時間。用 1.83 GHz 代替 3dB 帶寬,上升時間約為 185 ps。

方程 1

?

?

?

?

當您將 185 ps 除以 3 時,最終得到大約 62ps,而通過我們最初確定的過孔的傳播延遲約為 60ps。

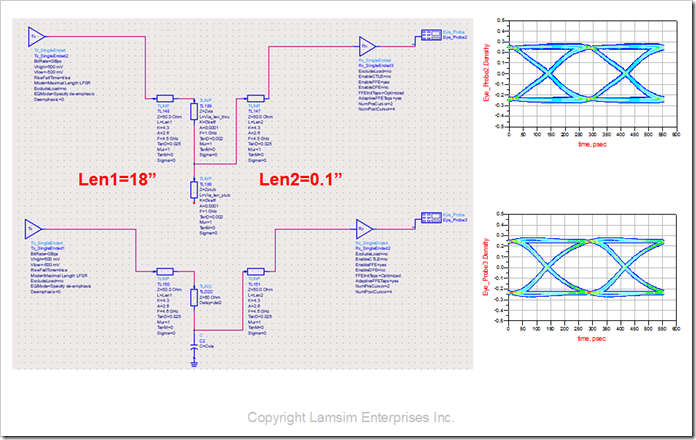

圖 5 是傳輸線長度減少到 18 英寸以將上升時間縮短到 185 ps 的仿真摘要。如您所見,3.6 Gb/s 的傳輸線過孔模型眼圖剛剛開始失真,而電容器模型仍然相對平滑;證實了我們的帶寬經驗法則。使用電容器作為超過此比特率的通孔模型將導致樂觀的結果,并在您的 10 Gig 原型進入實驗室時產生漫長的夜晚。

所以現在你明白我說的通孔是電容的,但不一定是電容器的意思了。

?

圖 5 3.6Gb/s 時的眼圖比較。頂部拓撲將 33 歐姆傳輸線用于過孔的直通和短截線部分。底部拓撲結構對過孔進行建模,其中一條 50 歐姆傳輸線表示直通部分的延遲,一個 1.9pf 電容器表示過剩的電容。使用?Agilent ADS?進行建模和仿真。

?

)

)

之 yolov5分類模型 訓練自己的數據集)

在Qt中的應用)