背景

《ug471》介紹了Xilinx 7 系列 SelectIO 的輸入/輸出特性及邏輯資源的相關內容。

第 1 章《SelectIO Resources》介紹了輸出驅動器和輸入接收器的電氣特性,并通過大量實例解析了各類標準接口的實現。

第 2 章《SelectIO Logic Resources》介紹了輸入輸出數據寄存器及其雙倍數據速率(DDR)操作,以及可編程輸入延(IDELAY)和可編程輸出延遲(ODELAY)。

第 3 章《Advanced SelectIO Logic Resources》介紹了ISERDESE2 、OSERDESE2與IO_FIFO。

了解了這個手冊充分介紹的SelectIO架構和資源,以及所支持的電平標準。就可以利用相應的架構和資源實現與不同電平標準、通信速率間的外設建立起聯系。

系列目錄與傳送門

- 基于Xilinx的7系列,

- 筆者學習、研究FPGA的過程、筆記,記錄為:《凡人修FPGA傳》。

說明1:本系列基于文檔文檔《ug471_7Series_SelectIO.pdf》而寫,翻譯和感悟,會出現中英文混合的情況。

說明2:雖然文中會出現一些原文的部分截圖,非常支持并推薦大家去看原汁原味的官方文檔

說明3:在查閱相關資料過程中,發現一些關于相關知識點的介紹零零散散,本系列會對其進行整合,力求詳盡。

說明4:本博客是筆者用來記錄學習過程的一個形式,并非專業論文。因此,在本博客中不會太注重圖文格式的規范。

說明5:如果文章有誤,歡迎諸位道友指出、討論,筆者也會積極改正,希望大家一起進步!

文章目錄

- 背景

- 系列目錄與傳送門

- 前言

- 1、Introduction

- 2、ILOGIC Resources

- 2.1、Combinatorial Input Path

- 2.2、Input DDR Overview (IDDR)

- 2.2.1、OPPOSITE_EDGE 模式

- 2.2.2、SAME_EDGE 模式

- 2.2.3、SAME_EDGE_PIPELINED 模式

- 2.3、Input DDR Resources (IDDR)

- 3、Input Delay Resources (IDELAY)

- 3.1、IDELAY Modes

- 3.2、IDELAY Timing

- 3.3、補充:波形圖

- 4、IDELAYCTRL

- 4.1、IDELAYCTRL Overview

- 4.2、IDELAYCTRL Timing

- 4.3、IDELAYCTRL Locations

- 5、OLOGIC Resources

- 5.1、Output DDR Overview (ODDR)

- 5.1.1、OPPOSITE_EDGE 模式

- 5.1.2、SAME_EDGE 模式

- 5.2、Clock Forwarding

- 5.3、Output DDR Primitive (ODDR)

- 6、Output Delay Resources (ODELAY)—Not Available in HR Banks

- 6.1、ODELAY Modes

- 6.2、ODELAY Timing

- 6.3、補充:波形圖

- 7、參考文獻

前言

本文對應的是《ug471_7Series_SelectIO.pdf》的第 2 章 < SelectIO Logic Resources > 部分,是對7系列FPGA的所帶有的I/O邏輯資源的一個概述與介紹。

1、Introduction

7系列FPGA的基本I/O邏輯資源,包括以下內容:

? Combinatorial input/output

? 3-state output control

? Registered input/output

? Registered 3-state output control

? Double-Data-Rate (DDR) input/output

? DDR output 3-state control

? IDELAY provides users control of an adjustable, fine-resolution delay taps

? ODELAY provides users control of an adjustable, fine-resolution delay taps

? SAME_EDGE output DDR mode

? SAME_EDGE and SAME_EDGE_PIPELINED input DDR mode

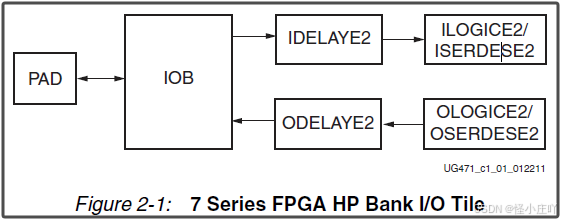

圖2-1,展示了1.8V HP Bank 的一個 I/O Tile。

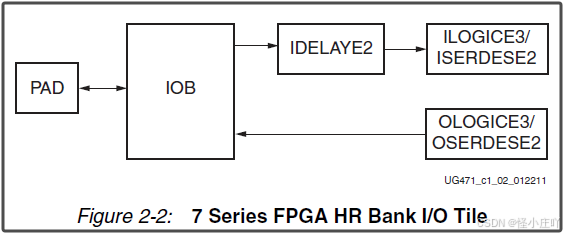

圖2-2,展示了3.3V HR Bank 的一個 I/O Tile。

SelectIO?輸入、輸出和三態驅動器,都位于輸入/輸出緩沖器(input/output buffer,IOB)中。

HP Bank 有獨立的IDELAY和ODELAY模塊。HR Bank 的邏輯元素與 HP Bank 相同,只是缺少ODELAY模塊。

2、ILOGIC Resources

ILOGIC 模塊與 輸入/輸出模塊(I/O blockIOB)相鄰,包含用于捕獲通過 IOB 進入 FPGA 的數據的同步元件(synchronous elements)。

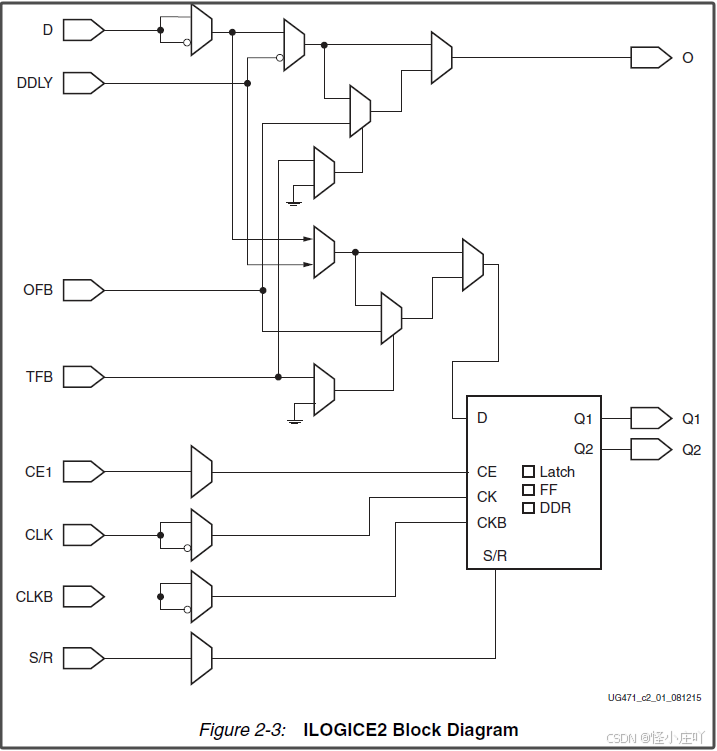

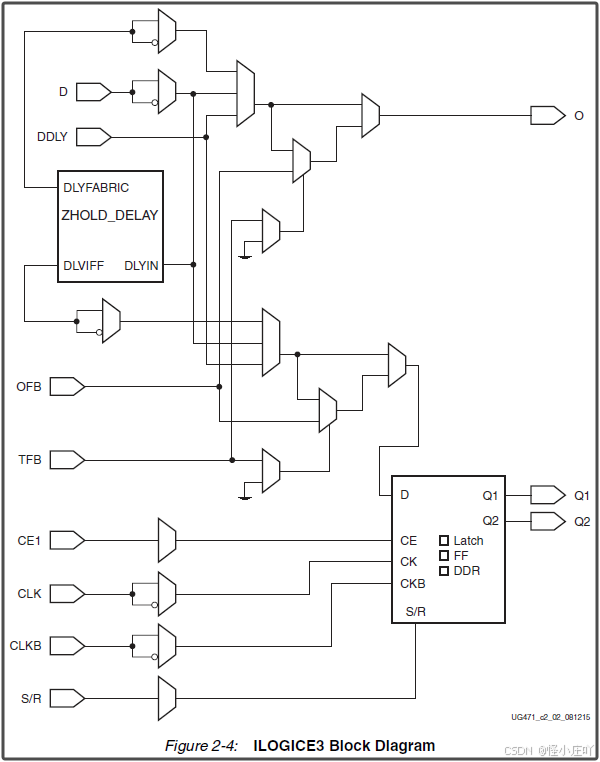

7 系列器件中的 ILOGIC 配置類型包括 ILOGICE2(HP I/O bank)和 ILOGICE3(HR I/O bank)。二者功能及端口完全一致,區別僅在于:

? ILOGICE3位于 HR bank,包含零保持延遲元件(zero hold delay element,ZHOLD)。

? ILOGICE2位于 HP bank,不含 ZHOLD 元件。

? 這些差異如圖 2-3 和圖 2-4 所示。

輸入/輸出互連(input/output interconnect,IOI)存儲元件 D輸入端 上的 ZHOLD 延遲,會自動匹配內部時鐘分配延遲,可消除焊盤之間的保持時間要求,使之為零。ILOGIC 模塊支持在輸入端配置可選的靜態未補償(an optional static uncompensated)零保持(zero hold,ZHOLD)延遲線(delay line),用于補償時鐘插入延遲(clock insertion delays)。當時鐘路徑直接來自同一 Bank 或相鄰 Bank 的 BUFG/BUFGCE 時,ZHOLD功能可經過優化用于補償時鐘插入延遲。除非時鐘源為 MMCM 或 PLL,亦或在 Xilinx設計約束(XDC)中設置了 IOBDELAY 屬性,ZHOLD 默認啟用。重要提示:ZHOLD 并非適用于所有應用場景,需查閱時序報告以確認其對特定時鐘方案的影響。

ILOGICE2 和 ILOGICE3 并非可實例化的原語。在布局布線后,如輸入觸發器(input flip-flop,IFD)或 IDDR(input DDR)等用戶實例化的元件,則會被包含在ILOGICE2 或 ILOGICE3中。

ILOGIC 可支持以下操作:

? 邊沿觸發的 D 型觸發器

? IDDR 模式(OPPOSITE_EDGE 或 SAME_EDGE 或 SAME_EDGE_PIPELINED)

? 電平敏感鎖存器

? 異步 / 組合邏輯

ILOGIC 模塊的寄存器具有一個公共的時鐘使能信號(CE1),默認情況下為高電平有效。如果未連接該信號,任何存儲元件的時鐘使能引腳將默認為有效狀態。ILOGIC 模塊的寄存器有一個通用的同步或異步 置位和復位信號(SR 信號)。置位/復位 輸入引腳 SR 會將存儲元件強制設置為 SRVAL 屬性所指定的狀態。復位條件優先于置位條件。在 ILOGIC 模塊中,可以為每個存儲元件單獨設置 SRVAL 屬性,但對于同步或異步置位 / 復位(SRTYPE)的選擇,卻不能為 ILOGIC 模塊中的每個存儲元件單獨進行設置。

博客在 《xilinx原語介紹及仿真之IDDR》中有進行ILOGICE的寄存器(IFD)使用的說明,并在有如下結論:

2.1、Combinatorial Input Path

組合輸入路徑,Combinatorial Input Path,組合輸入路徑用于在輸入驅動器和 FPGA 邏輯之間建立直接連接。

在以下情況下,軟件會自動使用該路徑:

? 從輸入數據到 FPGA 邏輯中的邏輯資源存在直接(未寄存)的連接。

? 將軟件映射指令 “ pack I/O register/latches into IOBs ” 設置為 “OFF” 狀態。

2.2、Input DDR Overview (IDDR)

7系列器件在 ILOGIC 模塊中配備了專用寄存器,用于實現輸入雙倍數據速率(DDR)寄存器功能。通過實例化 IDDR 原語來使用這一功能。

當不使用IDDR功能時,在使用IDDR原語后,只需要添加(IOB == “TRUE”)原語,就可以使用ILOGICE中的觸發器(FF)的功能。 這個觸發器相比FPGA內部觸發器更靠近FPGA管腳,使得建立時間余量更大,更有利于時序。(《xilinx原語介紹及仿真之IDDR》)

所有輸入到 I/O tile 的時鐘均采用全多路復用方式(fully multiplexed),即 ILOGIC 模塊和 OLOGIC 模塊之間不共享時鐘。IDDR 原語支持以下工作模式:

? OPPOSITE_EDGE 模式

? SAME_EDGE 模式

? SAME_EDGE_PIPELINED 模式

SAME_EDGE模式 和 SAME_EDGE_PIPELINED模式 允許設計人員在 ILOGIC 模塊內將下降沿數據轉移到上升沿域,從而節省可配置邏輯塊(CLB)和時鐘資源,并提高性能。上述這些模式,通過 DDR_CLK_EDGE 屬性來實現。

2.2.1、OPPOSITE_EDGE 模式

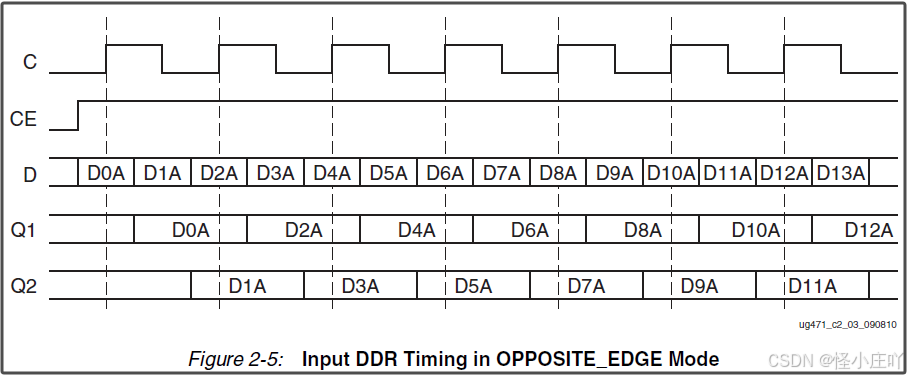

傳統DDR 的 OPPOSITE_EDGE模式,是通過 ILOGIC 模塊中的單個輸入來實現的。上升沿、下降沿均采樣:在時鐘的上升沿,數據通過輸出 Q1 傳輸至 FPGA 邏輯;在時鐘的下降沿,數據則通過輸出 Q2 傳輸至 FPGA 邏輯。且,輸出相較于輸入要延一拍。

圖 2-5 展示了 IDDR 在 OPPOSITE_EDG模式 下的時序圖。

2.2.2、SAME_EDGE 模式

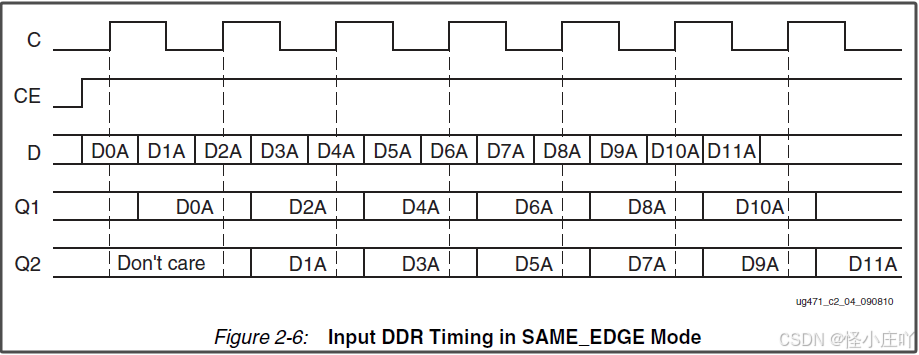

在 SAME_EDGE 沿模式下,數據會在同一個時鐘邊沿被送入FPGA邏輯。

輸出結果,與OPPOSITE_EDGE 模式相比,差別在于數據對齊了,但錯開了一位。

圖2-6,展示 SAME_EDGE模式 下的IDDR時序圖。在時序圖中,輸出對Q1和Q2不再是(0)和(1)。而是,第一對出現的是Q1(0)和Q2(don’t care),接著在下一個時鐘周期出現的是(1)和(2)。

2.2.3、SAME_EDGE_PIPELINED 模式

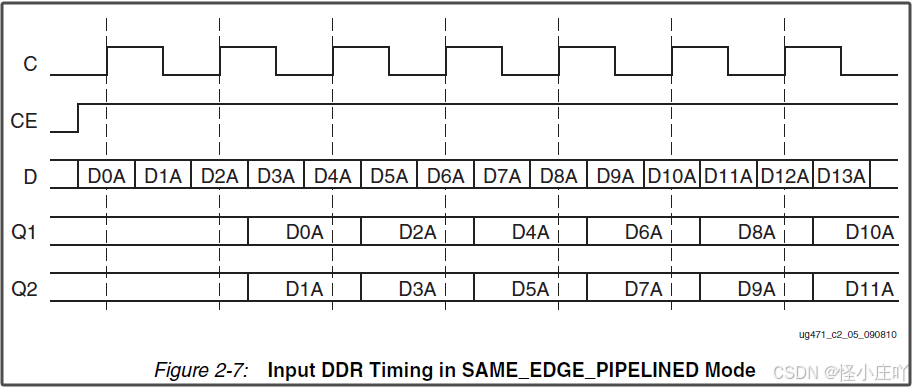

在 SAME_EDGE_PIPELINED 模式下,數據在同一個時鐘邊沿被傳輸到 FPGA 邏輯中。

與 SAME_EDGE 模式不同的是,數據對不再被一個時鐘周期分隔開。然而,為了消除 SAME_EDGE 模式中的時鐘周期分隔效應?(separated effect),需要額外的時鐘延遲。

圖 2-7, 展示了 IDDR 在 SAME_EDGE_PIPELINED 模式下的時序圖。輸出對 Q1 和 Q2 會同時被傳輸到 FPGA 邏輯中。

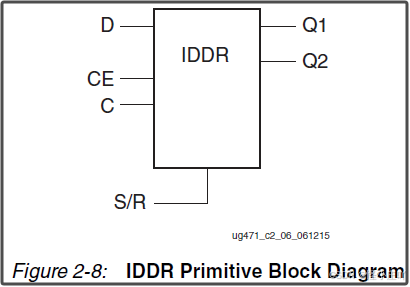

2.3、Input DDR Resources (IDDR)

- IDDR primitive

圖2-8,展示了 IDDR 原語。其中,Set 和 Reset 不能同時斷言。

3、Input Delay Resources (IDELAY)

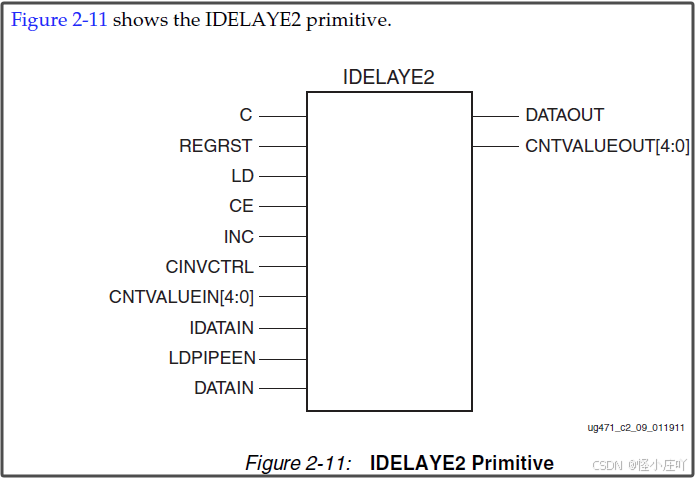

Every I/O block contains a programmable delay primitive called IDELAYE2. The IDELAY can be connected to an ILOGICE2/ISERDESE2 or ILOGICE3/ISERDESE2 block.

IDELAYE2 is a 31-tap, wraparound, delay primitive with a calibrated tap resolution. Refer to the 7 series FPGA data sheets for delay values. It can be applied to the combinatorial input path, registered input path, or both. It can also be accessed directly from the FPGA logic. IDELAY allows incoming signals to be delayed on an individual input pin basis. The tap delay resolution is contiguously calibrated by the use of an IDELAYCTRL reference clock from the range specified in the 7 series FPGA data sheets.

- IDELAYE2 primitive

3.1、IDELAY Modes

當用作輸入延遲(IDELAY)時,數據輸入可來自輸入緩沖器(IBUF)或 FPGA 邏輯,輸出則連接至 ILOGICE2/ISERDESE2 或 ILOGICE3/ISERDESE2 模塊。它有以下幾種工作模式可供選擇:

- Fixed delay mode( IDELAY_TYPE=FIXED )

在 fixed delay mode 下,延遲值在配置時根據 IDELAY_VALUE 屬性確定的抽頭編號(tap number)進行預設。一旦完成配置,該值便無法更改。使用此模式時,必須實例化 IDELAYCTRL 原語。

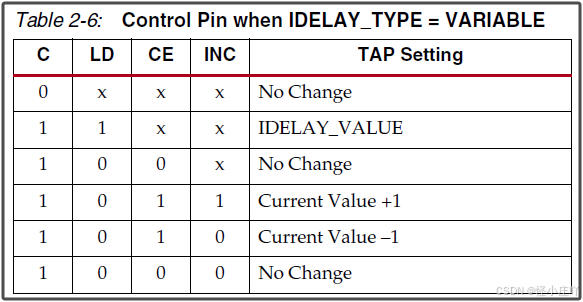

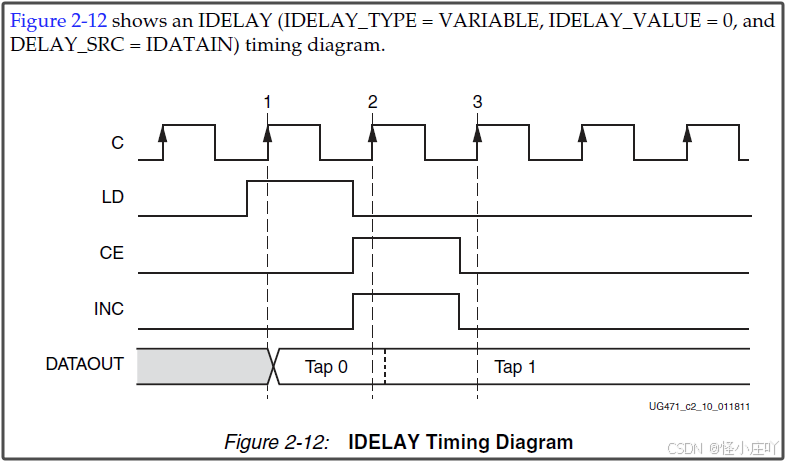

- Variable delay mode( IDELAY_TYPE=VARIABLE )

在 variable delay mode下,延遲值可以在配置完成后可通過操控控制信號 CE 和 INC 來改變。使用此模式時,同樣必須實例化 IDELAYCTRL 原語。

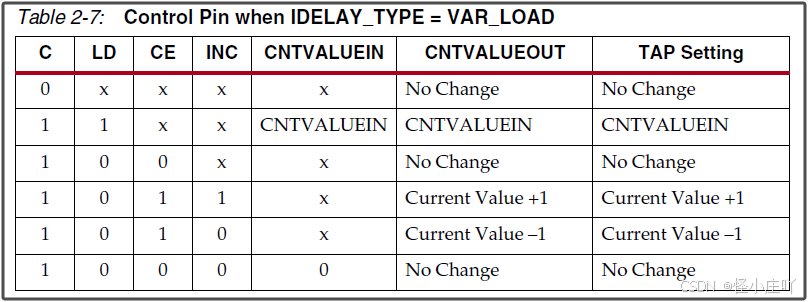

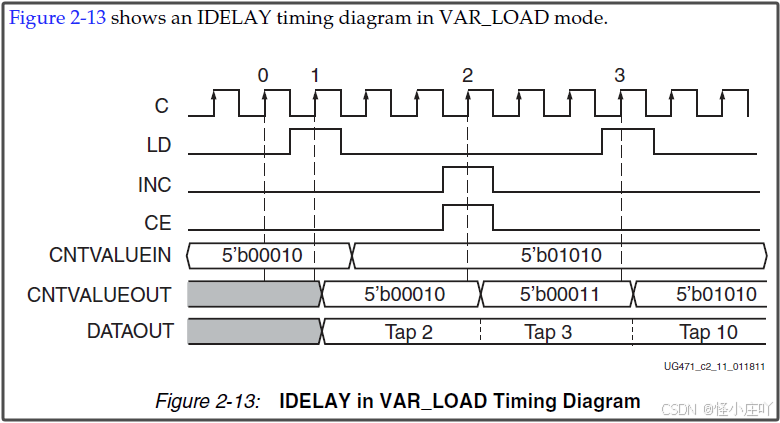

- Loadable variable mode( IDELAY_TYPE=VAR_LOAD )

在此模式下,除了具備與 Variable delay mode( IDELAY_TYPE=VARIABLE ) 相同的功能外,還可通過來自 FPGA 邏輯的 5 位輸入 CNTVALUEIN[4:0] 加載 IDELAY 的 tap 。當 LD 引腳出現脈沖時,CNTVALUEIN[4:0] 上的值將成為新的 tap value 。使用此模式時,必須實例化 IDELAYCTRL 原語。

VAR_LOAD模式與VARIABLE模式相似,區別在于 VARIABLE模式為高電平時,是加載IDELAY_VALUE的值到內部作為延時數據,而VAR_LOAD模式在LD為高電平時,加載輸入信號CNTVALUEIN的值作為內部新的延時數據。(《xilinx原語介紹及仿真之IDELAYE2 & IDELAYCTRL》)

3.2、IDELAY Timing

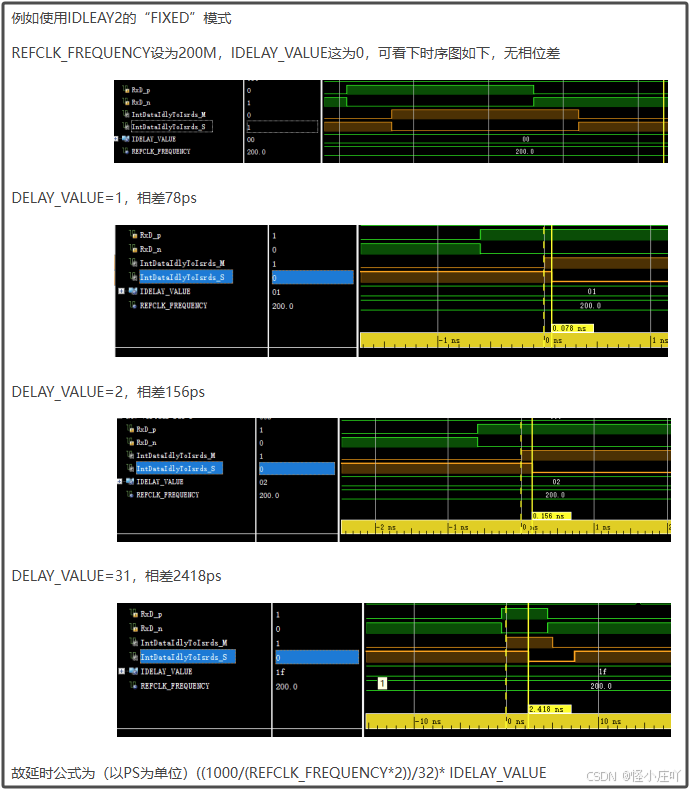

3.3、補充:波形圖

在《7系列selectio之DELAYE相關》中,看到這樣一個波形,就直接截圖給諸位道友展示了。請原諒筆者有些懶,沒有自己跑仿真。

4、IDELAYCTRL

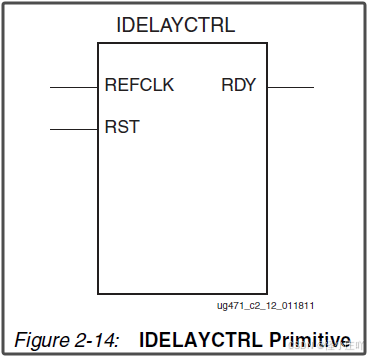

4.1、IDELAYCTRL Overview

如果實例化了 IDELAYE2 或 ODELAYE2 原語,那么也必須實例化 IDELAYCTRL 模塊。 IDELAYCTRL 模塊會持續校準其所在區域內的各個 delay taps(IDELAY/ODELAY),以降低工藝、電壓和溫度變化帶來的影響。IDELAYCTRL 模塊會使用用戶提供的參考時鐘(REFCLK)來校準 IDELAY 和 ODELAY。

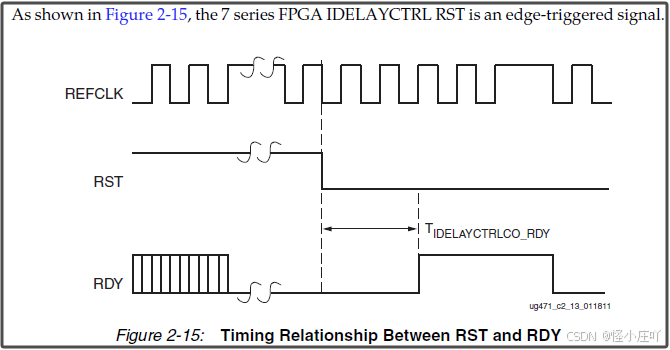

- RST - Reset

RST 為高電平有效異步復位信號。復位釋放后延時一段時間將RDY信號拉高表示復位完成。

To ensure proper IDELAY and ODELAY operation, IDELAYCTRL must be reset after configuration and the REFCLK signal is stable. A reset pulse width TIDELAYCTRL_RPW is required.

- REFCLK - Reference Clock

REFCLK 為 IDELAYCTRL 提供時間基準,用于校準同一區域內所有 IDELAY 和 ODELAY 模塊。

該時鐘必須由 BUFG 或 BUFH 驅動,且設定值也不是可以隨意給的,要求是 190-210、 290-310、390-410 這三個范圍之間。

REFCLK must be FIDELAYCTRL_REF ± the specified ppm tolerance (IDELAYCTRL_REF_PRECISION) to guarantee a specified IDELAY and ODELAY resolution ( TIDELAYRESOLUTION ). REFCLK can be supplied directly from a user-supplied source or the MMCM and must be routed on a global clock buffer.

- RDY - Ready

RDY 表示 IDELAY 和 ODELAY 模塊已完成校準。若 REFCLK 保持高電平或低電平超過一個時鐘周期,RDY 信號將置為無效(低電平)。若 RDY 無效(低電平),則必須重新復位 IDELAYCTRL 模塊。

The implementation tools allow RDY to be unconnected/ignored.

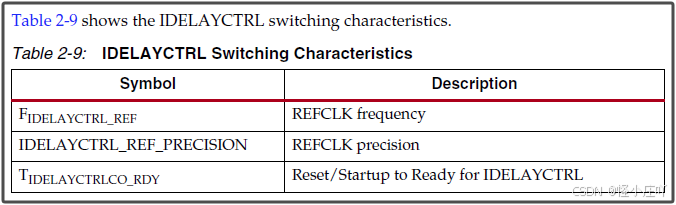

4.2、IDELAYCTRL Timing

4.3、IDELAYCTRL Locations

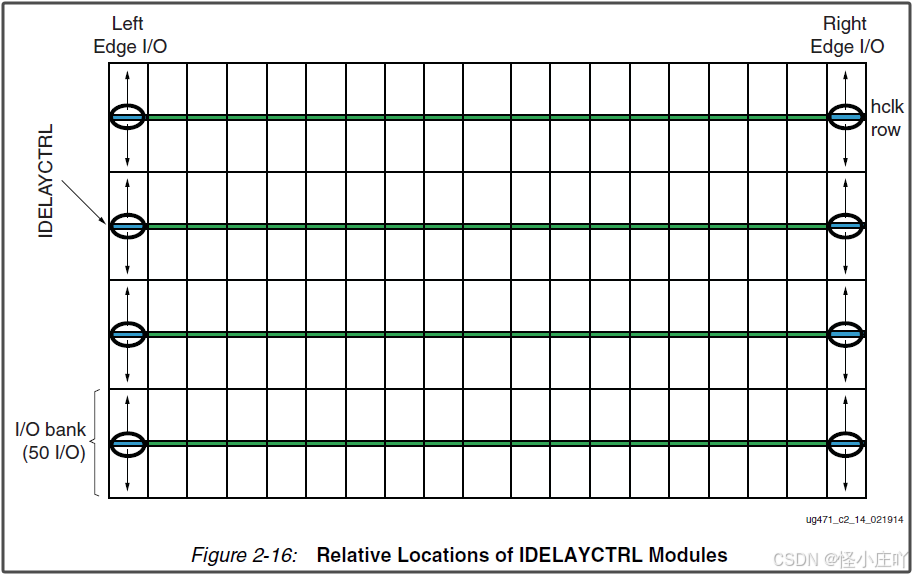

在每個時鐘區域的每一 I/O 列中都存在 IDELAYCTRL 模塊。一個 IDELAYCTRL 模塊會對其所在時鐘區域內的所有 IDELAYE2 和 ODELAYE2 模塊進行校準。

?圖2-16,展示了IDELAYCTRL模塊在FPGA架構中的相對位置。

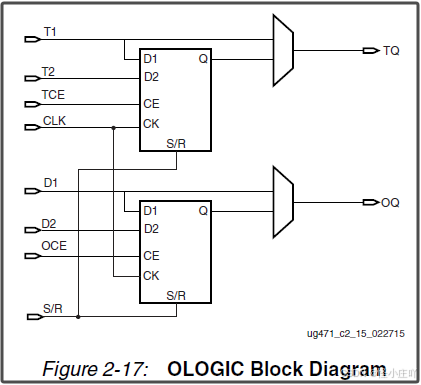

5、OLOGIC Resources

OLOGIC 模塊靠近 I/O block( IOB )。OLOGIC 是一個專用的同步模塊,用于通過 IOB 將數據從 FPGA 中輸出。

OLOGIC 資源的類型包括 OLOGICE2(HP I/O banks)和 OLOGICE3(HR I/O banks)。

OLOGICE2 和 OLOGICE3 并非原語,不能被實例化。在布局布線之后,它們包含用戶實例化的元件,比如 output flip-flop(OFD)或 output DDR element(ODDR)。

OLOGIC 由兩個主要模塊組成,一個用于配置輸出數據路徑,另一個用于配置三態控制路徑。這兩個模塊有一個公共時鐘(CLK),但使能信號不同,分別是 OCE 和 TCE。兩者都具有由獨立的 SRVAL 屬性控制的異步和同步置位與復位(S/R 信號)功能。

輸出路徑和三態路徑可以被獨立配置為以下模式之一:

? 邊沿觸發的 D 型觸發器

? DDR模式(SAME_EDGE 或 OPPOSITE_EDGE)

? 電平敏感鎖存器

? 異步 / 組合邏輯

圖 2-17,展示了 OLOGIC 模塊中的各種邏輯資源。

- Combinatorial Output Data and 3-State Control Path

組合輸出路徑在 FPGA 邏輯與輸出驅動器或輸出驅動器控制之間建立直接連接。在以下情況下,軟件會自動使用這些路徑:

? 從 FPGA 邏輯中的邏輯資源到輸出數據或三態控制存在直接(未寄存)的連接。

? “ pack I/O register/latches into IOBs ” 這一軟件映射指令設置為 “關閉(OFF)” 狀

5.1、Output DDR Overview (ODDR)

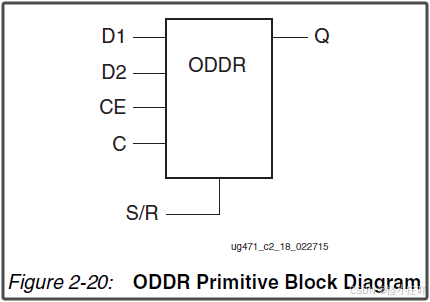

ODDR位于OLOGIC中,把FPGA內部邏輯中的單沿傳輸信號轉換為雙沿傳輸信號,輸出給ODELAYE或者PAD。(《xilinx原語詳解及仿真之ODDR》)

7 系列器件在 OLOGIC(輸出邏輯)模塊中設有專用寄存器,用于實現 ODDR 寄存器功能。通過實例化 ODDR 原語即可使用該功能。使用 OLOGIC 時,DDR 多路復用會自動進行,無需手動控制多路選擇,該控制信號由時鐘生成。

ODDR 原語只有一個時鐘輸入,下降沿數據由輸入時鐘的本地反相時鐘驅動。所有輸入到 I/O tile 的時鐘均采用全多路復用方式(fully multiplexed),即 ILOGIC 模塊和 OLOGIC 模塊之間不存在時鐘共享。ODDR 原語支持以下工作模式:

? OPPOSITE_EDGE 模式

? SAME_EDGE 模式

SAME_EDGE模式 允許設計人員在 ODDR時鐘 的上升沿將兩個數據輸入都提供給 ODDR 原語,從而節省了可配置邏輯塊(CLB)和時鐘資源,并提升了性能。此模式通過 DDR_CLK_EDGE 屬性實現,同時也支持三態控制。

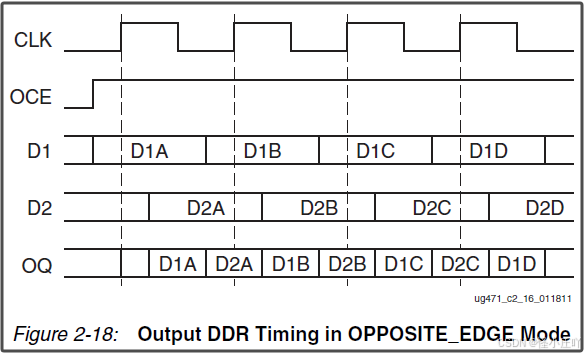

5.1.1、OPPOSITE_EDGE 模式

在 OPPOSITE_EDGE模式下,時鐘(CLK)的上升沿和下降沿都被用于以兩倍的數據傳輸速率捕獲來自 FPGA 邏輯的數據。輸出端的數據都會被傳輸到 IOB 的數據輸入端或三態控制輸入端。

如圖 2-18 ,展示了在OPPOSITE_EDGE模式下的 output DDR 時序圖。

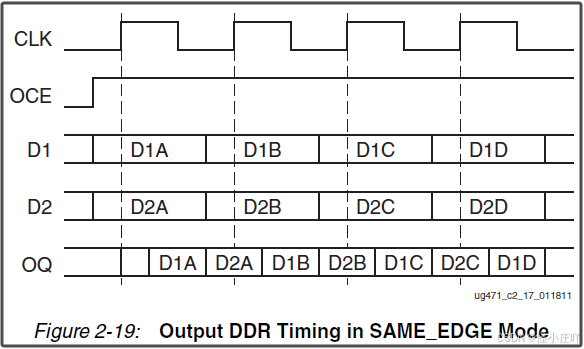

5.1.2、SAME_EDGE 模式

在 SAME_EDGE模式 下,數據可以在同一個時鐘邊沿被傳輸至 IOB 。在同一個時鐘邊沿將數據傳輸至 IOB,可避免出現建立時間違規的情況,并且與使用 CLB 寄存器相比,用戶能夠以最小的寄存器到寄存器延遲實現更高的 DDR 頻率。

圖 2-19 ,展示了SAME_EDGE 模式下的輸出 DDR 時序圖。

5.2、Clock Forwarding

Output DDR 可以將時鐘的一個副本轉發到輸出端。這對于以相同延遲傳播時鐘信號和 DDR 數據,以及在每個時鐘負載都有獨立時鐘驅動器的多時鐘生成場景中非常有用。實現方法是將 ODDR 原語的 D1 輸入端置為高電平,D2 輸入端置為低電平。Xilinx 建議采用這種方案將時鐘從 FPGA 邏輯轉發至輸出引腳。

5.3、Output DDR Primitive (ODDR)

6、Output Delay Resources (ODELAY)—Not Available in HR Banks

每個 HP I/O block 包含一個名為 ODELAYE2 的可編程絕對延遲原語。該 ODELAY 可連接至 OLOGICE2/OSERDESE2 模塊。

ODELAY is a 31-tap,wraparound, delay primitive with a calibrated tap resolution.

它可應用于組合輸出路徑或寄存輸出路徑,也可直接從 FPGA 邏輯進行訪問。ODELAY 允許對輸出信號按單個信號進行延遲處理。通過從 7 系列 FPGA 數據手冊規定的范圍內選擇 IDELAYCTRL 參考時鐘,可調整 tap delay resolution 。

6.1、ODELAY Modes

當用作 ODELAY 時,數據輸入來自 IBUF 或 FPGA 邏輯,輸出則連接 ILOGICE2/ISERDESE2 或 ILOGICE3/ISERDESE2。ODELAY 提供以下幾種操作模式:

- Fixed delay mode( ODELAY_TYPE = FIXED )

在 fixed delay mode 下,延遲值在配置時根據 ODELAY_VALUE 屬性確定的 tap number進行預設。一旦完成配置,該值便無法更改。使用此模式時,必須實例化 IDELAYCTRL 原語。

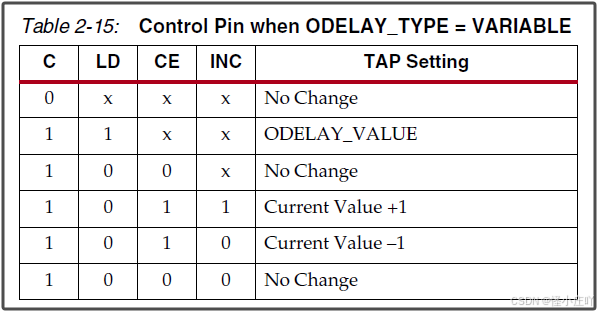

- Variable delay mode( ODELAY_TYPE = VARIABLE )

在 variable delay mode 下,配置完成后,可通過操控控制信號 CE 和 INC 來改變延遲值。使用此模式時,必須實例化 IDELAYCTRL 原語。

- Loadable variable delay mode (ODELAY_TYPE = VAR_LOAD)

在此模式下,除具備與 ODELAY_TYPE = VARIABLE 相同的功能外,還可通過來自 FPGA 邏輯的 5 位輸入 CNTVALUEIN[4:0] 加載 ODELAY 的 tap。當 LD 引腳出現脈沖時,CNTVALUEIN<4:0 > 上的值將成為新的 tap value。由于具備這一功能,ODELAY_VALUE 屬性將被忽略。使用此模式時,必須實例化 IDELAYCTRL 原語。

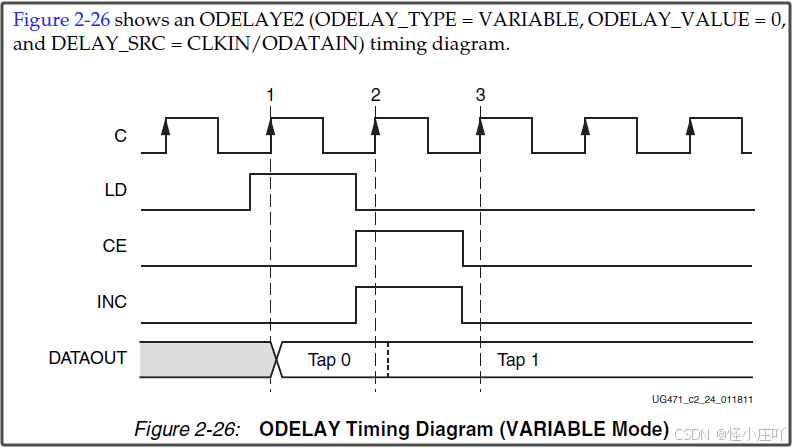

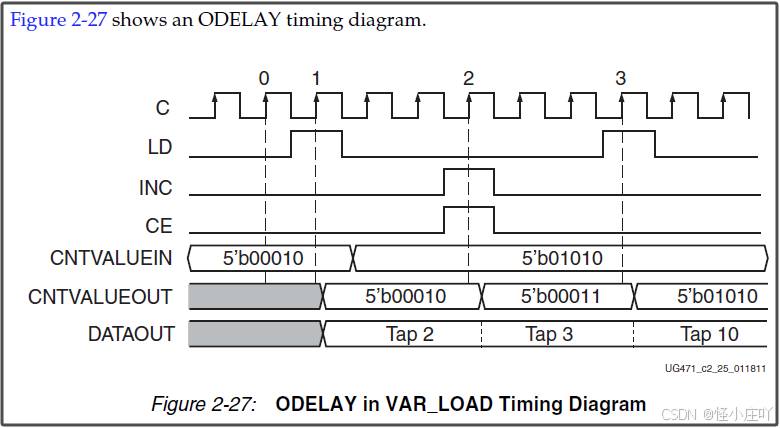

6.2、ODELAY Timing

6.3、補充:波形圖

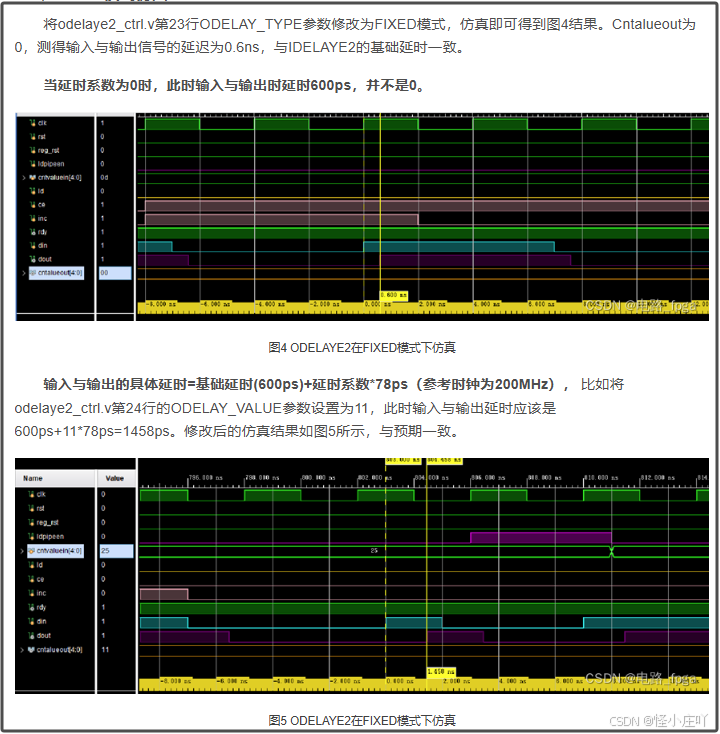

但是在《xilinx原語介紹及仿真之ODELAYE2》中,看到了仿真波形,如下圖所示。請原諒筆者有些懶,沒有自己跑仿真。

7、參考文獻

1、《ug471_7Series_SelectIO.pdf》

2、《GMII轉RGMII(二)ILOGIC相關原語介紹》

3、《xilinx原語介紹及仿真之IDDR》,這篇也還不錯。

4、《xilinx原語介紹及仿真之IDELAYE2 & IDELAYCTRL》

5、《7系列selectio之DELAYE相關》

6、《xilinx原語介紹及仿真之ODELAYE2》,這篇博客里面的仿真做的比較全,諸位道友感興趣的話,可以去看一看。

7、《xilinx原語詳解及仿真之ODDR》

)

-神經網絡參數初始化-之-softmax)

)

(一))