版本:Vivado2020.2(Vitis)

任務:PL 端自定義一個 AXI4 接口的 IP 核,通過 AXI_HP 接口對 PS 端 DDR3 進行讀寫 測試,讀寫的內存大小是 4K 字節,

目錄

一、介紹? ??

(1)AXI

(2)AXI SmartConnect 與?AXI Interconnect IP核

(3)ZYNQ AXI GP/HP 接口

二、硬件設計

三、軟件設計

四、效果

一、介紹? ??

(1)AXI

????????AXI:高級可擴展接口(Advanced eXtensible Interface)是 ARM 公司提出的?高性能、高帶寬、低延遲?的片上總線協議,屬于 AMBA:高級微控制器總線架構(Advanced Microcontroller Bus Architecture)協議家族的一部分,廣泛應用于 FPGA 和 SoC 設計中。

AXI 協議目前主要有?3 種版本:

-

AXI4(AXI4-Full):支持高帶寬數據傳輸,適用于內存映射(Memory-Mapped)設備。

-

AXI4-Lite:簡化版,適用于低復雜度外設(如寄存器配置)。

-

AXI4-Stream:無地址協議,用于高速流數據傳輸(如視頻、網絡數據)。

| AXI4 (Full) | AXI4-Lite | AXI4-Stream | |

|---|---|---|---|

| 地址支持 | ??? | ??? | ? (無地址) |

| 突發傳輸 | ??? | ? | ? (但本身流數據連續,且不限制長度) |

| 亂序支持 | ?? | ? | ? |

| 適用場景 | DDR訪問、DMA | 寄存器配置 | 流數據傳輸:視頻流、網絡數據 |

(2)AXI SmartConnect 與?AXI Interconnect IP核

????????兩者都是 Xilinx 提供的基礎互聯 IP,用于管理多個AXI主設備(Master)和從設備(Slave)之間的通信,支持地址路由、仲裁和基礎QoS(服務質量)。AXI SmartConnect 為更高性能互聯IP,在AXI Interconnect 基礎上優化了?延遲、吞吐量和資源利用率,支持更復雜的系統拓撲。

| AXI Interconnect | AXI SmartConnect | |

|---|---|---|

| 協議支持 | AXI4, AXI4-Lite | AXI4, AXI4-Lite, AXI4-Stream |

| QoS 能力 | 基礎輪詢仲裁 | 權重仲裁、優先級搶占 |

| 數據寬度轉換 | 需手動配置 | 自動適配 |

| 延遲優化 | 中等 | 更低延遲 |

| 適用場景 | 簡單到中等復雜度系統 | 高性能復雜系統(如Versal) |

| 資源占用 | 較少 | 較多(但更高效) |

(3)ZYNQ AXI GP/HP 接口

????????Zynq 的 PS 與 PL 端之間通過多種AXI接口連接,其中?GP(通用)接口和 HP(高性能)接口是最常用的兩類,主要區別在于帶寬、用途和連接對象。以下是核心對比與使用指南:

| 特性 | GP(General Purpose)接口 | HP(High Performance)接口 |

|---|---|---|

| AXI版本 | AXI4(32位數據位寬) | AXI3/AXI4(32/64位數據位寬) |

| 數據帶寬 | 較低 | 高 |

| 主要用途 | 控制寄存器訪問、低速數據傳輸 | 高速數據流(如DMA、視頻處理) |

| 連接對象 | PS 作為主設備訪問 PL 外設、 進行一般性的數據傳輸交互 | PL 作為主設備訪問 PS 端 DDR 或 OCM |

| 典型應用 | 配置IP核寄存器、傳感器數據讀取 | 視頻幀緩沖、高速ADC/DAC數據交互 |

二、硬件設計

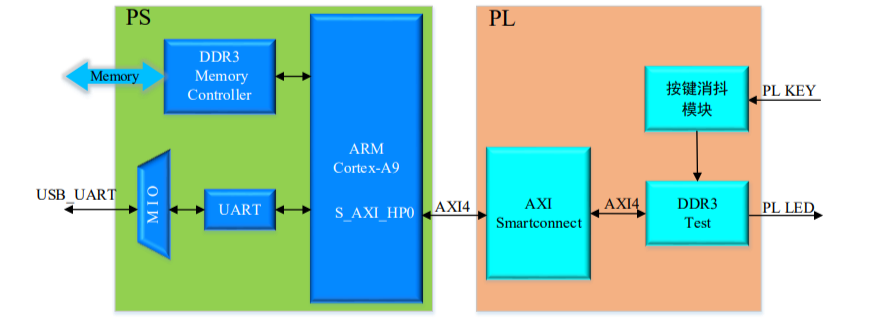

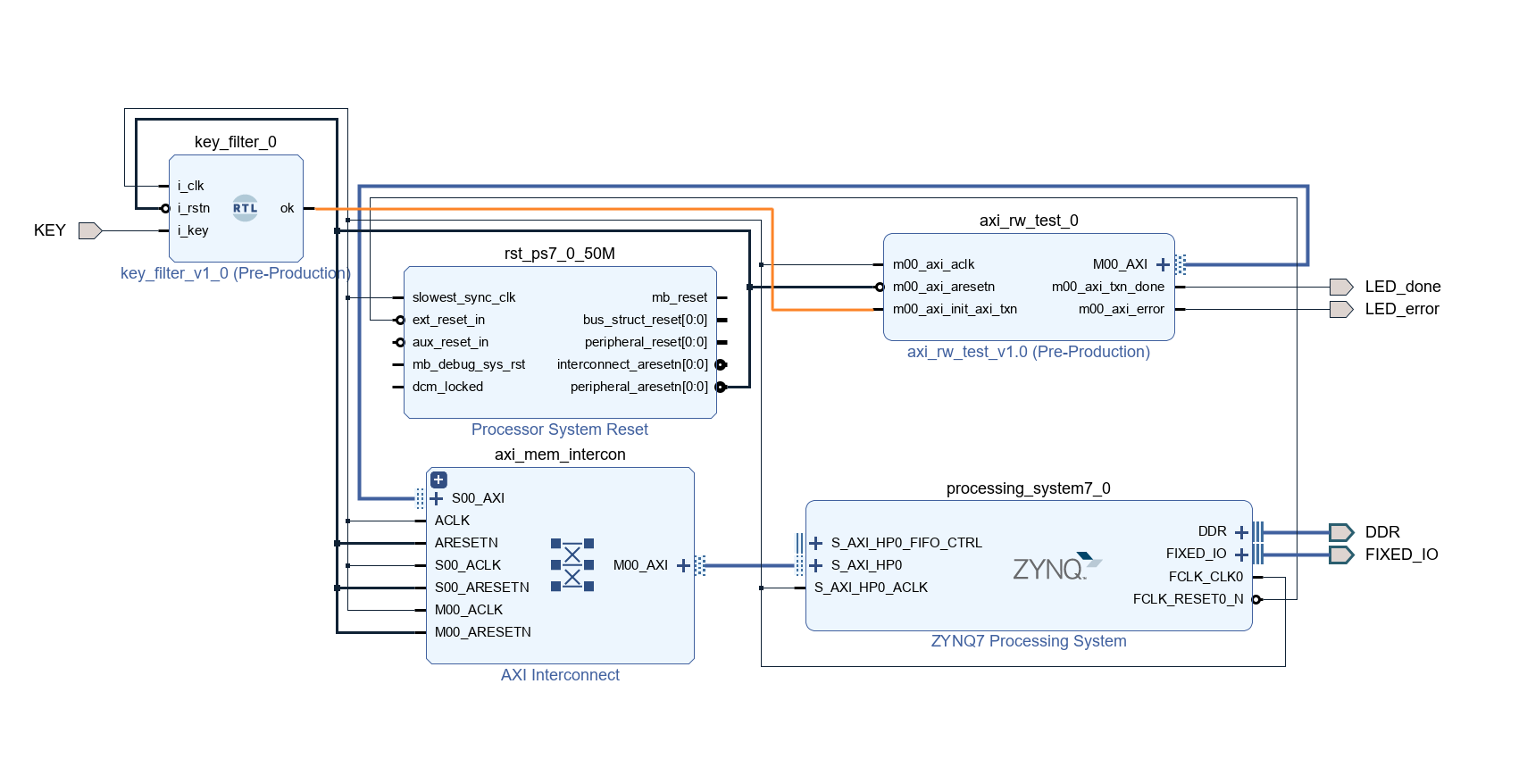

? ? ? ? 整體系統框圖如圖所示,ZYNQ 配置用到了UART、AXI HP接口(PL端訪問 PS端 DDR)、DDR、以及提供給PL端的時鐘、復位信號:

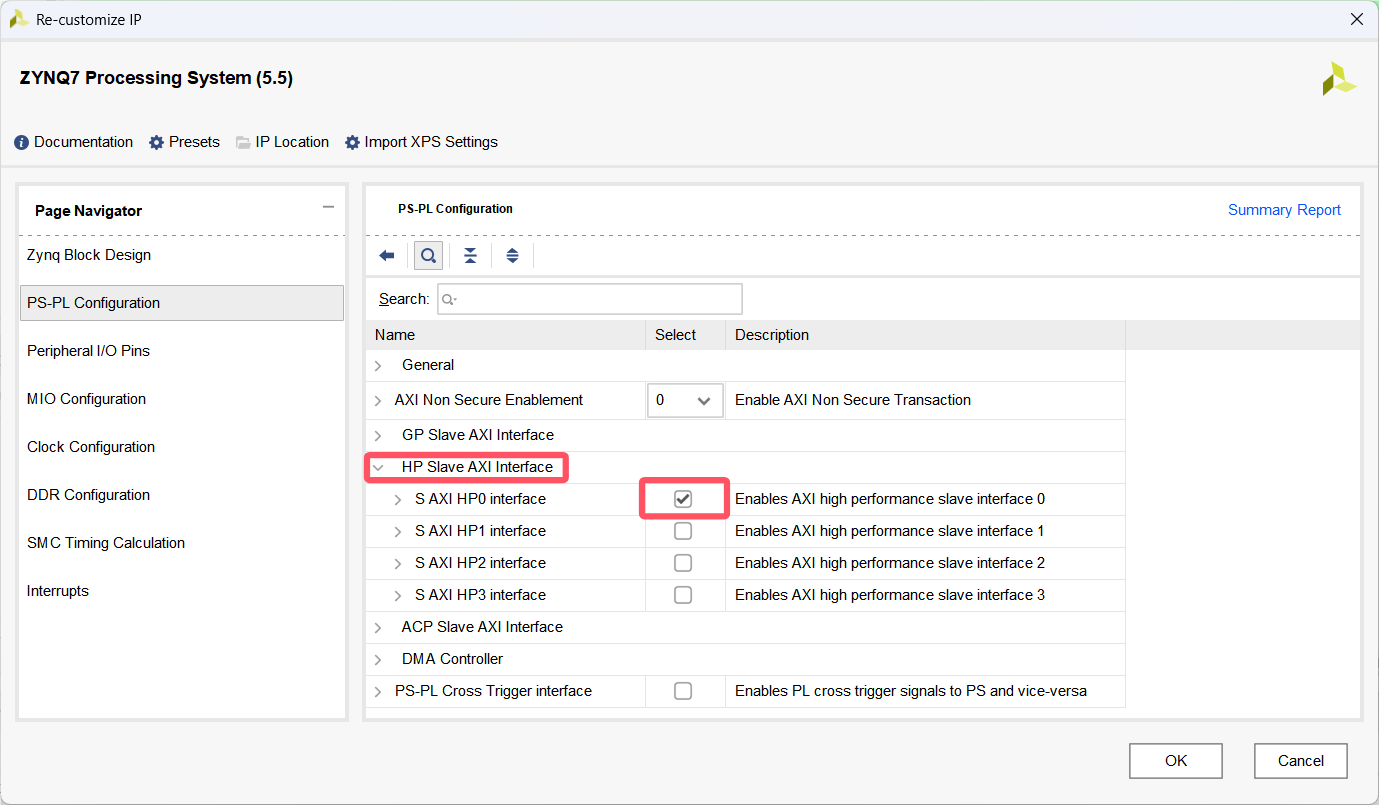

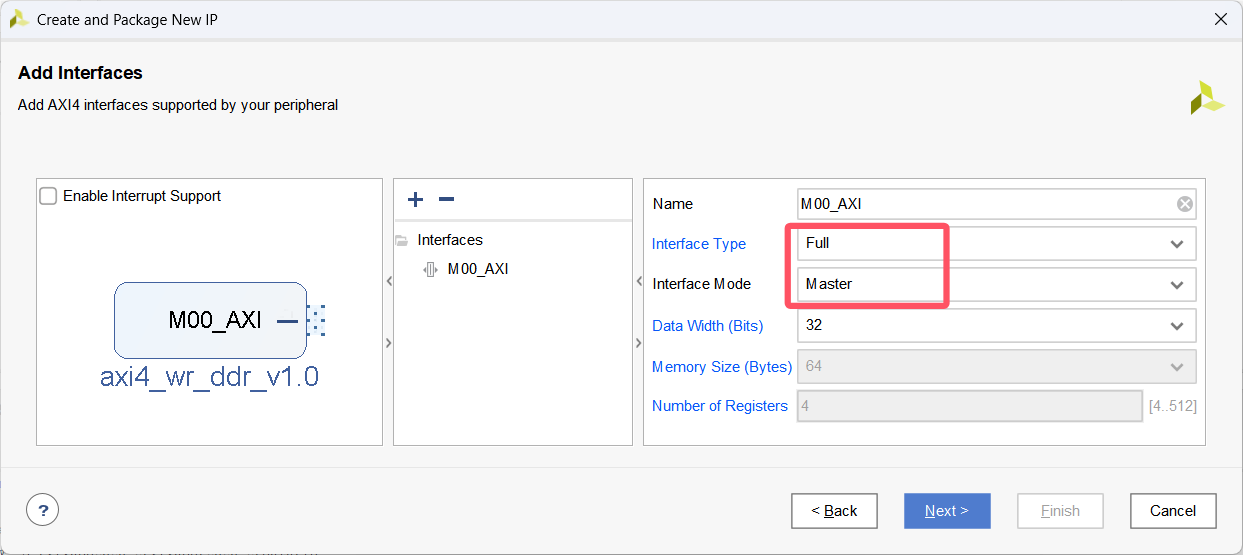

????????(1)自定義 IP 核創建流程之前有介紹,參考:ZYNQ筆記(六):自定義IP核-LED呼吸燈。此外本次 IP 要實現 PL 端讀寫 PS 端 DDR,因此接口類型需要選FULL(AXI4-FULL)接口模式為Master。如圖所示:

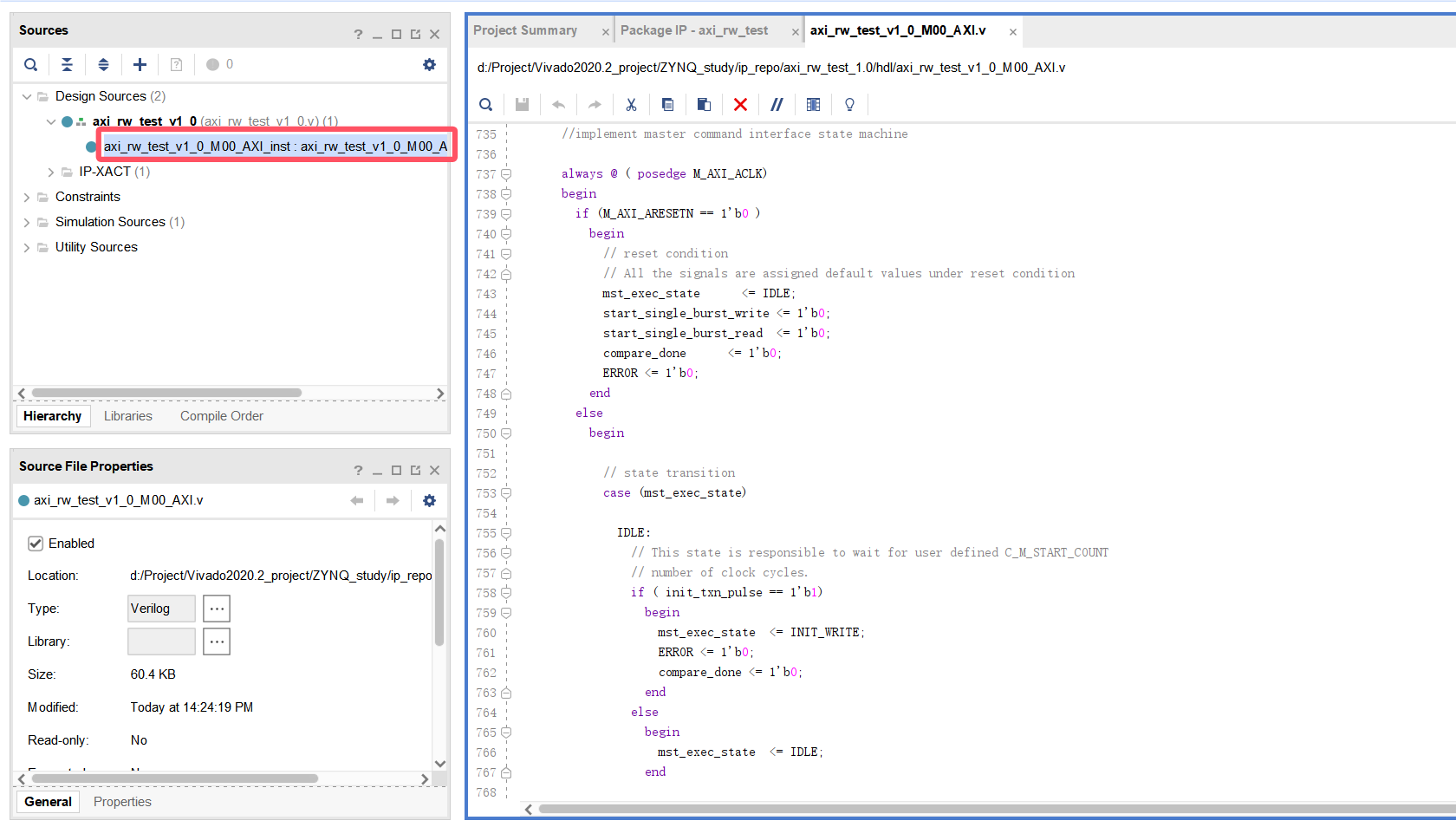

????????(2)所創建的自定義 IP 核 Vivado 提供了實現 AXI-Full 接口的讀寫功能的模板(頂層模塊下的.v文件):不用對代碼作任 何修改,即可實現本次例程對 DDR 的讀寫測試功能

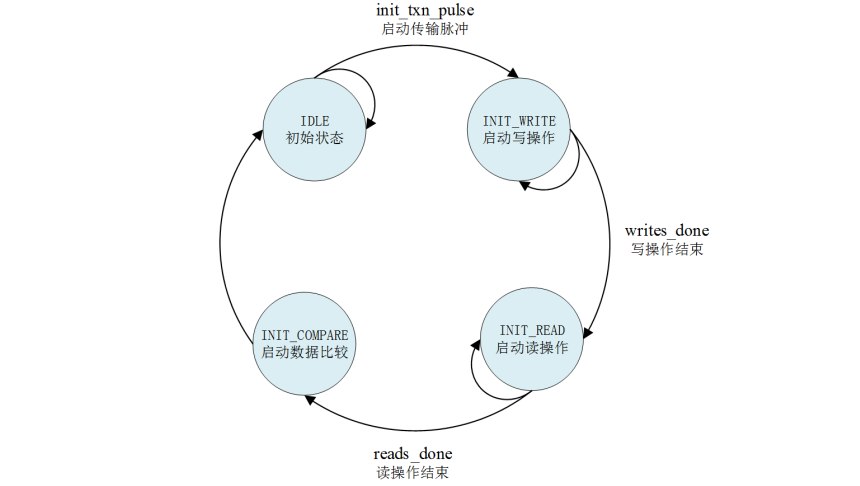

模板代碼設計了一個狀態機實現讀寫功能(模板代碼分析可參考正點原子視頻教程):

| 狀態機流程 |

|---|

| 1. 系統復位后,狀態機處于IDLE 初始狀態,等待外部輸入的啟動傳輸脈沖 init_txn_pulse。 |

| 2. IDLE 狀態下檢測到 init_txn_pulse 為高電平,狀態機跳轉到 INIT_WRITE 狀態。 |

| 3. INIT_WRITE 狀態下,狀態機拉高 start_single_burst_write 信號,來不斷地啟動 AXI4 Master 接口對 Slave 端大小為 4KB 的存儲空間進行突發寫操作。寫操作完成后,write_done 信號會拉高,狀態機進入 INIT_READ 狀態。 |

| 4. INIT_READ 狀態下,狀態機拉高 start_single_burst_read 信號,不斷地啟動 AXI4 Master 接口對 Slave 端同一存儲空間進行突發讀操作,同時將讀出的數據與寫入的數據進行對比。讀操作完成后,read_done 信號拉高,狀態機進入 INIT_COMPARE 狀態。 |

| 5. INIT_COMPARE 狀態下,判斷 AXI4 接口在讀寫過程中的是否發生錯誤,并將錯誤狀態賦值給 ERROR 信號,然后將 compare_done 信號拉高,表示一次讀寫測試完成。最后跳轉到 IDLE 狀態,等待下一次讀寫操作的啟動信號。 |

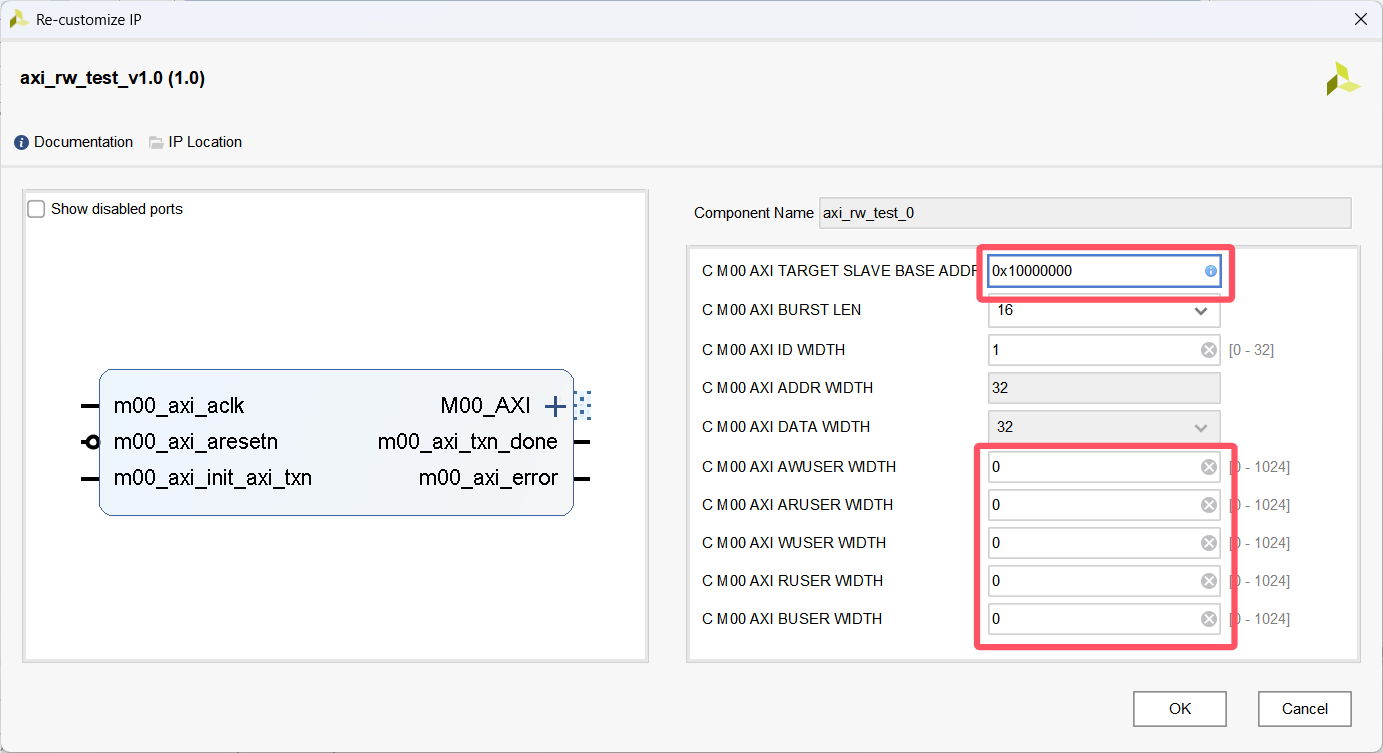

????????(3)直接封裝打包IP核,不用對內部代碼進行修改,直接使用生成的模板實現讀寫操作。再將自定義IP核添加到BD設計中,雙擊進行配置,將變量C M AXI TARGET SLAVE BASE ADDR 的值修改為0x1000_0000,它位于DDR3存儲器的地址空間,是axi4_rw_test IP核進行讀寫操作的起始地址,約為中間位置(不同板卡的ddr大小可能不一樣)。將該地址之前約DDR一半的存儲空間預留下來,用于運行PS中的軟件程序:

? ? ? ? 寫滿這些配置參數用于?AXI4 總線?的?用戶側擴展信號,允許在 AXI4 事務中添加額外的用戶自定義信息,沒有使用全部設置0。

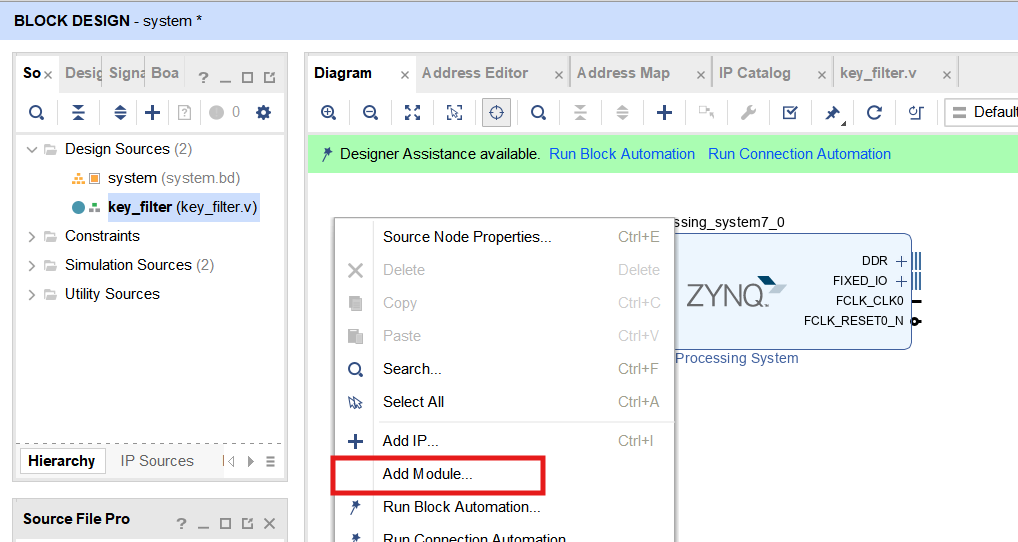

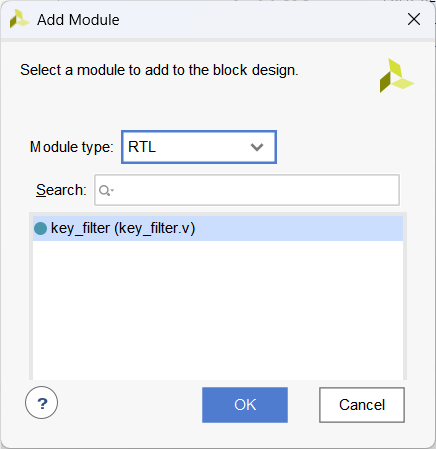

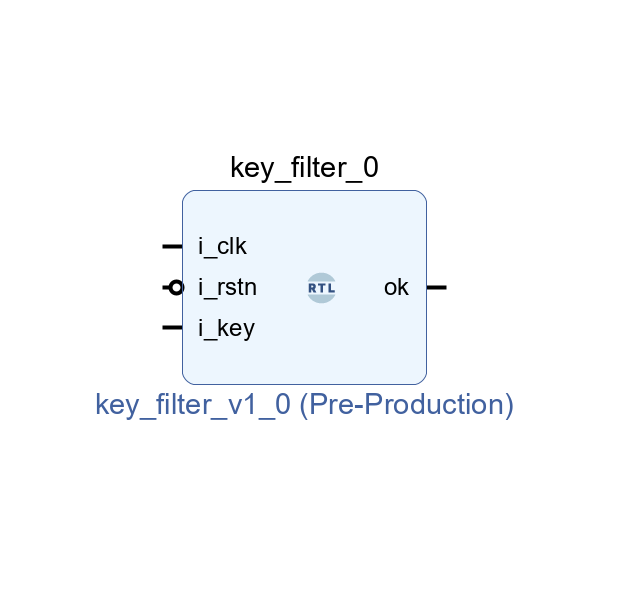

? ? ? ? (4)PL通過按鍵輸入一個啟動信號,因此需要添加一個按鍵消抖模塊key_filter,實現按鍵按下輸出一個時鐘周期的高電平脈沖,模塊時鐘周期為50MHz,正好是zynq配置提供給PL的時鐘頻率。新建key_filter.v源文件并完成verilog設計后,在 BD 界面空白處右鍵選擇“Add Module”,添加源文件,將按鍵消抖模塊 key_filter.v 添加進來,如圖所示:

????????(5)最后整體 bd 設計部分如圖所示:設計檢查、Generate Output Products、 Create HDL Wrapper、管腳約束、Gnerate Bitstream、Export Hardware(包含比特流文件)、啟動Vitis

三、軟件設計

#include "stdio.h"

#include "xil_printf.h"

#include "xil_cache.h"

#include "xil_io.h" //用于訪問內存映射的寄存器或外設:包含讀寫內存數據函數#define DDR3_DATA_BASEADDR 0x10000000 //宏定義DDR3數據存儲的起始地址(對應硬件設計中的配置)int main()

{int i;int data;int c;//關閉數據緩存Data Cache以免從緩存中讀取數據。因為對同一地址進行讀操作時,讀出的有可能是 Data Cache中緩存數據,而非 DDR中真正數據Xil_DCacheDisable();while(1){xil_printf("Enter 1 to start read data in DDR \r\n");scanf("%d",&c);if(c==1){//for循環從地址 0x1000_0000讀取 DDR3存儲器中的數據,讀取的存儲空間大小為 4KB。for(i=0; i<4096; i+=4)//i每次累加 4,因為調用Xil_In32()讀取內存數據,每次讀取 32bit。而內存地址以字節為單位,一次讀操作后地址應加 4。{//通過地址讀取32位數據data = Xil_In32(DDR3_DATA_BASEADDR + i);//打印地址和數據xil_printf("Address:%d Data:%d \r\n",(DDR3_DATA_BASEADDR+i), data);}}}return 0;

}

四、效果

1.不按按鍵(沒有向DDR寫數據)直接讀取DDR,可以看到打印的數據為隨機數。

2.按下按鍵后,僅指示讀寫操作結束的LED燈亮起(DDR數據讀寫成功),這時PS再讀取DDR,可以看到打印的數據為1到1024(一個數據32位,一共剛好?4Byte×1K=4KB數據),正是自定義IP寫入DDR的數據。

注意力機制(第3/4集),位置編碼)

馬爾科夫決策過程(MDP))

——LeetCode45.跳躍游戲II763.劃分字母區間)

:常見位運算操作總結)