控制單元的功能

文章目錄

- 控制單元的功能

- 9.1 微操作命令的分析

- 9.1.1 取指周期

- 9.1.2 間址周期

- 9.1.3 執行周期

- 9.1.4 中斷周期

- 9.2 控制單元的功能

- 9.2.1 控制單元的外特性

- 9.2.2 控制信號舉例

- 9.2.3 多級時序系統

- 9.2.4 控制方式

- 控制單元的設計

- 10.1 組合邏輯設計

- 10.1.1 組合邏輯控制單元框圖

- 10.1.2 微操作的節拍安排

- 10.1.3 組合邏輯設計步驟

- 10.2 微程序設計

- 10.2.1 微程序設計思想的產生

- 10.2.2 微程序控制單元框圖及工作原理

- 10.2.3 微指令的編碼方式(控制方式)

- 10.2.4 微指令序列地址的形成

- 10.2.5 微指令格式

- 10.2.6 靜態微程序設計和動態微程序設計

- 10.2.7 毫微程序設計

- 10.2.8 串行微程序控制和并行微程序控制

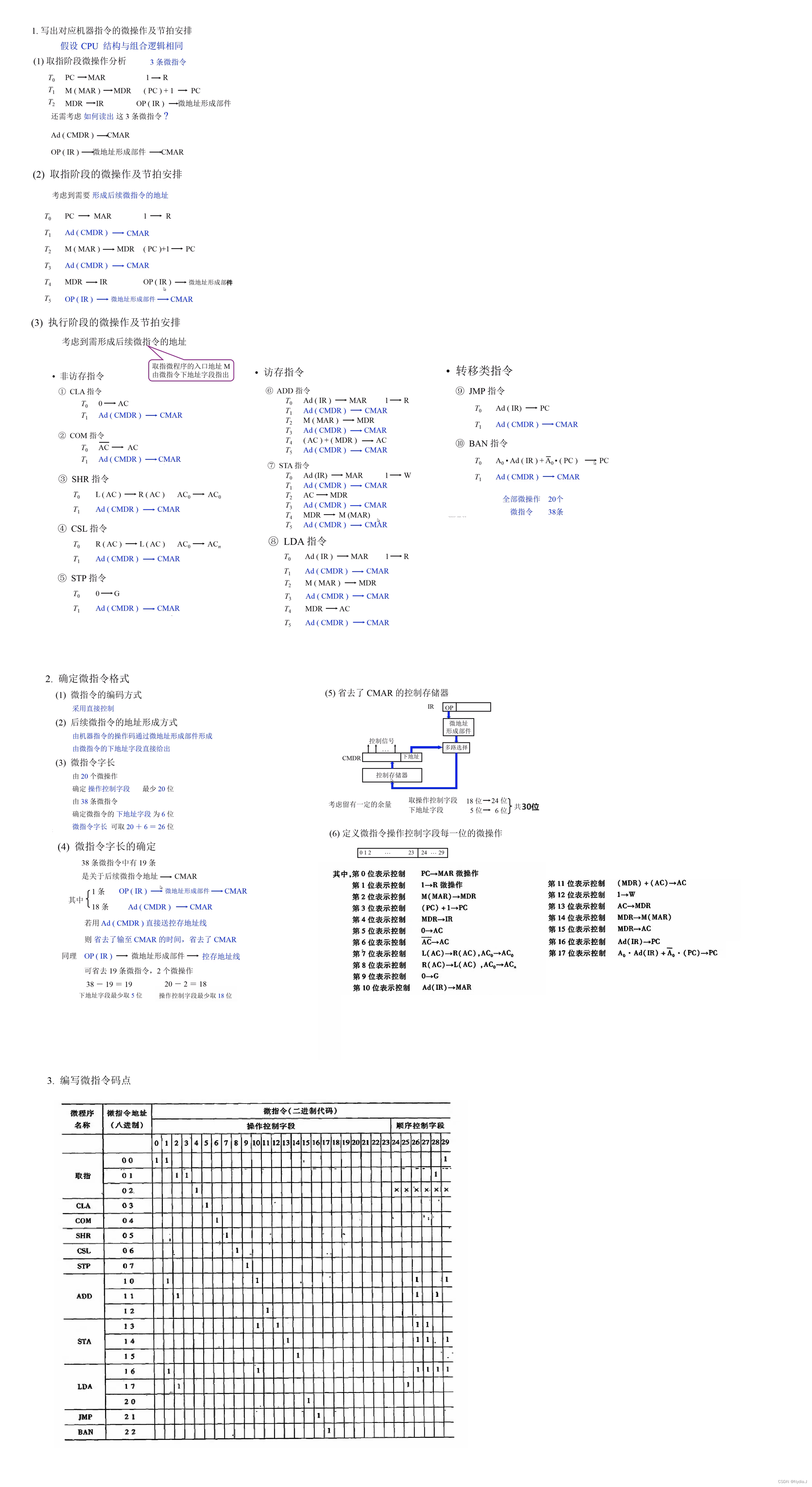

- 10.2.9 微程序設計舉例

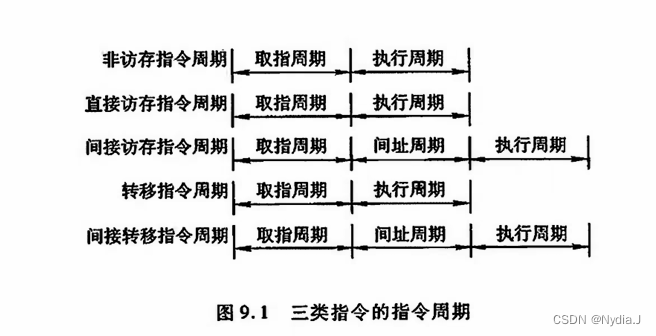

9.1 微操作命令的分析

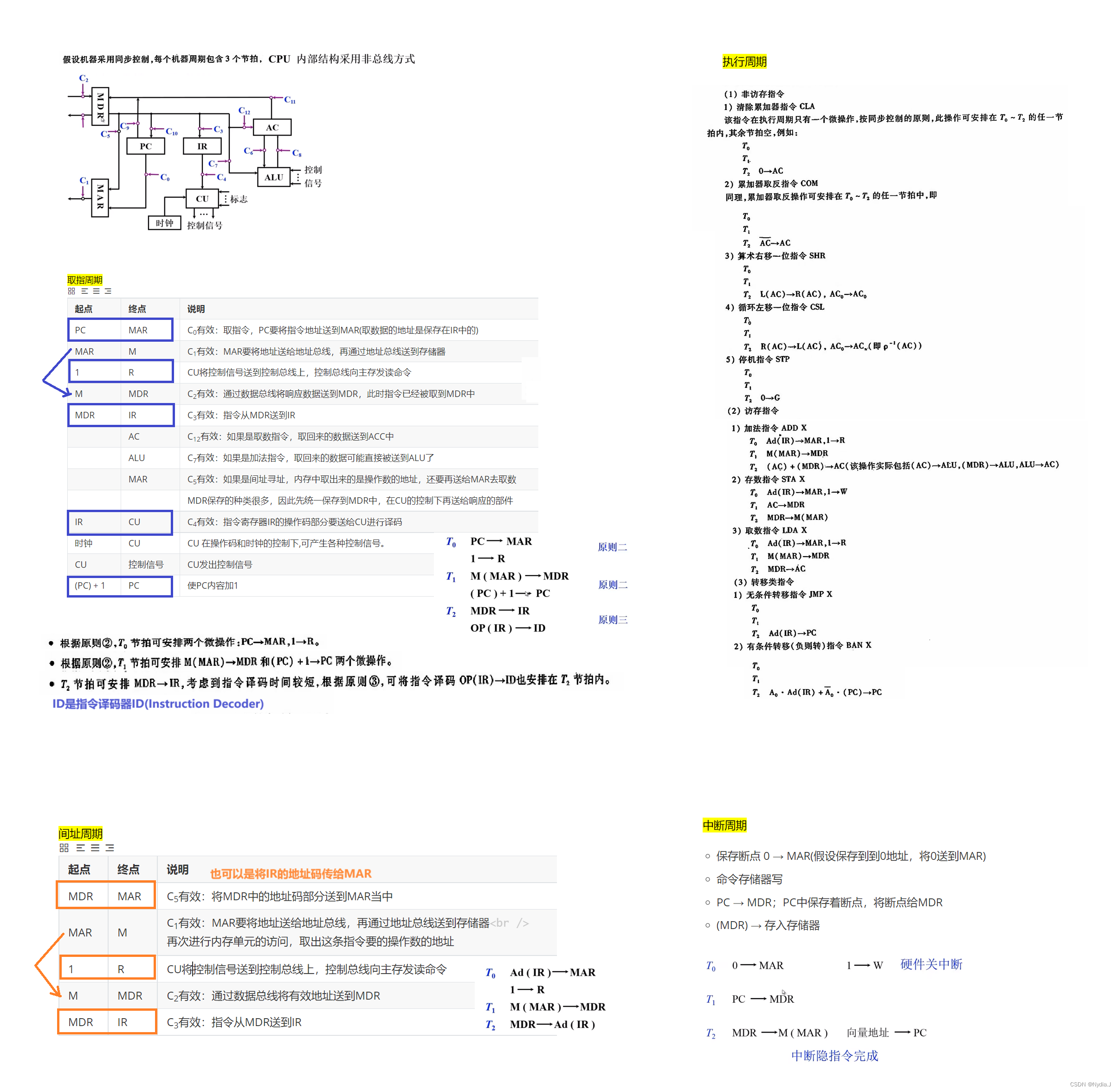

9.1.1 取指周期

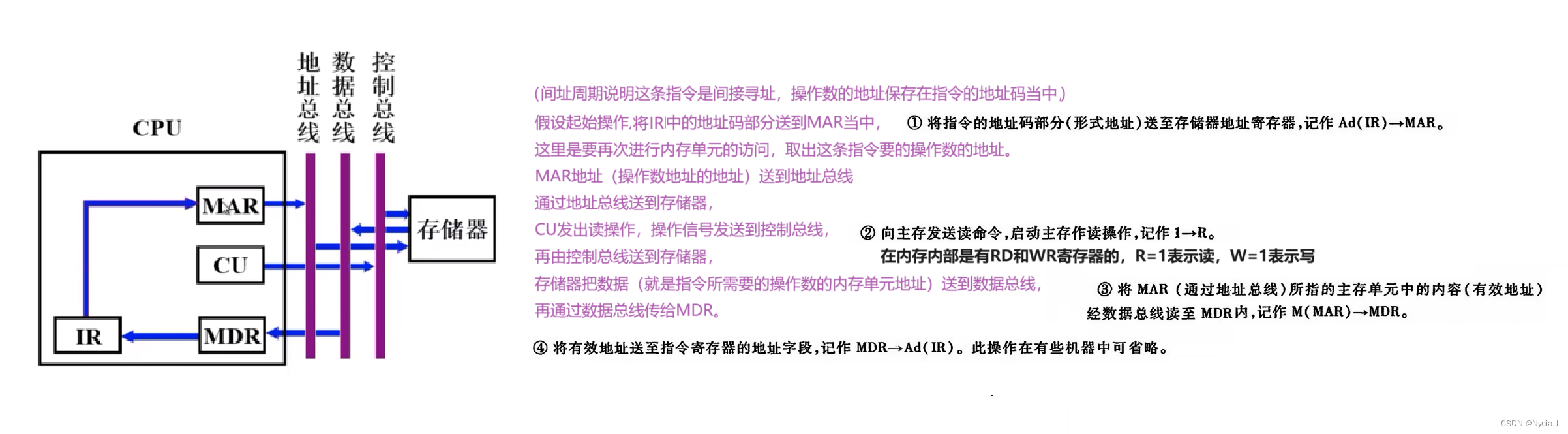

9.1.2 間址周期

9.1.3 執行周期

-

非訪存指令

指令 微操作 說明 CLA clear ACC,對ACC清零 0 → ACC COM 取反 ACC  ̄ \overline{\text{ACC}} ACC → ACC SHR 算術右移,左邊補上的是原來的符號位 L(ACC) → R(ACC), ACC0 → ACC0,就是將原來的符號位寫回到最高位 CSL 循環左移 R(ACC) → L(ACC),ACC0 → ACCn STP 停機指令 0 → G,計算機有個停機標志,置0即停機 -

訪存指令

指令 微操作 說明 ADD X 加法指令 將地址X中的數取出與ACC中相加再存入ACC中 Ad(IR) → MAR 操作數地址仍然是在IR中的,要將加數從內存取出 1 → R M(MAR) → MDR (ACC) + (MDR) → ACC STA X 存數指令 ACC中保存的數據存到內存單元給定的地址X中 Ad(IR) → MAR 將X的地址傳給存儲器 1 → W 寫的指令傳給主存 ACC → MDR MDR → M(MAR) LDA X 取數指令 X中的數據加載到ACC中 Ad(IR) → MAR 將X的地址傳給存儲器 1 → R M(MAR) → MDR MDR → ACC -

轉移指令

指令 微操作 說明 JMP X —— 無條件轉移 Ad(IR) → PC BAN X —— 條件轉移 A0 ? Ad(IR) + A0  ̄ \overline{\text{A0}} A0 ? (PC) → PC 負則轉,

如果上一條指令的結果是負數,

就跳轉到X地址的指令,

上一條指令的運算結果是在ACC中的,

判斷正負就看ACC的最高位A0 即可

9.1.4 中斷周期

| 任務 | 微操作 | 說明 |

|---|---|---|

| 保存斷點 | 0 → MAR(程序斷點存入"0"地址) 或 (SP)?1 → MAR(程序斷點進棧) | 保存斷點就是將斷點送入到內存單元中,有兩種方式: 1. 程序斷點存入"0"地址 2. 程序斷點進棧 二者在操作上唯一的不同就是:斷點保存的地址不同 |

| 1 → W | ||

| PC → MDR | 程序斷點原在PC中的 | |

| MDR → M(MAR) | ||

| 形成中斷服務程序入口地址 | (中斷識別程序入口地址)M → PC | 軟件查詢法 |

| 向量地址 → PC | 硬件查詢法 | |

| 關中斷 | 0 → EINT | EINT置0,就關中斷了 |

9.2 控制單元的功能

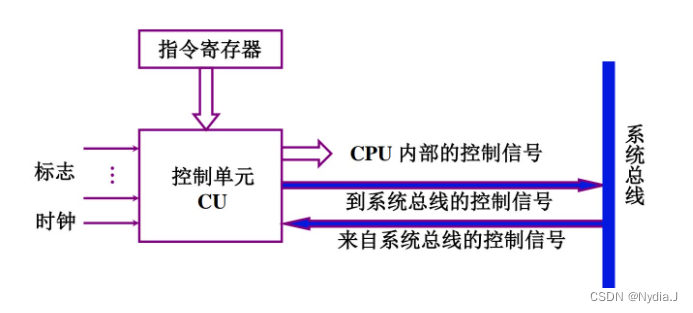

9.2.1 控制單元的外特性

-

輸入信號

輸入信號 說明 指令寄存器 OP(IR) → CU,IR保存了要執行的那條指令,將指令的操作碼送到CU進行譯碼,指出指令要做的操作,控制信號與操作碼有關 時鐘 為了使控制單元按一定的先后順序、一定的節奏發出各個控制信號,控制單元必須受時鐘控制,即每一個時鐘脈沖使控制單元發送一個操作命令,或發送一組需要同時執行的操作命今 標志 控制單元有時需依賴CPU當前所處的狀態(如ALU操作的結果)產生控制信號

如BAN指令,控制單元要根據上條指令的結果是否為負而產生不同的控制信號;

再如條件轉移指令所需要判斷的條件就是標志外來信號 (來自系統總線(控制總線)的控制信號)

來自CPU外部的信號也會進入CU,以便CU對整個系統的硬件資源發出命令,進行管理。比如INTR中斷請求,HRQ總線請求 -

輸出信號

輸出信號 指令舉例 說明 CPU內部的各種控制信號,控制CPU內部的部件做相應的操作 Ri → Rj 寄存器之間的數據傳輸 (PC)+1 → PC 更新PC指令 ALU 算術運算(加、減)、邏輯運算(與、或) CPU內部運算器執行的操作 送至控制總線的信號,控制IO、總選、存儲體的信號 MREQ  ̄ \overline{\text{MREQ}} MREQ? 訪問存儲體控制信號 IO  ̄ \overline{\text{IO}} IO/M 訪IO/存儲體的控制信號,低電平是IO,高電平是存儲體 RD 存儲器讀命令 WR 存儲器寫命令 INTA 中斷響應信號,CPU發出,響應中斷源的中斷請求 HLDA 總線應答信號,響應外設發出的總線使用請求

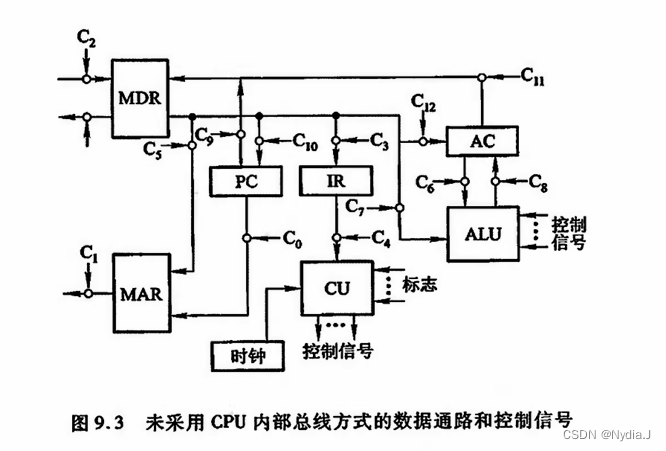

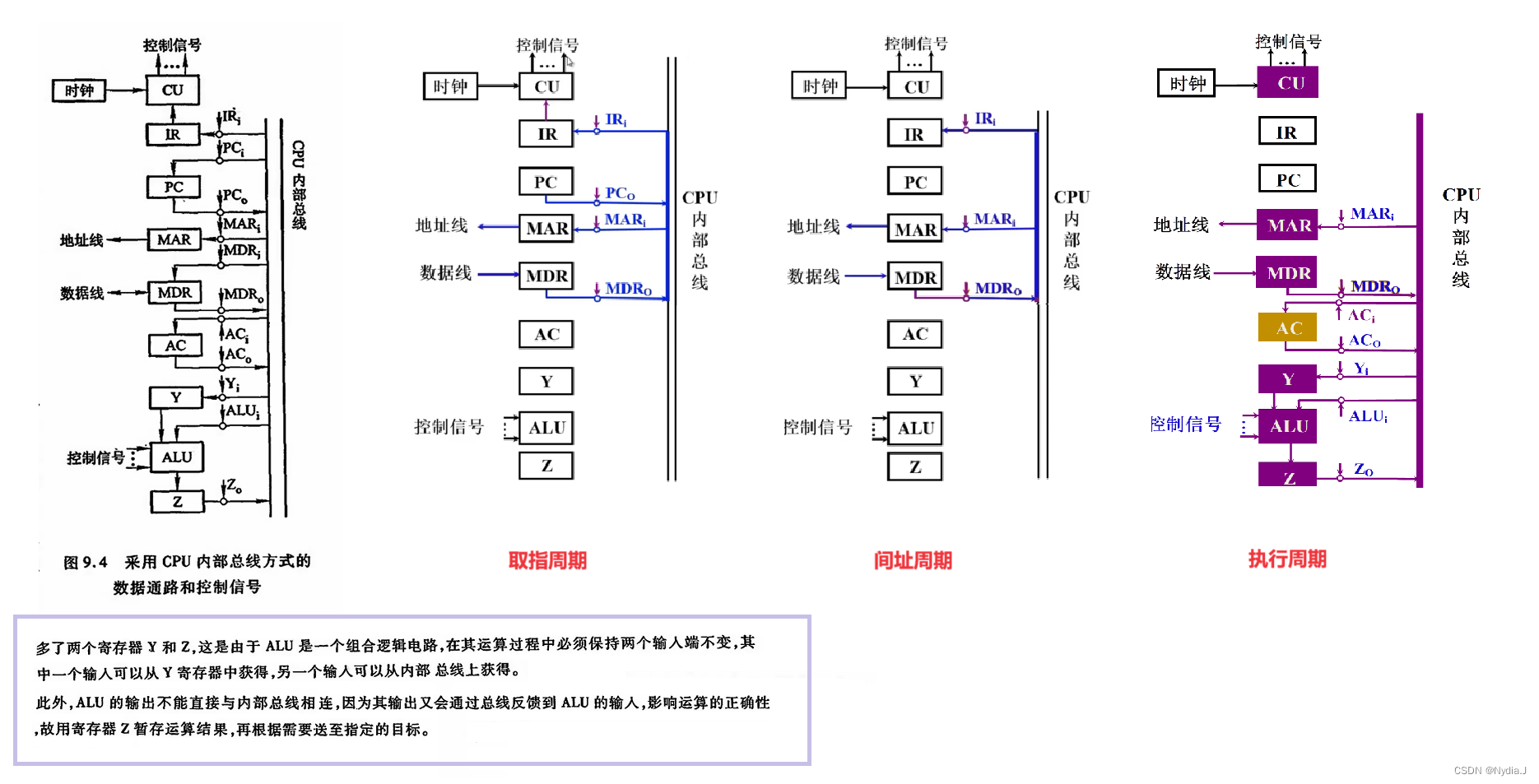

9.2.2 控制信號舉例

-

不采用 CPU 內部總線的方式

?

以ADD @X為例

取指周期

起點 終點 說明 PC MAR C0有效:取指令,PC要將指令地址送到MAR(取數據的地址是保存在IR中的) MAR M C1有效:MAR要將地址送給地址總線,再通過地址總線送到存儲器 1 R CU將控制信號送到控制總線上,控制總線向主存發讀命令 M MDR C2有效:通過數據總線將響應數據送到MDR,此時指令已經被取到MDR中 MDR IR C3有效:指令從MDR送到IR AC C12有效:如果是取數指令,取回來的數據送到ACC中 ALU C7有效:如果是加法指令,取回來的數據可能直接被送到ALU了 MAR C5有效:如果是間址尋址,內存中取出來的是操作數的地址,還要再送給MAR去取數 MDR保存的種類很多,因此先統一保存到MDR中,在CU的控制下再送給響應的部件 IR CU C4有效:指令寄存器IR的操作碼部分要送給CU進行譯碼 時鐘 CU CU 在操作碼和時鐘的控制下,可產生各種控制信號。 CU 控制信號 CU發出控制信號 (PC) + 1 PC 使PC內容加1 間址周期

起點 終點 說明 MDR MAR C5有效:將MDR中的地址碼部分送到MAR當中 MAR M C1有效:MAR要將地址送給地址總線,再通過地址總線送到存儲器

再次進行內存單元的訪問,取出這條指令要的操作數的地址1 R CU將控制信號送到控制總線上,控制總線向主存發讀命令 M MDR C2有效:通過數據總線將有效地址送到MDR MDR IR C3有效:指令從MDR送到IR 執行周期

起點 終點 說明 MDR MAR C5有效:將MDR中的地址碼部分送到MAR當中 MAR M C1有效:MAR要將地址送給地址總線,再通過地址總線送到存儲器 1 R CU將控制信號送到控制總線上,控制總線向主存發讀命令 M MDR C2有效:通過數據總線將操作數送到MDR(此時加數在MDR,被加數在AC) 控制信號 ALU C6、C7同時有效:通過CPU內部控制總線對ALU發“ADD”加控制信號,完成AC的內容和MDR的內容相加。 (AC) + (MDR) AC C8同時有效:將求和結果存入 AC。 C9和C10分別是控制PC的輸出和輸人的控制信號,

C11和C12分別是控制AC的輸出和輸入的控制信號。 -

采用 CPU 內部總線方式

?

以ADD @X為例

取指周期

起點 終點 說明 PC MAR PCo和MARi有效:PC的值經由CPU內部總線送到MAR(保存的是下一條要執行的指令地址) MAR 地址線 MAR把地址送到地址線 1 R CU發出讀命令,讀命令是通過控制線送到存儲器 數據線 MDR 讀出來的指令通過數據線送到MDR(保存的是取回來的間接尋址的加法值) MDR IR MDRo和IRi有效:在控制信號的控制之下輸出到CPU內部總線,通過總線輸入到IR中

IR就保存了要執行的加法指令OP(IR) CU 指令寄存器IR的操作碼部分要送給CU進行譯碼 (PC) + 1 PC 使PC內容加1 間址周期

起點 終點 說明 MDR MAR MDRo和MARi有效:MDR通過CPU的內部總線將形式地址送入到MAR中 MAR 地址線 MAR將地址送到地址線 1 R CU發出讀命令,讀命令是通過控制線送到存儲器 數據線 MDR 讀出的內容(有效地址)經過數據線送入到MDR中 MDR IR MDRo和IRi有效:MDR通過CPU的內部總線將有效地址送入到IR中 執行周期

起點 終點 說明 MDR MAR MDRo和MARi有效:MDR通過CPU的內部總線將操作數的地址送入到MAR中 MAR 地址線 MAR將地址送到地址線 1 R CU發出讀命令,讀命令是通過控制線送到存儲器 數據線 MDR 讀出的內容(操作數)經過數據線送入到MDR中 MDR Y MDRo和Yi有效:MDR通過CPU的內部總線將操作數送入到Y寄存器中 Y ALU Y中操作數送到ALU,另一個操作數在AC中 AC ALU ACo和ALUi有效:AC中操作數經由CPU內部總線送到ALU中 (AC) + (Y) Z 加法結果保存到Z中 Z AC Zo和ACi有效:加法結果經由CPU內部總線送到AC中

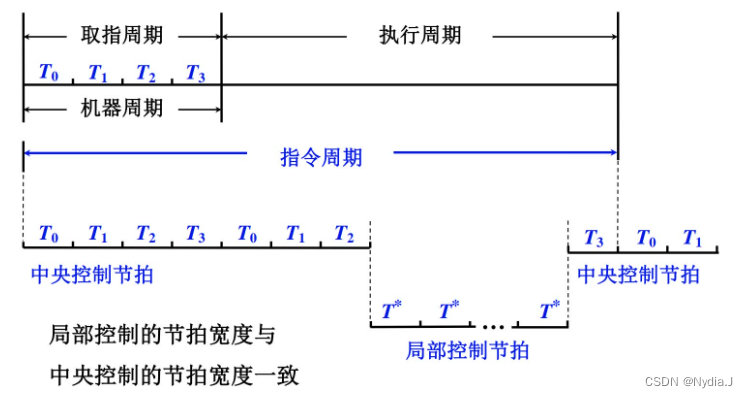

9.2.3 多級時序系統

-

機器周期

-

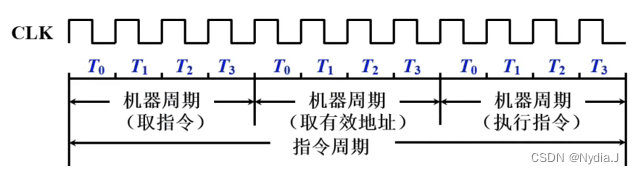

概念:所有指令執行過程中的一個基準時間

-

確定機器周期需考慮的因素:每條指令的執行步驟,每一步驟所需的時間,將每個步驟劃分到不同機器周期中

-

基準時間的確定:

-

通常情況下:

在指令執行的過程中(取指、間址、執行、中斷)以完成最復雜指令功能的微操作的時間為準

實際上,最復雜的通常都是是訪存操作,因此,以訪問一次存儲器的時間為基準若指令字長 = 存儲字長,取指周期 = 機器周期

-

-

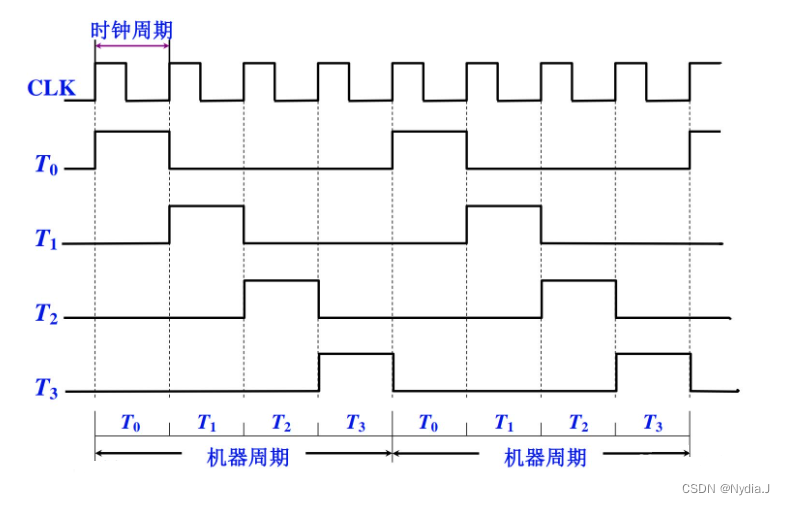

時鐘周期

-

一個機器周期內可完成若干個微操作,每個微操作需一定的時間,有些微操作在一個時鐘周期內完成,有些微操作可能花費多個時鐘周期(比如對內存的訪問)

將一個機器周期分成若干個時間相等的時間段(節拍、狀態、時鐘周期),由時鐘周期控制在一個機器周期內部微操作的先后順序。 -

時鐘周期是控制計算機操作的最小單位時間。用時鐘周期控制產生一個或幾個微操作命令(控制幾個微操作命令的情況一般是指這些微操作可以并行執行)

-

-

多級時序系統

-

機器周期、節拍(狀態)組成多級時序系統;

-

一個指令周期包含若干個機器周期、一個機器周期包含若干個時鐘周期。

-

機器速度與機器主頻的關系

-

機器速度不僅與主頻有關 ,還與一個機器周期中所含時鐘周期(主頻的倒數)數以及指令周期中所含的機器周期數有關。

即使這兩個一樣,一臺采用流水,一臺采用非流水,結果也是不一樣的。 -

假設兩臺機器都采用非流水方式,并且在一個指令周期當中,包含的機器周期的數量是相同的 ,在機器周期所含節拍數也相同的,那么兩機平均指令執行速度之比就等于兩機主頻之比

M I P S 1 M I P S 2 = f 1 f 2 \frac{MIPS_1}{MIPS_2} = \frac{f_1}{f_2} MIPS2?MIPS1??=f2?f1??

-

9.2.4 控制方式

產生不同微操作命令序列所用的時序控制方式

-

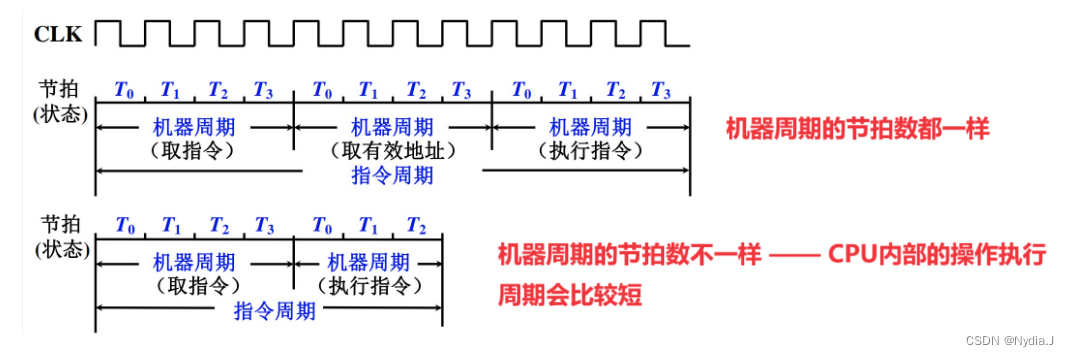

同步控制方式 - 任何一條指令或指令中任何一個微操作的執行都是事先確定的,并且都是受統一基準時標的時序信號所控制的方式。(一定有一個統一的,定寬定距的時鐘作為標準,每一個微操作都是在這個時鐘的控制下,在指定的節拍產生。)

-

采用定長的機器周期

每個機器周期含有相同數量的節拍數,這個時候機器周期以最長的微操作序列和最復雜的微操作作為標準。可能會在某些執行階段造成時間浪費。 -

采用不定長的機器周期

每個機器周期內的節拍數可以不等,這種控制方式可解決微操作執行時間不統一的問題。 通常把大多數微操作安排在一個較短的機器周期內完成,而對某些復雜的微操作,采用延長機器周期或增加節拍的辦法來解決。 -

采用中央控制和局部控制相結合的方法

將機器的大部分指令安排在統一的、較短的機器周期內完成,稱為中央控制,而將少數操作復雜的指令中的某些操作(如乘除法和浮點運算等)采用局部控制方式來完成

-

-

異步控制方式

- 無基準時標信號

- 無固定的周期節拍和嚴格的時鐘同步

- 采用 應答方式

- 當CU發出執行某一微操作的控制信號后,等待執行部件完成了該操作后發回“回答”(或“結束”)信號,再開始新的微操作,使CPU沒有空閑狀態,但因需要采用各種應答電路,故其結構比同步控制方式復雜

-

聯合控制方式

- 同步控制和異步控制相結合。這種方式對各種不同指令的微操作實行大部分統一、小部分區別對待的辦法。

- 對每條指令都有的取指令操作,采用同步方式控制;

對那些時間難以確定的微操作,如 I/O操作,則采用異步控制,

以執行部件送回的“回答"信號作為本次微操作的結束。

-

人工控制方式

? 為了調機和軟件開發的需要,在機器面板或內部設置一些開關或按鍵,來達到,工控制的目的。

? (1) Reset(復位)鍵

? 按下 Reset 鍵,使計算機處于初始狀態。當機器出現死鎖狀態或無法繼續運行時,可按此鍵。若在機器運行時按此鍵,將會破壞機器內某些狀態而引起錯誤,因此要慎用。有些微型計算機未設此鍵,當機器死鎖時,可采用停電后再加電的辦法重新啟動計算機。

? (2) 連續或單條執行轉換開關

? 由于調機的需要,有時需要觀察執行完一條指令后的機器狀態,有時又需要觀察連續運行程序后的結果,設置連續或單條執行轉換開關,能為用戶提供這兩種選擇。? (3) 符合停機開關

? 這組開關指示存儲器的位置,當程序運行到與開關指示的地址相符時,機器便停止運行,稱為符合停機。

控制單元的設計

10.1 組合邏輯設計

10.1.1 組合邏輯控制單元框圖

?

10.1.2 微操作的節拍安排

- 安排微操作時序的原則

- ① 原則一 微操作的先后順序不得隨意更改

- ② 原則二 被控對象不同 的微操作盡量安排在一個節拍內完成(可以并行操作且沒有先后順序的微操作)

- ③ 原則三 占用 時間較短 的微操作盡量安排在一個節拍內完成 并允許有先后順序

?

10.1.3 組合邏輯設計步驟

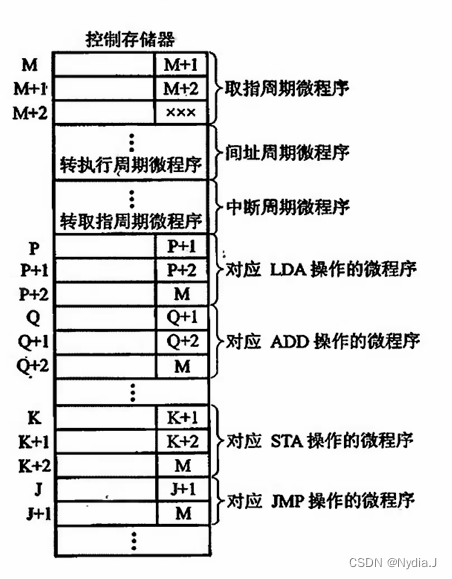

10.2 微程序設計

10.2.1 微程序設計思想的產生

完成一條機器指令 需要 一個或者多個微操作命令,這些微操作命令存儲起來變成微指令,每個節拍對應一個微指令,那么多個節拍對應的多個微指令就構成了微程序。微指令由0、1組成,每一個位置對應某一種或某一個微操作命令。即一條機器指令對應一個微程序。

微程序存入ROM中,執行時把微指令一條一條的從ROM讀出,根據讀出的微指令中有效控制信號的位置發出相應的信號,讓計算機執行相應的操作 —— 存儲邏輯(把邏輯信號存儲在存儲器中)

?

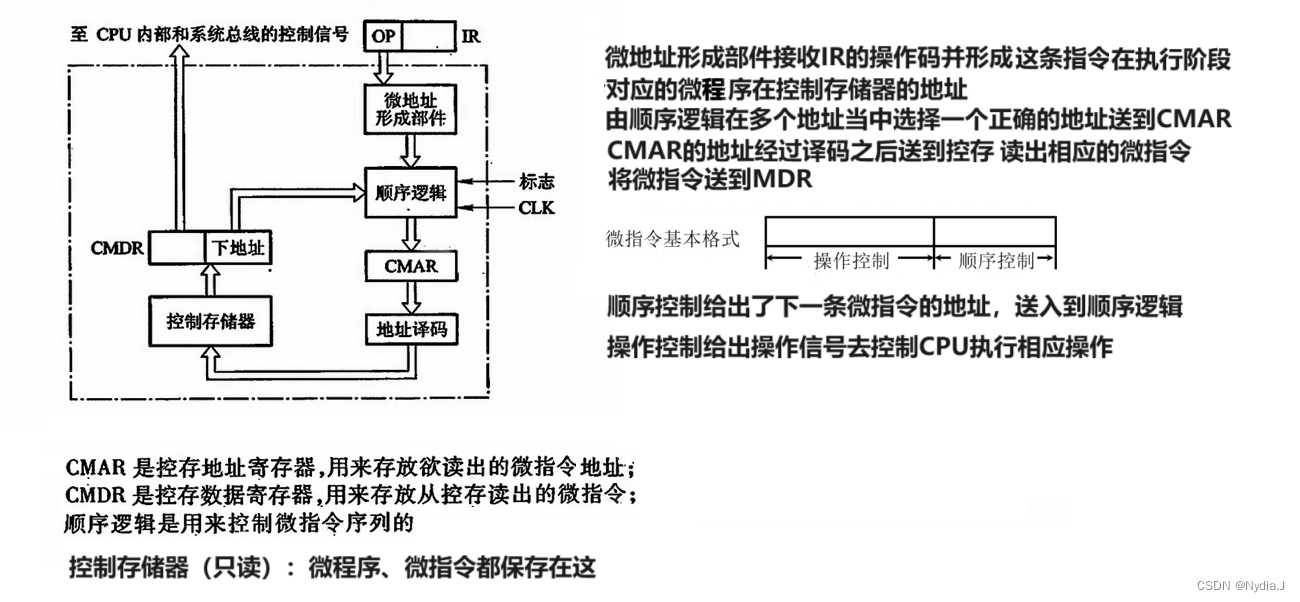

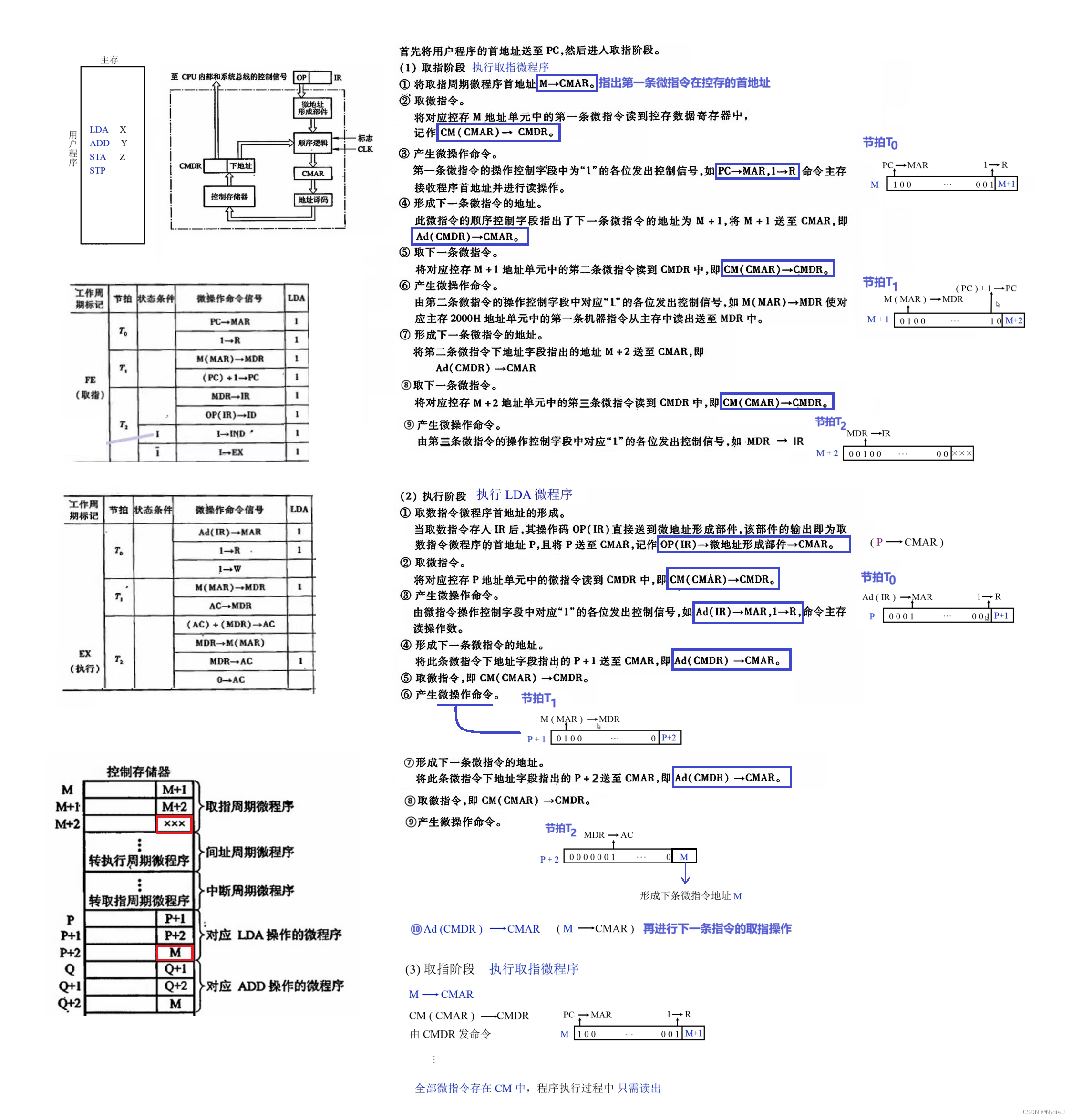

10.2.2 微程序控制單元框圖及工作原理

-

機器指令對應的微程序

-

微程序控制單元的基本框圖

-

工作原理

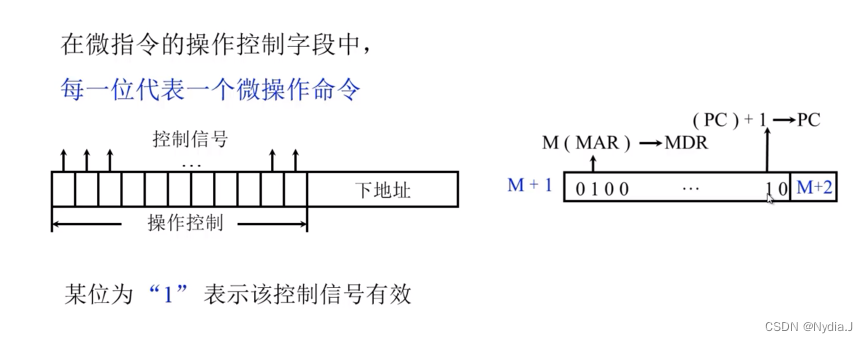

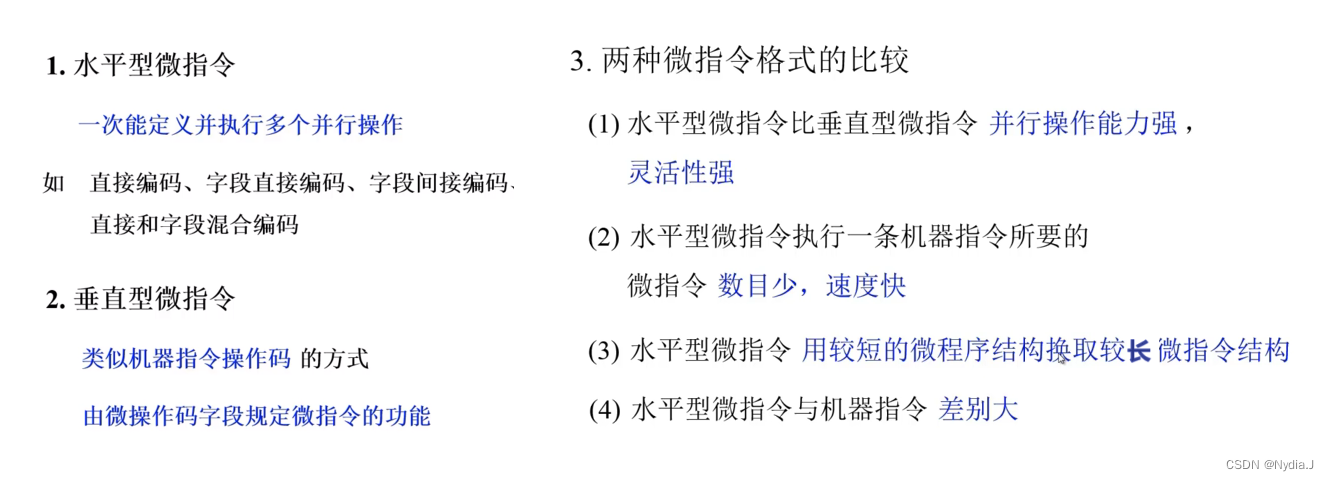

10.2.3 微指令的編碼方式(控制方式)

-

直接編碼(直接控制)方式

?

-

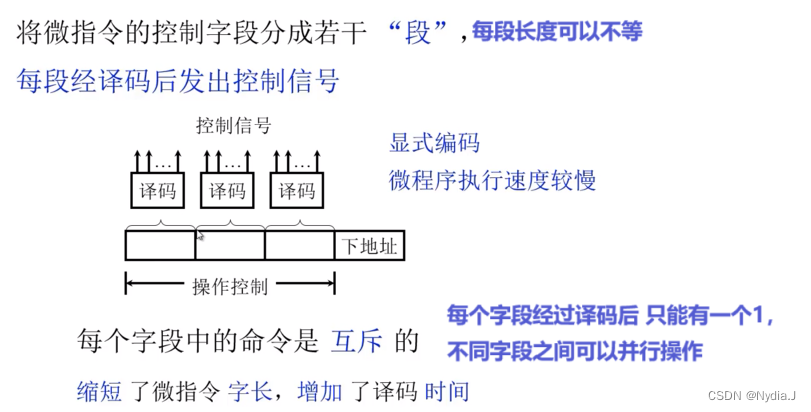

字段直接編碼方式

-

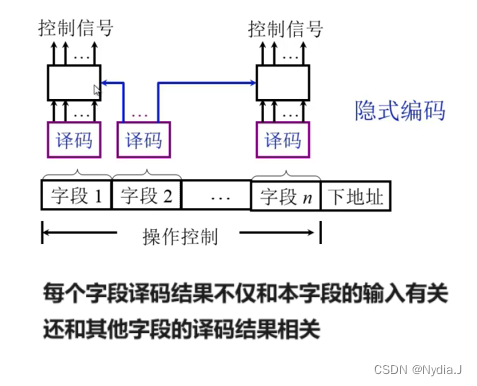

字段間接編碼方式

?

-

混合編碼

直接編碼和字段編碼(直接和間接)混合使用

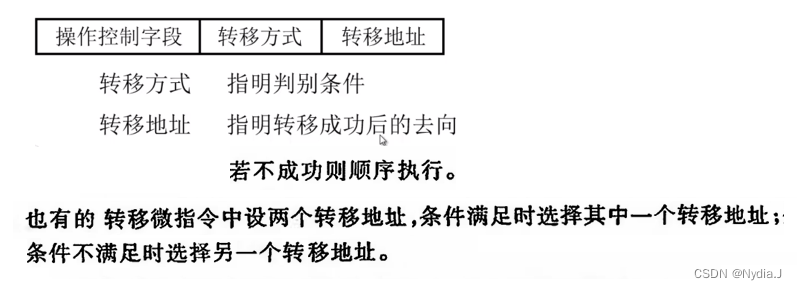

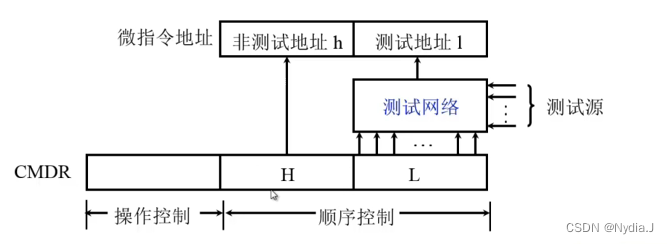

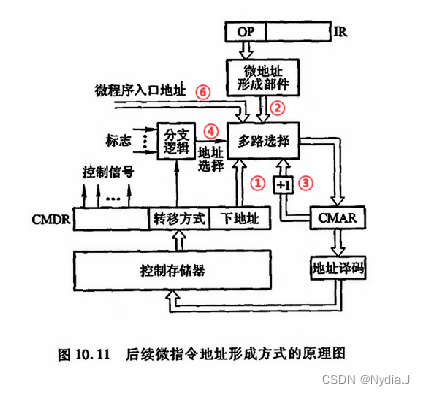

10.2.4 微指令序列地址的形成

-

直接由微指令的下地址字段指出

-

根據機器指令的操作碼形成

當機器指令取至指令寄存器后,微指令的地址由操作碼經微地址形成部件形成。微地址形成部件實際是一個編碼器,其輸人為指令操作碼,輸出就是對應該機器指令微程序的首地址。

-

增量計數器法

在很多情況下,后續微指令的地址是連續的,因此對于順序地址,微指令可采用增量計數法,即(CMAR)+1 CMAR來形成后續微指令的地址。

-

分支轉移

-

通過測試網絡 - 用于微程序小范圍內跳轉

-

由硬件產生微程序人口地址

第一條微指令地址由專門 硬件產生

中斷/間址周期 由硬件產生中斷周期微程序首地址

?

10.2.5 微指令格式

10.2.6 靜態微程序設計和動態微程序設計

- 靜態微程序設計:通常指令系統是固定的,對應每一條機器指令的微程序是計算機設計者事先編好的,因此一般微程序無須改變,其控制存儲器采用ROM。

- 動態微程序設計:人們可以通過改變微指令和微程序來改變機器的指令系統,有利于仿真,采用 EPROM作為控制存儲器。但是這種設計對用戶的要求很高,目前難以推廣。

10.2.7 毫微程序設計

微程序可看做是解釋機器指令的,毫微程序可看做是解釋微程序的,而組成微程序的毫微指令則是用來解釋微指令的。

10.2.8 串行微程序控制和并行微程序控制

10.2.9 微程序設計舉例

參考:

教材:計算機組成原理 (唐朔飛).pdf

博客:https://blog.csdn.net/weixin_51825055/article/details/133738724

視頻:https://www.bilibili.com/video/BV1t4411e7LH?p=126&vd_source=a89593e8d33b31a56b894ca9cad33d33

![[Algorithm][動態規劃][子序列問題][最長遞增子序列的個數][最長數對鏈]詳細講解](http://pic.xiahunao.cn/[Algorithm][動態規劃][子序列問題][最長遞增子序列的個數][最長數對鏈]詳細講解)

服務端Filter)

)

win10、11鏡像文件)

![PS Mac Photoshop 2024 for Mac[破]圖像處理軟件[解]PS 2024安裝教程[版]](http://pic.xiahunao.cn/PS Mac Photoshop 2024 for Mac[破]圖像處理軟件[解]PS 2024安裝教程[版])