一、時鐘

1.時鐘系統基本概念

(1)PLL (鎖相環, Phase-Locked Loop)

作用:PLL是一種反饋控制電路,用于生成穩定的高頻時鐘信號。它通過將輸出時鐘與參考時鐘進行比較和調整,可以產生比輸入參考時鐘頻率高得多的輸出時鐘。倍頻??Fin * n = Fout

特點:

倍頻功能:可將低頻參考時鐘倍頻為高頻時鐘

低抖動:輸出時鐘穩定性好

可編程性:可通過寄存器配置倍頻系數

(2)Prescaler (預分頻器)

作用:用于對輸入時鐘進行分頻,降低時鐘頻率。分頻? Fin / m = Fout

特點:

分頻比可配置 (通常為2的冪次方或整數分頻)

用于將高速時鐘分頻為適合外設工作的頻率

可級聯使用實現更大的分頻比

(3)FPD (Fractional Post Divider,相位項數分頻器?)

作用:提供更精細的時鐘分頻能力,可以實現非整數分頻比。既能倍頻也能分頻??(Fin * n) / m = Fout

特點:

支持分數分頻 (如4.5分頻)

提供更靈活的時鐘配置

通常用于需要特定頻率但整數分頻無法滿足的場景

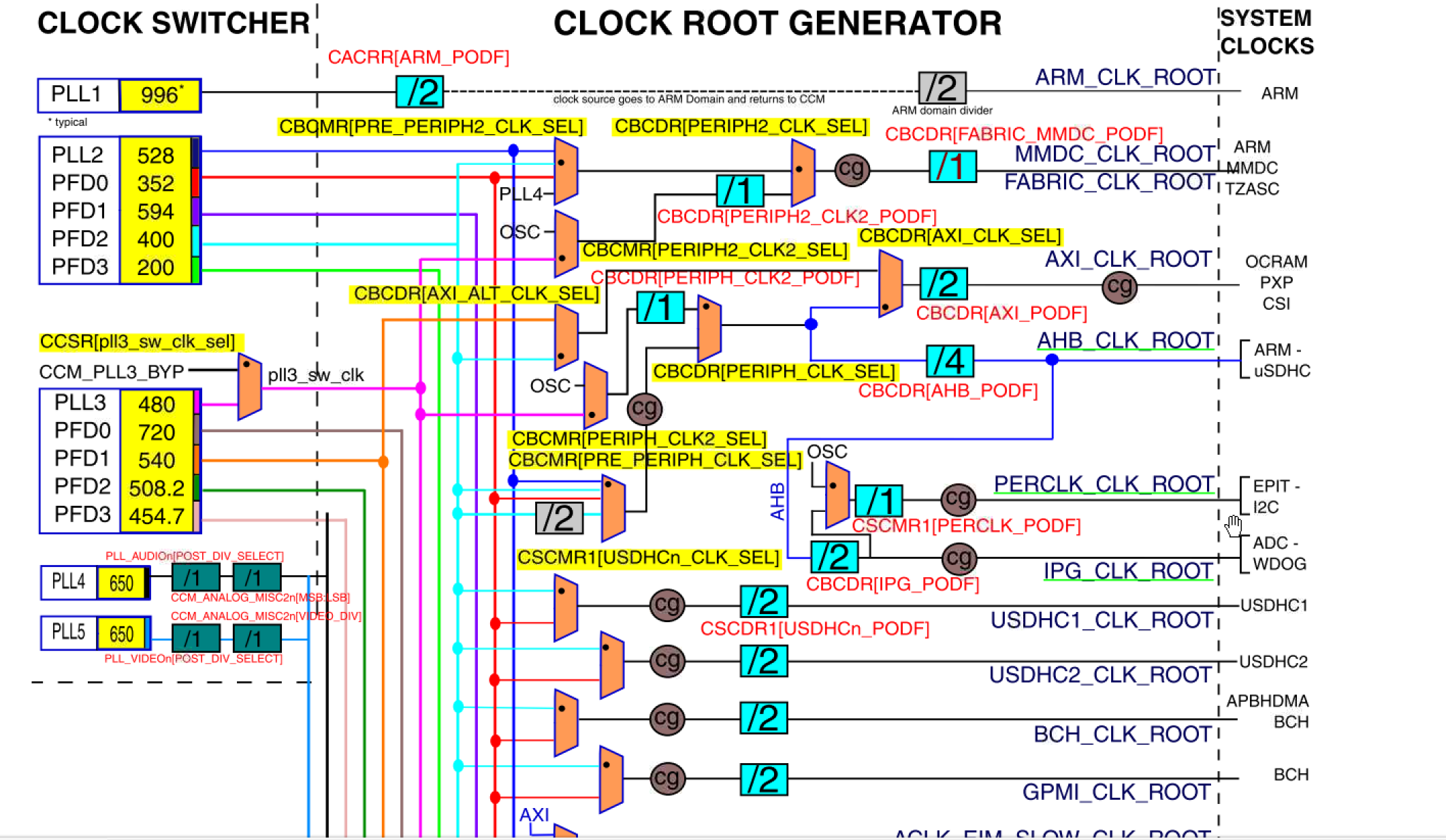

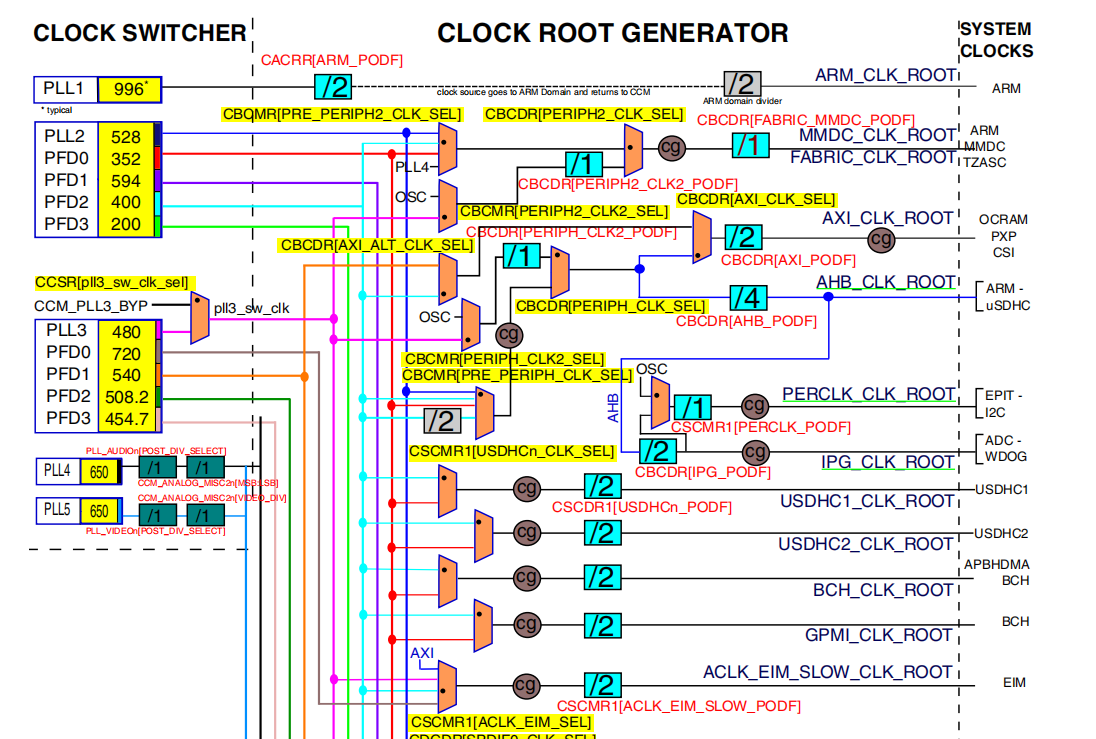

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ??時鐘樹

2.IMX6ULL中的PLL和PFD

(1)PLL數量

IMX6ULL中有7個PLL:

ARM PLL (用于ARM內核)

SYSTEM PLL (系統主PLL)

USB1 PLL (USB1專用)

USB2 PLL (USB2專用)

AUDIO PLL (音頻子系統)

VIDEO PLL (視頻處理)

ENET PLL (以太網專用)

(2)PFD數量

IMX6ULL的每個PLL有4個PFD?(Phase Fractional Dividers),因此總共有:

7個PLL × 4個PFD = 28個PFD

二、EPIT定時器

1.定義

? ? ? ?EPIT 的全稱是:Enhanced Periodic Interrupt Timer,增強的周期中斷定時器, 它主要是完成周期性中斷定時的。

? ? ? ??s3c2440里面的定時器還有很多其它的功能,比如輸入捕獲、PWM 輸出等等。但是 I.MX6U 的 EPIT 定時器只是完成周期性中斷定時的,僅此一項功能!至于輸入捕獲、 PWM 輸出等這些功能,I.MX6U 由其它的外設來完成。????????EPIT 是一個 32 位定時器,在處理器幾乎不用介入的情況下提供精準的定時中斷,軟件使能以后 EPIT 就會開始運行.

2.EPIT 定時器特點

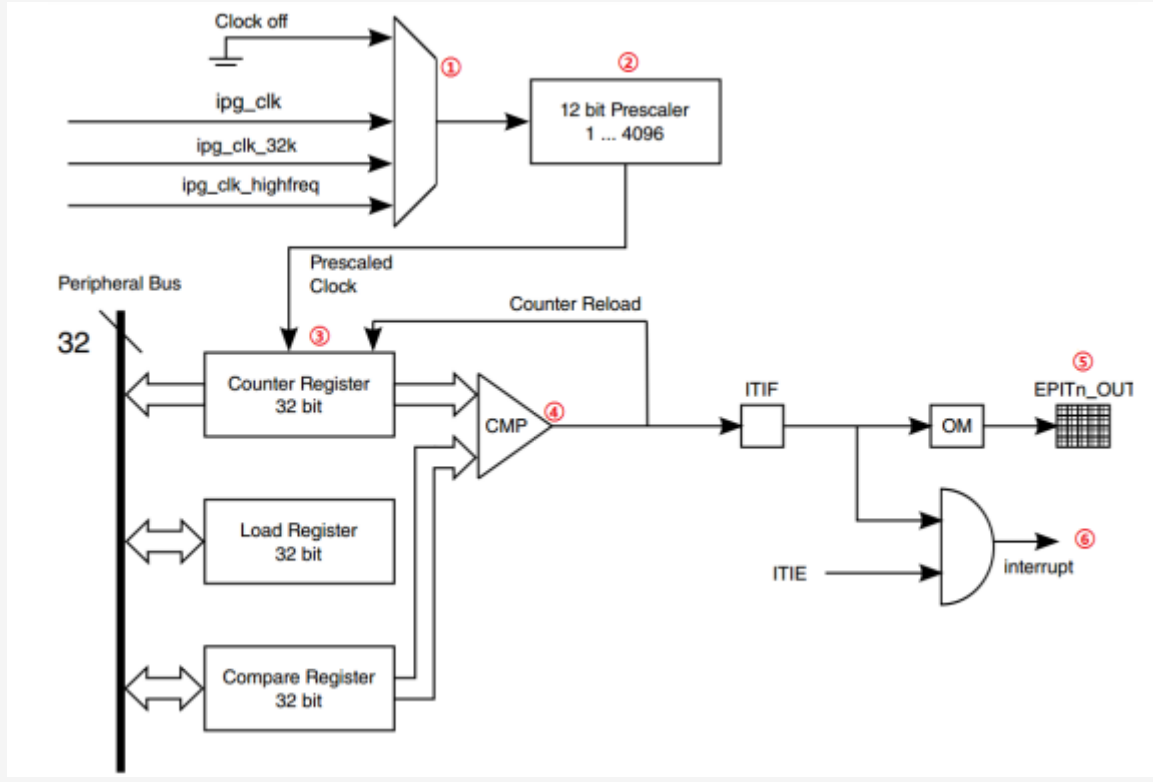

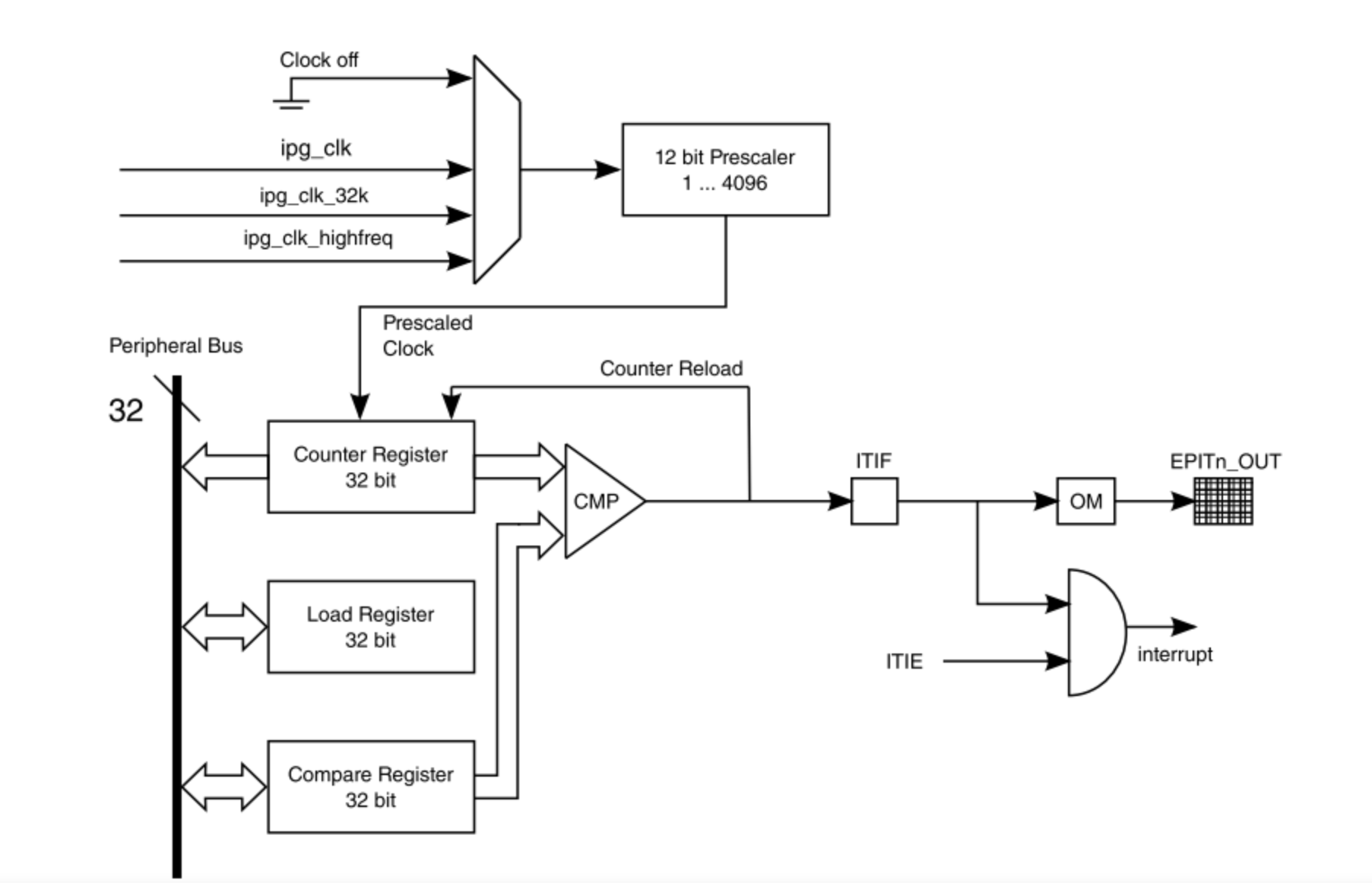

3.EPIT結構圖

① 這是個多路選擇器,用來選擇 EPIT 定時器的時鐘源,EPIT 共有 3 個時鐘源可選擇,ipg_clk、ipg_clk_32k 和 ipg_clk_highfreq,ipg_clk我們之前已經配置好了——66MHz;② 這是一個 12 位的分頻器,負責對時鐘源進行分頻,12 位對應的值是 0~4095,對應著1~4096 分頻.③ 經過分頻的時鐘進入到 EPIT 內部,在 EPIT 內部有三個重要的寄存器:計數寄存器(EPIT_CNR)、加載寄存器(EPIT_LR)和比較寄存器(EPIT_CMPR),這三個寄存器都是 32 位的。EPIT 是一個向下計數 器,也就是說給它一個初值,它就會從這個給定的初值開始遞減,直到減為 0,計數寄存器里面保 存的就是當前的計數值。如果 EPIT 工作在 set-and-forget 模式下,當計數寄存器里面的值減少到 0,EPIT 就會重新從加載寄存器讀取數值到計數寄存器里面,重新開始向下計數;④ 比較器,比較寄存器里面保存的數值用于和計數寄存器里面的計數值比較,如果相等的話就會產生 一個比較事件;⑤ EPIT 可以設置引腳輸出,如果設置了的話就會通過指定的引腳輸出信號;⑥ 產生比較中斷,也就是定時中斷。

4.EPIT兩種工作模式

5.相關配置

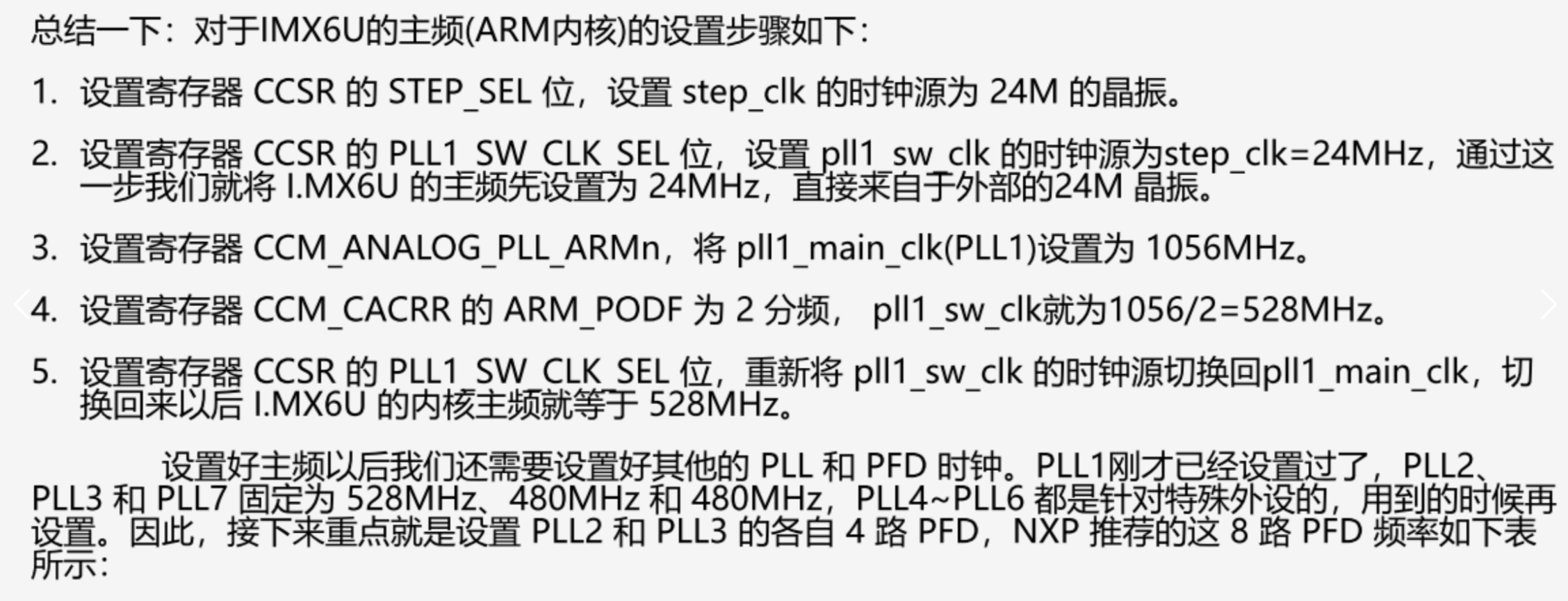

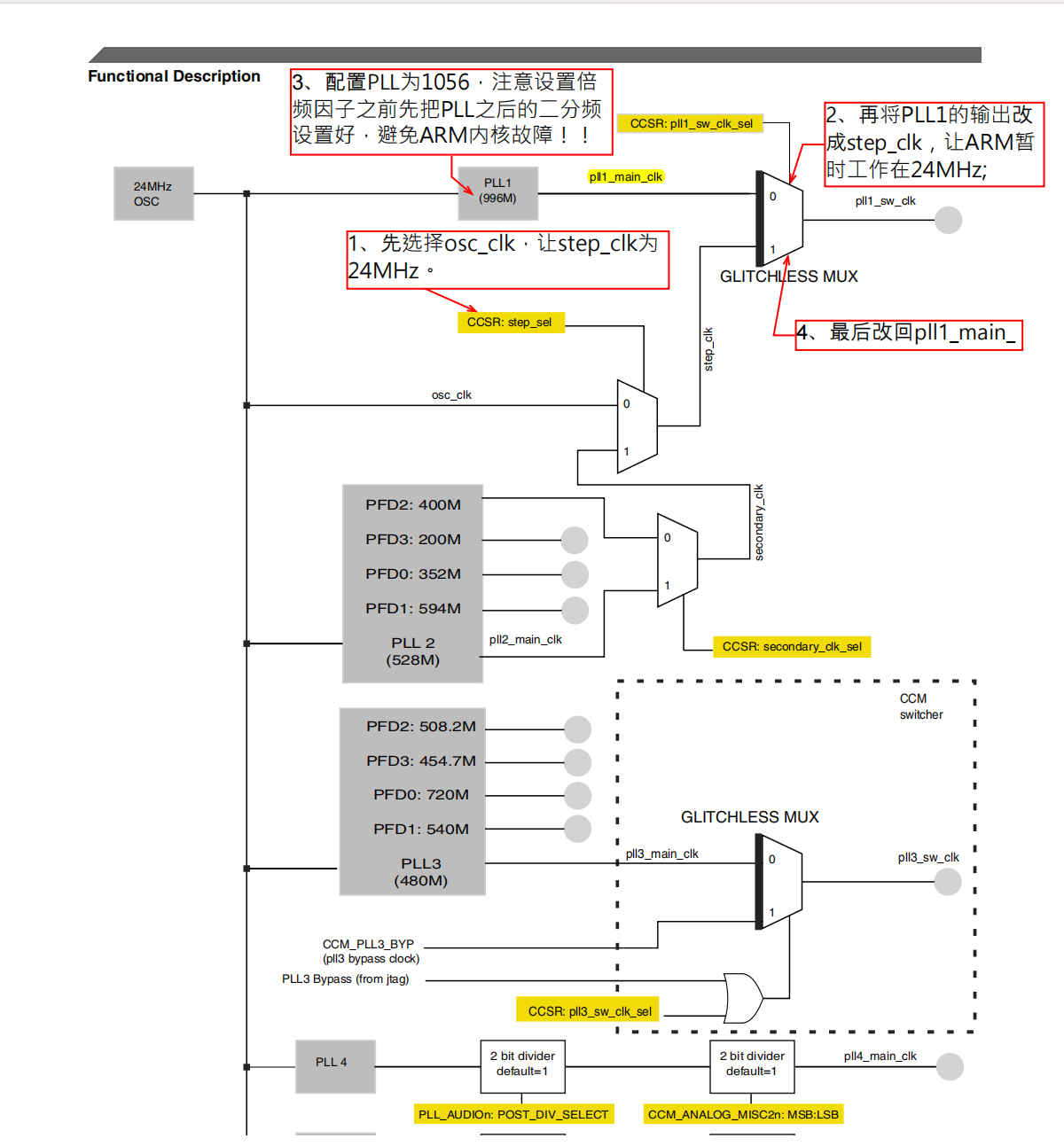

(1) 配置PLL1、PLL2、PLL3

(2)、配置時鐘生成樹CLOCK ROOT GENERATOR

(3)驗證配置(使用EPIT外設)

6.EPIT設置步驟

三、GPT通用目的寄存器

輸入捕獲,輸出比較

IMX6U有兩個GPT,全稱為 General Purpose Timer(通用目的的定時器)。GPT 定時器是一個 32 位向上定時器(也就是從 0X00000000 開始向上遞增計數),GPT 定時器也可以跟一個值進行比較,當計數器值和這個值相等的話就發生比較事件,產生比較中斷。GPT 定時器有一個 12 位的分頻器,可以對 GPT 定時器的時鐘源進行分頻。

GPT主要使用最主要的寄存器是GPT Control Register (GPTx_CR)寄存器主要的域有:? SWR(bit15):復位 GPT 定時器,向此位寫 1 就可以復位 GPT 定時器,當 GPT 復位完成以后此為會 自動清零。? FRR(bit9):運行模式選擇,當此位為 0 的時候比較通道 1 工作在重新啟動(restart)模式。當此位為 1的時候所有的三個比較通道均工作在自由運行模式(free-run)。? CLKSRC(bit8:6):GPT 定時器時鐘源選擇位,為 0 的時候關閉時鐘源;為 1 的時候選擇ipg_clk 作為時鐘源;為 2 的時候選擇 ipg_clk_highfreq 為時鐘源;為 3 的時候選擇外部時鐘為時鐘源;為 4 的時候選擇 ipg_clk_32k 為時鐘源;為 5 的時候選擇 ip_clk_24M 為時鐘源。我們選擇 ipg_clk 作為 GPT定時器的時鐘源,因此此位設置位 1(0b001)。? ENMOD(bit1):GPT 使能模式,此位為 0 的時候如果關閉 GPT 定時器,計數器寄存器保存定時器關閉時候的計數值。此位為 1 的時候如果關閉 GPT 定時器,計數器寄存器就會清零。? EN(bit):GPT 使能位,為 1 的時候使能 GPT 定時器,為 0 的時候關閉 GPT 定時器。GPT Prescaler Register (GPTx_PR)用于保存分頻值,PRESCALER(bit11:0),這就是 12 位分頻值,可設置 0~4095,分別對應 1~4096 分頻

)

(文件系統路由、服務端渲染SSR、靜態生成SSG、增量靜態再生ISR、API路由))

high 調優一例(二))