目錄

1. 簡介

1.1 硬件平臺

1.2 圖片

2. 硬件信息

2.1 Vivado Basic

2.1.1 GPIO

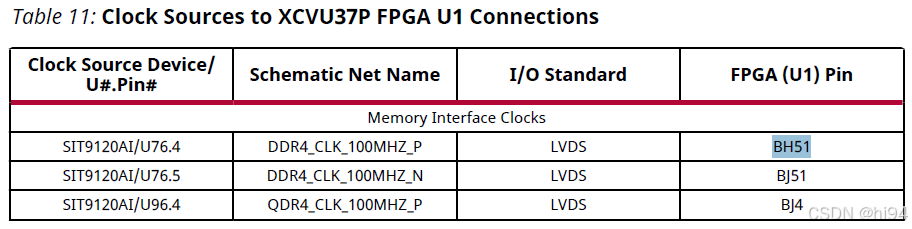

2.1.2 Clock Sources

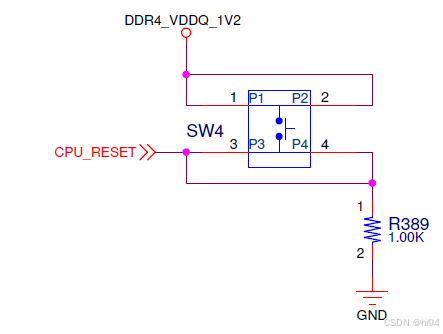

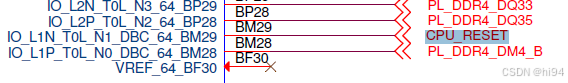

2.1.3 Reset

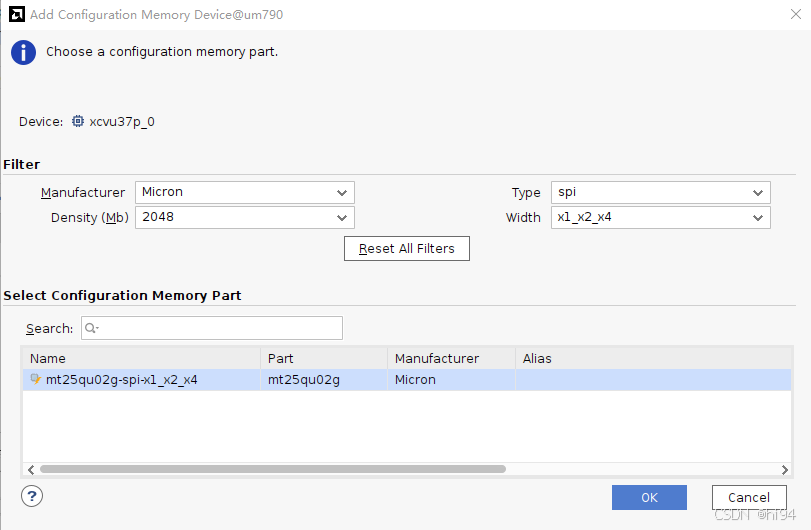

2.1.4 Flash

2.1.5 燒寫報錯

2.2 PCIe simple

2.2.1 Block Design

2.2.2 XDMA

2.3 PCIe HBM

2.3.1 Block Design

2.3.2 HBM IP

3. HBM 知識

3.1 交叉開關

3.2?Throughput

3.3 Global Addressing

3.4 時鐘

3.5?Packaging and Pinouts

4. 總結

1. 簡介

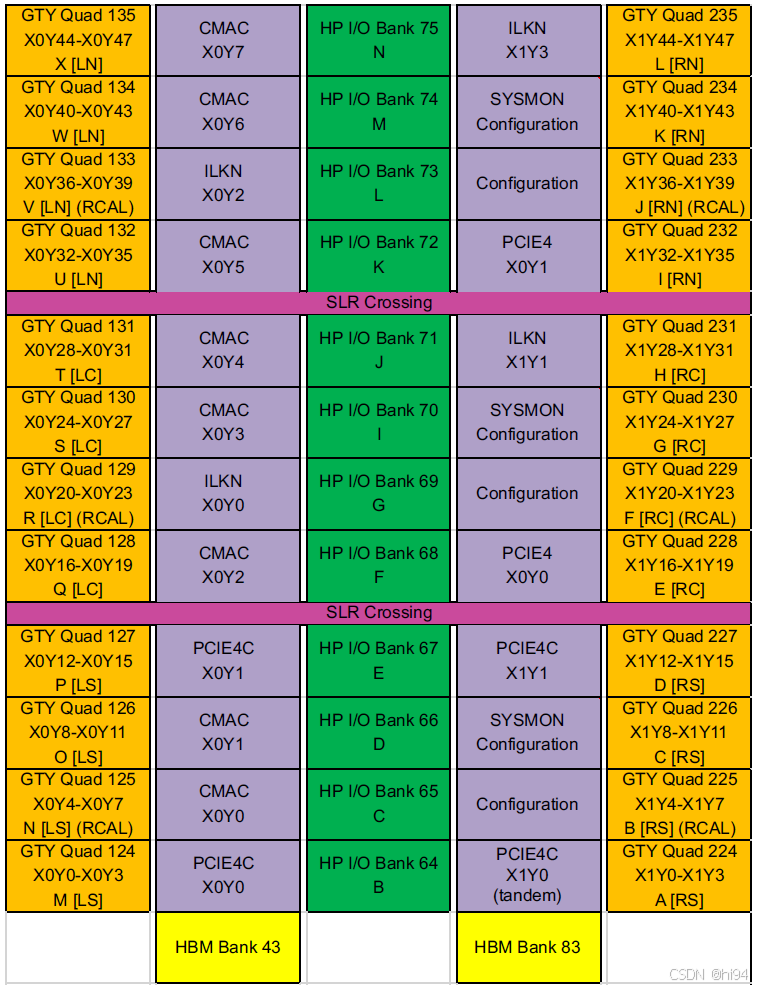

1.1 硬件平臺

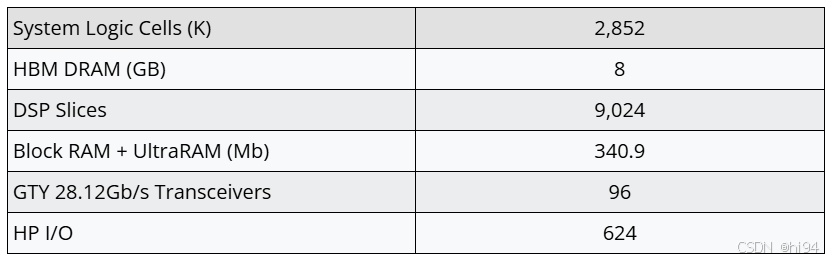

Virtex UltraScale+ VU37P HBM FPGA:XCVU37P-2FSVH2892E

AMD Virtex? UltraScale+? HBM VCU128 FPGA Evaluation KitThe VCU128 board incorporates the all new AMD Virtex? UltraScale+? VU37P HBM FPGA that integrates 8GB of HBM DRAM adjacent to FPGA die to enable massive memory bandwidth and much smaller PCB footprint. Virtex UltraScale+ HBM FPGAs alleviate bandwidth bottlenecks and power consumption associated with using parallel memories, like DDR4, in compute, database, and network acceleration applications.The VCU128 evaluation kit is optimized for quickly prototyping applications using Virtex UltraScale+ HBM FPGAs.![]() https://www.amd.com/en/products/adaptive-socs-and-fpgas/evaluation-boards/vcu128.html

https://www.amd.com/en/products/adaptive-socs-and-fpgas/evaluation-boards/vcu128.html

XCVU37P HBM Feature:

- 集成 8GB HBM,460GB/s 帶寬

- HBM 子系統的最大理論帶寬為 460 GB/S,可實現帶寬為 420 GB/s(~90% 效率)

靈活的連接性,適用于廣泛的應用:

- 四個 28.12Gb/s QSFP28 接口

- PCIe?Gen3 x16 和 Gen4 x8

- VITA 57.4 FMC+ 接口

- 10/100/1000Mb/s 以太網

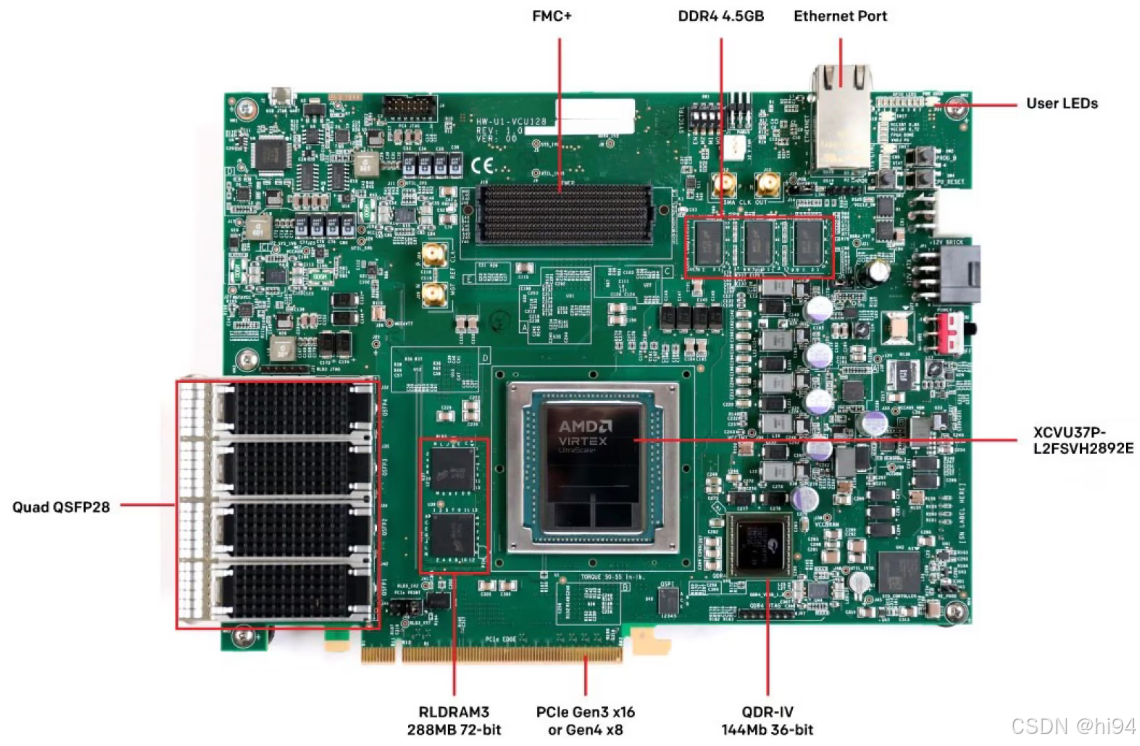

1.2 圖片

2. 硬件信息

2.1 Vivado Basic

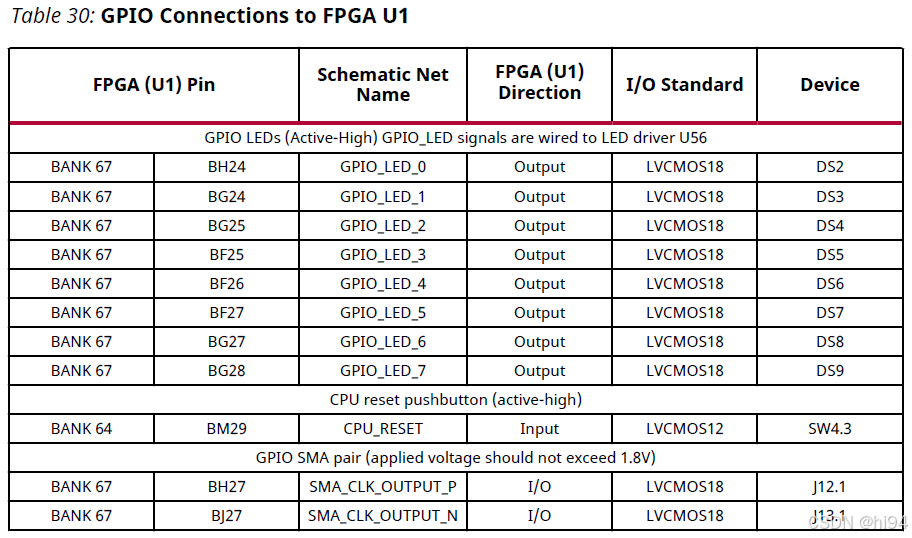

2.1.1 GPIO

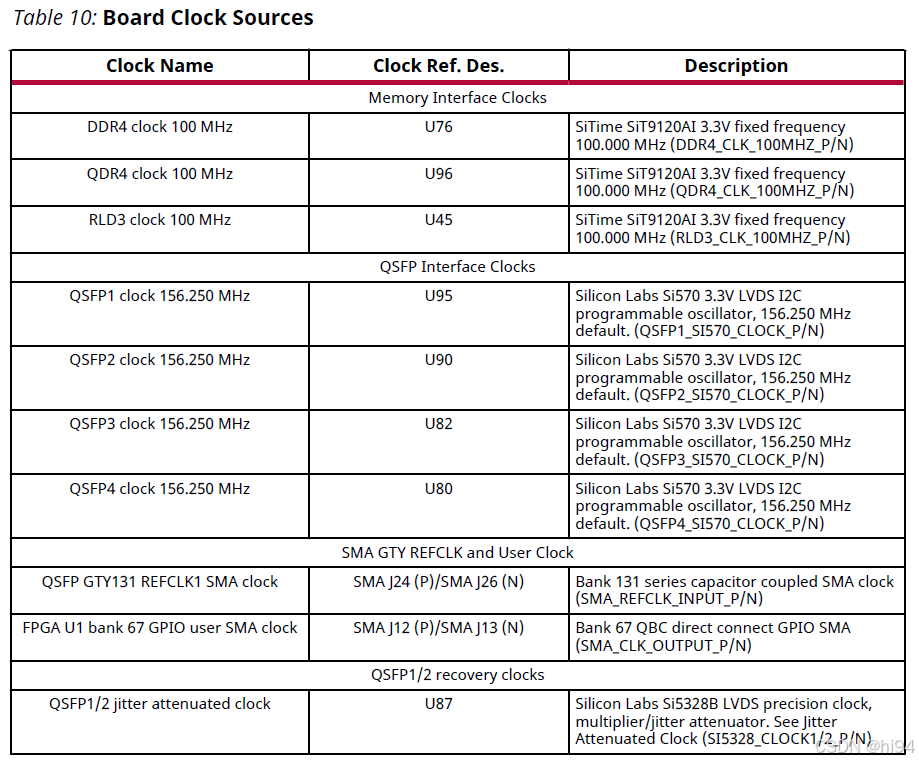

2.1.2 Clock Sources

2.1.3 Reset

SW4 - CPU_RESET - PIN: BM29,?LVCMOS12, Active High

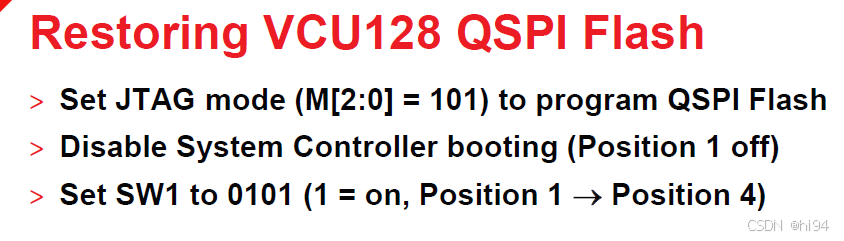

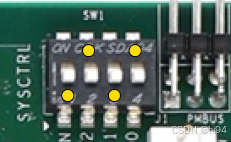

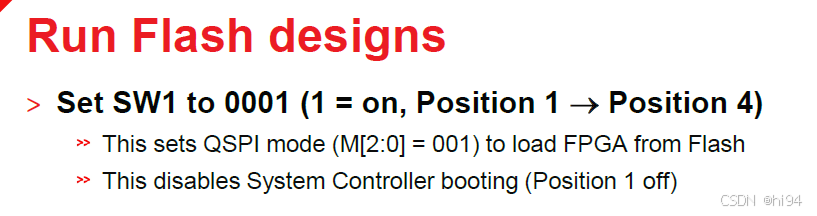

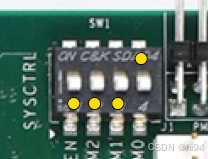

2.1.4 Flash

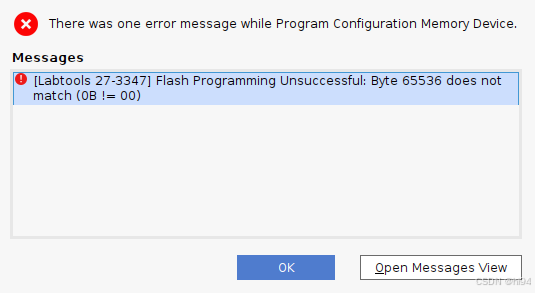

2.1.5 燒寫報錯

?[Labtools 27-3347] Flash Programming Unsuccessful: Byte 65536 does not match (0B != 00)

設置的速率過高導致的:

set_property PARAM.FREQUENCY 15000000 [get_hw_targets */xilinx_tcf/*/*]

如果設置為 30000000 則會出錯。

2.2 PCIe simple

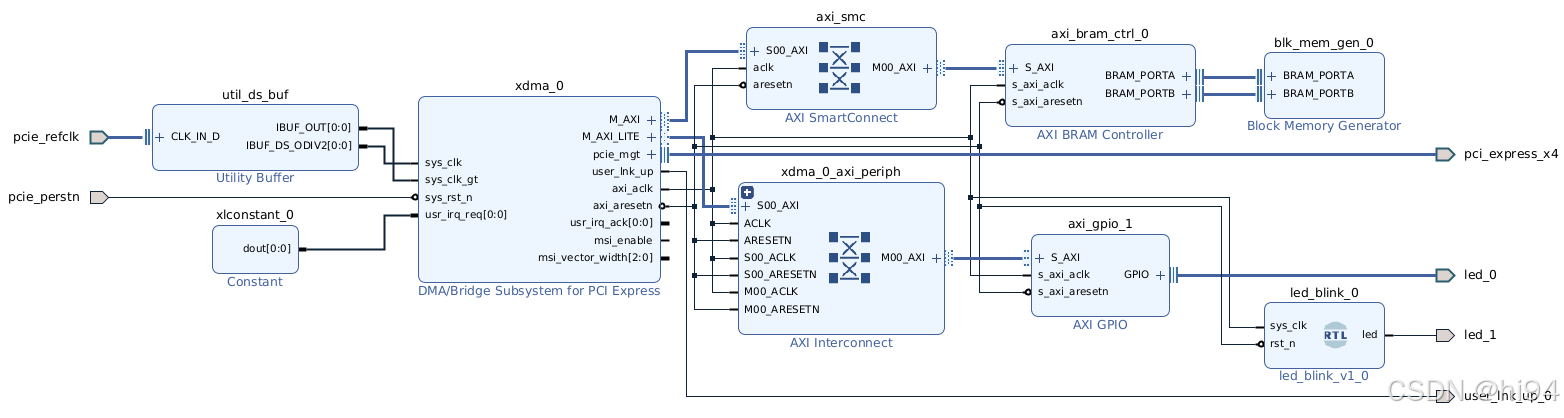

2.2.1 Block Design

XDC

set_property PACKAGE_PIN BG28 [get_ports user_lnk_up_0]

set_property IOSTANDARD LVCMOS18 [get_ports user_lnk_up_0]set_property PACKAGE_PIN BH24 [get_ports {led_0_tri_o[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {led_0_tri_o[0]}]set_property PACKAGE_PIN BG24 [get_ports led_1]

set_property IOSTANDARD LVCMOS18 [get_ports led_1]set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 51.0 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]2.2.2 XDMA

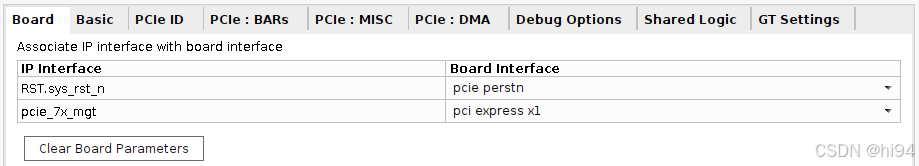

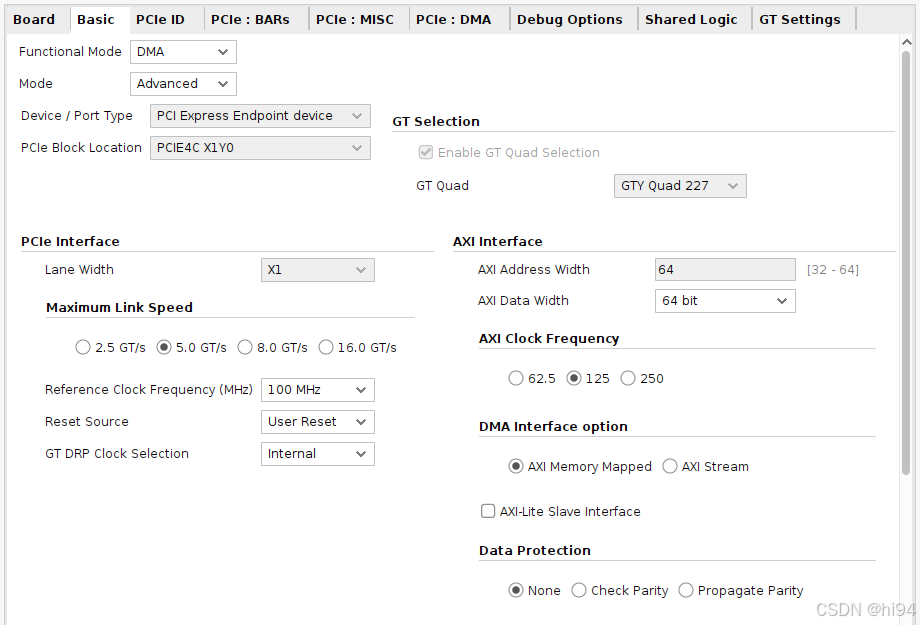

1)Board

2)Basic

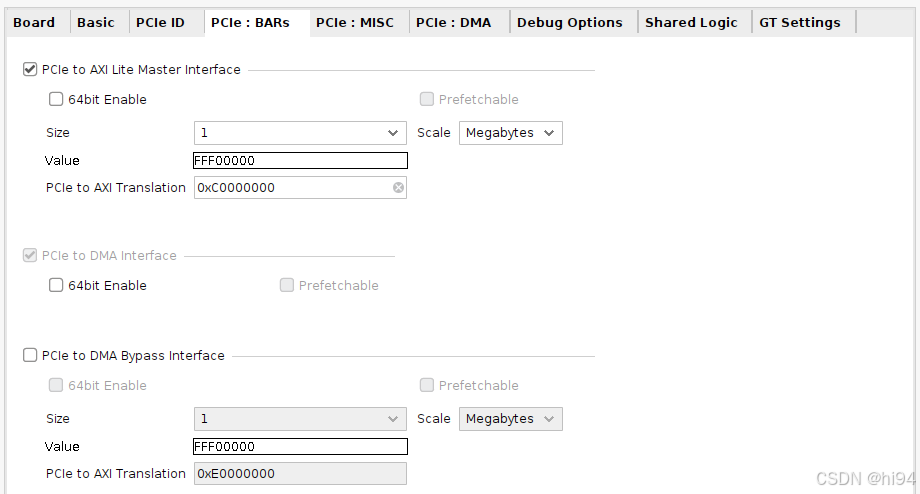

3)PCIe Bars

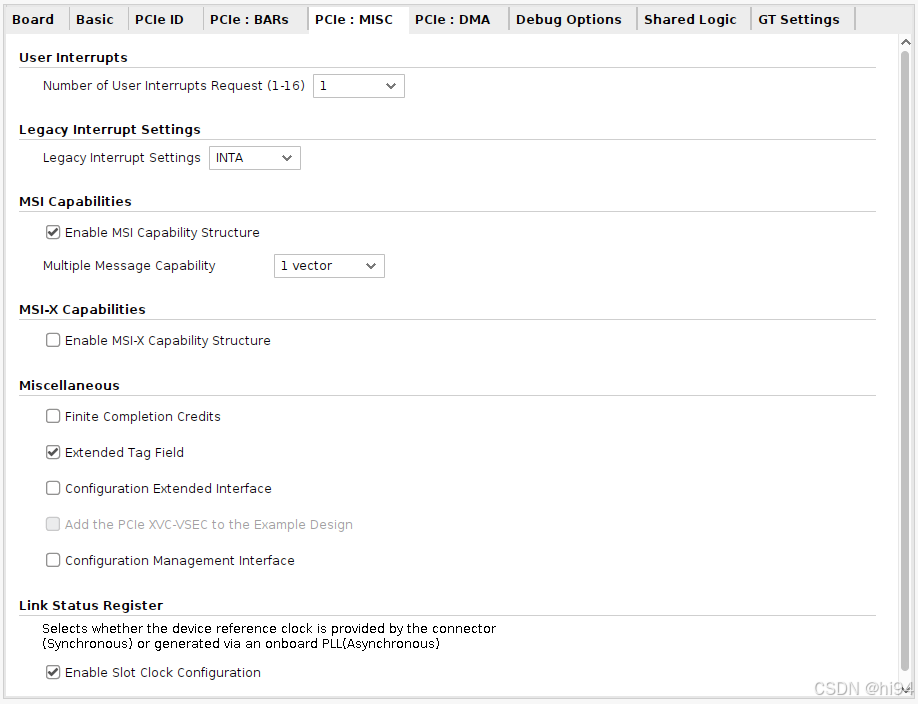

4)MISC

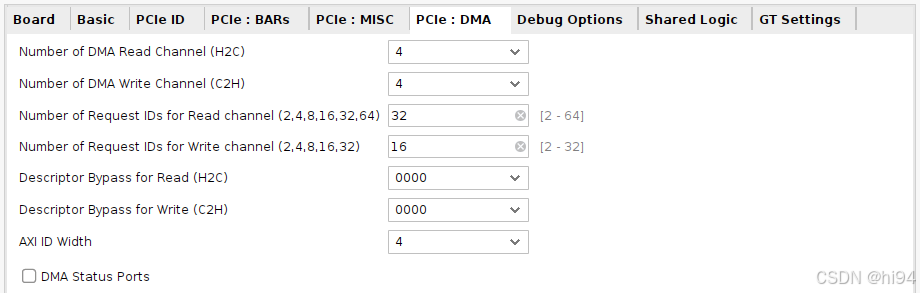

5)PCIe DMA

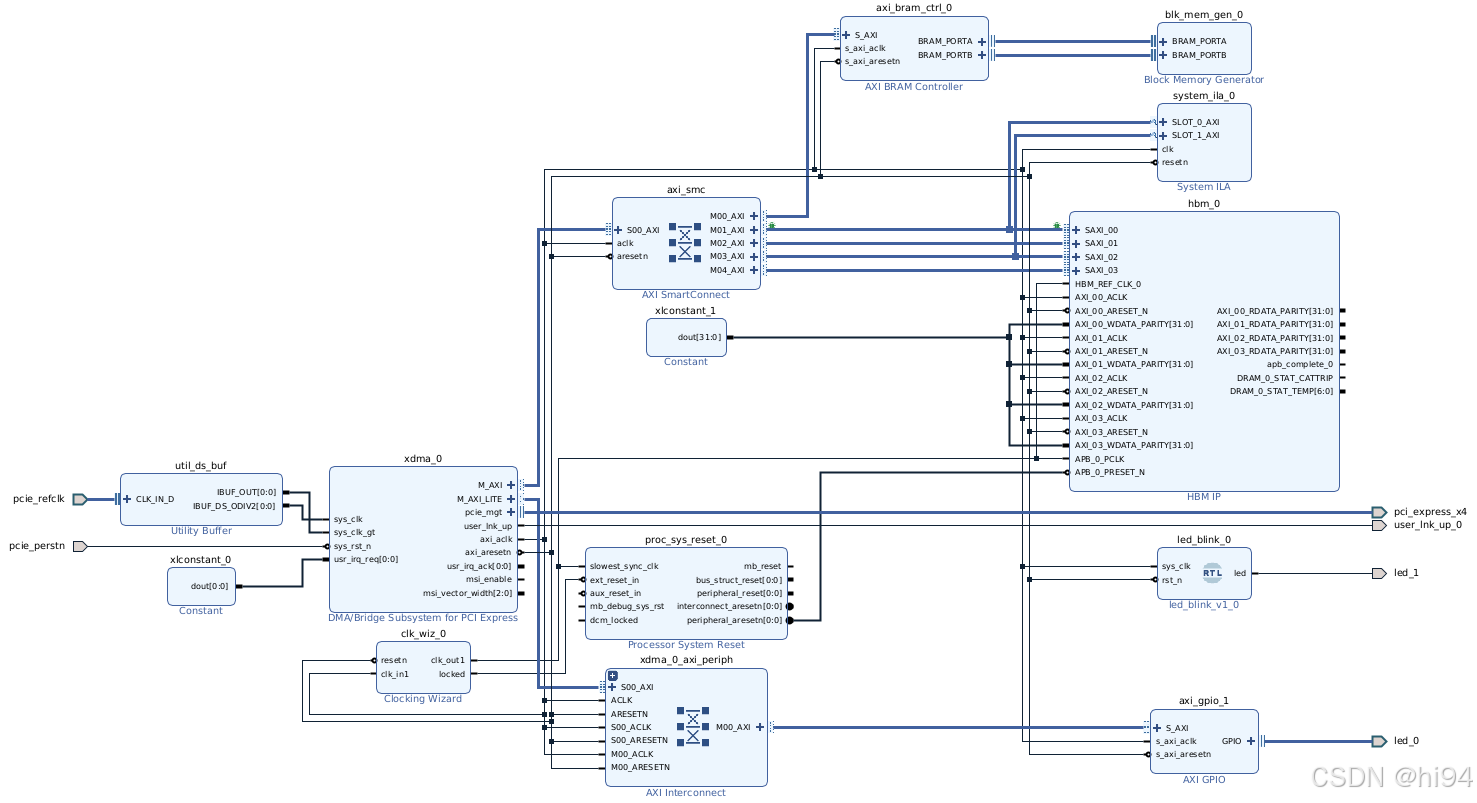

2.3 PCIe HBM

2.3.1 Block Design

XDC:

set_property PACKAGE_PIN BG28 [get_ports user_lnk_up_0]

set_property IOSTANDARD LVCMOS18 [get_ports user_lnk_up_0]set_property PACKAGE_PIN BG24 [get_ports led_1]

set_property IOSTANDARD LVCMOS18 [get_ports led_1]set_property PACKAGE_PIN BH24 [get_ports {led_0_tri_o[0]}]

set_property IOSTANDARD LVCMOS18 [get_ports {led_0_tri_o[0]}]set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 51.0 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]set_property C_USER_SCAN_CHAIN 1 [get_debug_cores dbg_hub]

connect_debug_port dbg_hub/clk [get_nets */clk_wiz_0_clk_out1]2.3.2 HBM IP

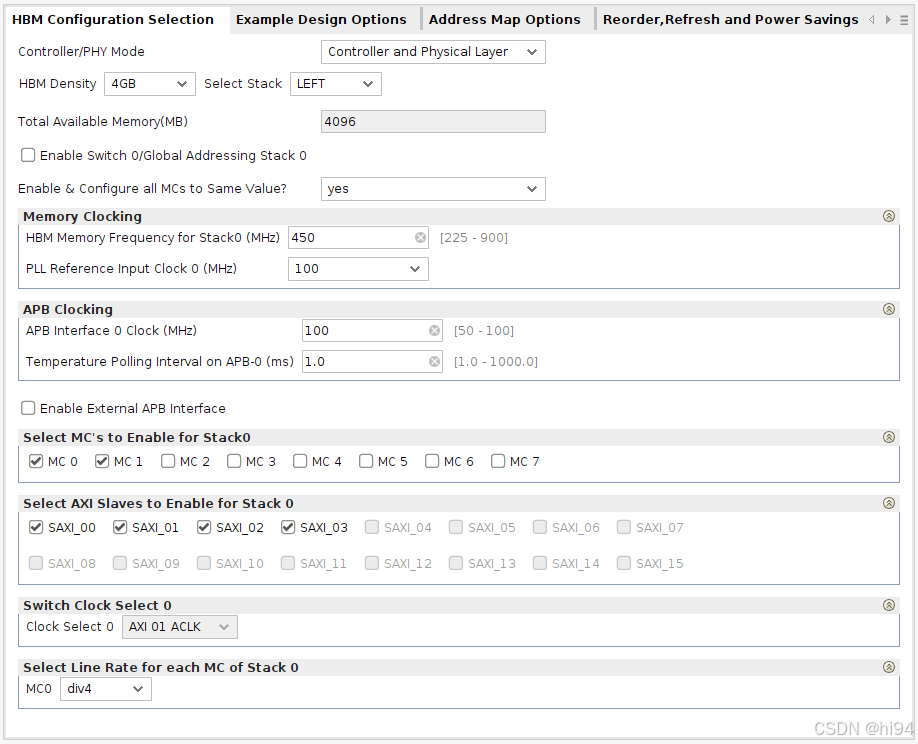

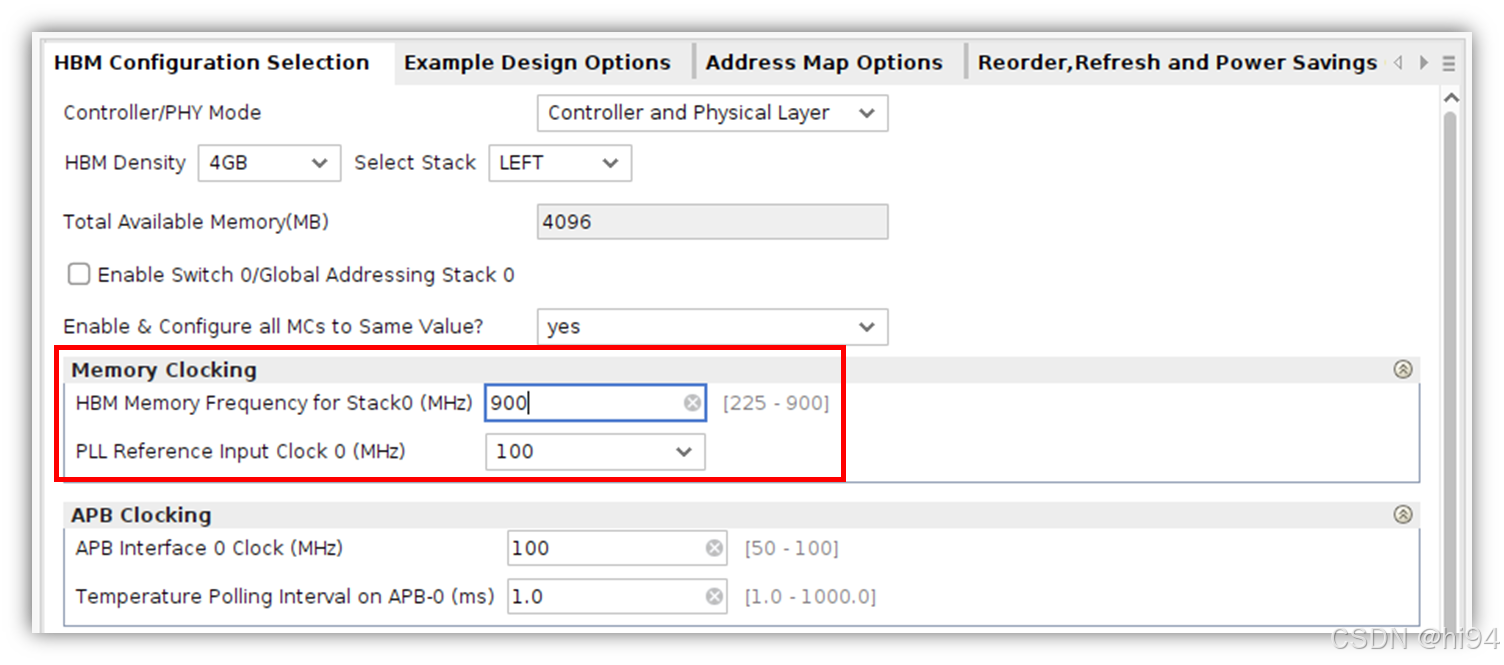

1)HBM Configuration Selection Tab

- Enable Switch / Global Addressing Stack

是否啟用全局尋址功能。選擇此選項允許全局尋址的靈活性,但會增加延遲。

- Enable External APB Interface

啟用外部 APB 接口以寫入/讀取文檔中記錄的控制器狀態和性能寄存器。

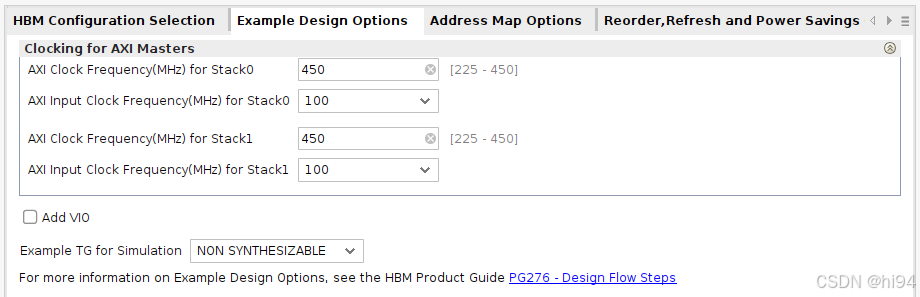

2)Example Design Options Tab

生成示例設計時所使用的時鐘配置。

在示例設計的頂層文件中,每個 Stack 實例化一個 MMCM 來生成 AXI 時鐘。

- AXI Clock Frequency(MHz) for Stackx 指定 MMCM 輸出時鐘頻率。

- AXI Input?Clock Frequency(MHz) for Stackx 指定 MMCM 的輸入時鐘頻率。?

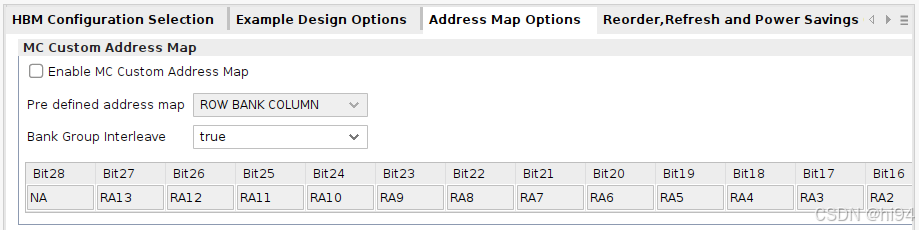

3)Address Map Options

- Address Map Options

如果遇到性能瓶頸,可以通過 ILA 監控內存訪問模式,進一步優化地址映射。

DDR 內存的地址由 Bank、Row、Column 組成。Address Map Options 允許用戶調整這些地址位的排列順序,以優化內存訪問的并行性和減少 Bank 沖突。如果多個請求訪問同一Bank的不同Row,會導致額外的預充電和激活延遲(tRP + tRCD)。合理的地址映射可以分散訪問,減少此類沖突。

Row-Bank-Column (RBC):適用于大多數標準應用,提供均衡的性能。

Bank-Row-Column (BRC):適用于高帶寬需求,可以減少 Bank 沖突,但可能增加 Row 切換的開銷。

- Bank Group Interleave

啟用此功能可使順序地址操作在偶數與奇數存儲體組之間交替執行,從而最大化內存效率。但需注意,隨機訪問模式可能無法從此設置中獲益。

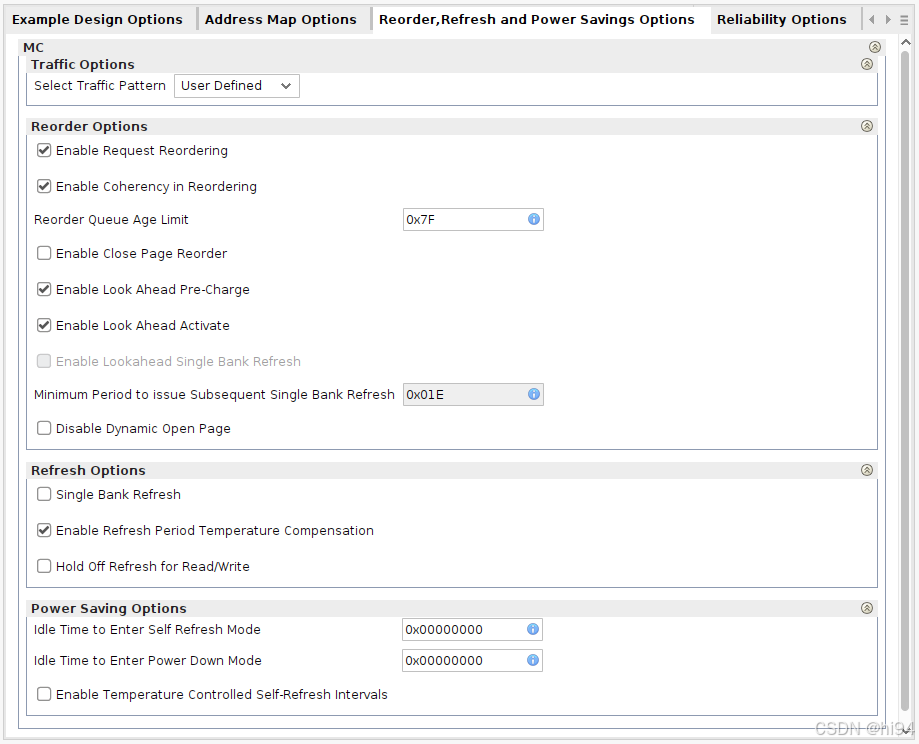

4)Reorder, Refresh, and Power Savings Options

Reorder Options:通過智能調整命令順序(如重排、預充電、頁管理)最大化吞吐量。

- 命令重排序:在64深度的窗口內重新排列命令(如讀寫順序),減少存儲體(Bank)沖突和行(Row)切換延遲。

- 動態頁管理:控制存儲頁(Page)的關閉/保持開放,平衡延遲與吞吐量。

- 預充電與激活優化:提前規劃預充電(Pre-Charge)和激活(Activate)命令,減少空閑周期。

- 刷新插入策略:結合待處理操作智能插入刷新命令,降低性能影響。

Refresh Options:優化刷新策略(如單 Bank 刷新、溫度適應)以兼顧數據可靠性和性能。

- 單存儲體刷新(Single Bank Refresh):逐個Bank刷新(而非全Bank同時刷新),減少訪問阻塞。

- 溫度補償刷新:高溫時自動提高刷新頻率(高溫下 DRAM 數據易丟失)。

- 讀寫優先:允許延遲刷新以優先處理讀寫請求,但需后續補償更多刷新。

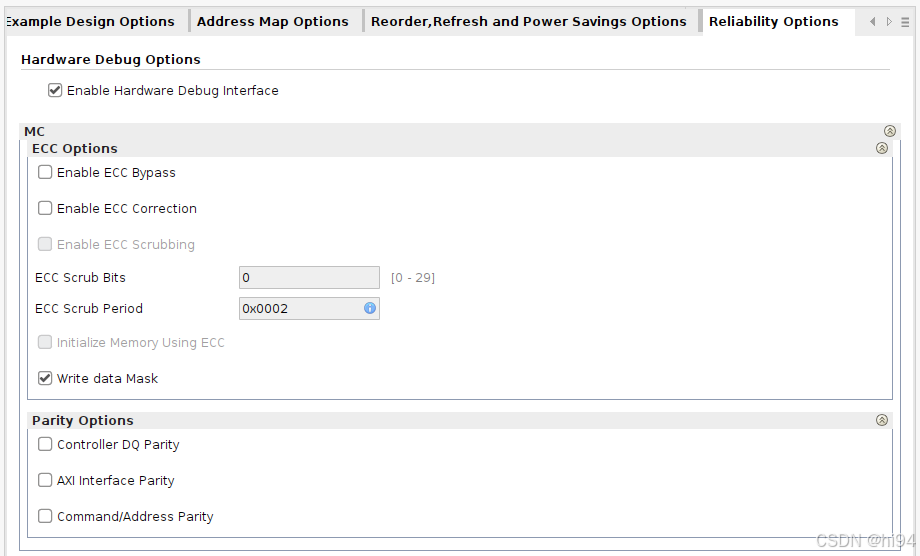

5)Reliability Options

- 1)Enable ECC Bypass(啟用ECC旁路)

- 功能:禁用ECC計算和校正功能。

- 行為:

- wdata_parity輸入引腳改為直接寫入ECC存儲器的數據。

- rdata_parity輸出改為從ECC存儲器讀取的原始數據。

- 副作用:

- 自動禁用寫數據掩碼(Write Data Mask)功能。

- 非對齊事務會觸發讀-修改-寫操作。

- 2)Enable ECC Correction(啟用ECC校正)

- 功能:啟用單比特錯誤校正和雙比特錯誤檢測。

- 行為:

- 檢測到錯誤時會記錄在狀態寄存器中。

- 是其他高級ECC功能(如擦洗)的基礎。

- 3)Enable ECC Scrubbing(啟用ECC擦洗)

- 前提:必須啟用ECC Correction。

- 功能:持續后臺掃描內存,主動修復單比特錯誤。

- 優勢:防止錯誤累積導致不可修復的雙比特錯誤。

- 4)ECC Scrub Bits(擦洗地址位寬)

- 定義:用于擦洗操作的內存地址位數。

- 默認值(0):自動使用當前內存配置支持的最大位寬。

- 5)ECC Scrub Period(擦洗周期)

- 單位:256個內存時鐘周期。

- 示例:值為2表示每512個周期(2×256)執行一次擦洗讀取。

- 6)Initialize Memory Using ECC(ECC初始化內存)

- 前提:必須啟用ECC Correction。

- 功能:在初始化時用有效ECC值填充整個內存陣列。

- 用途:確保未寫入區域也有合法ECC數據。

- 7)Write Data Mask(寫數據掩碼)

- 兼容性:與ECC Correction/Bypass互斥。

- 功能:允許部分寫入(掩碼指定哪些字節被寫入)。

3. HBM 知識

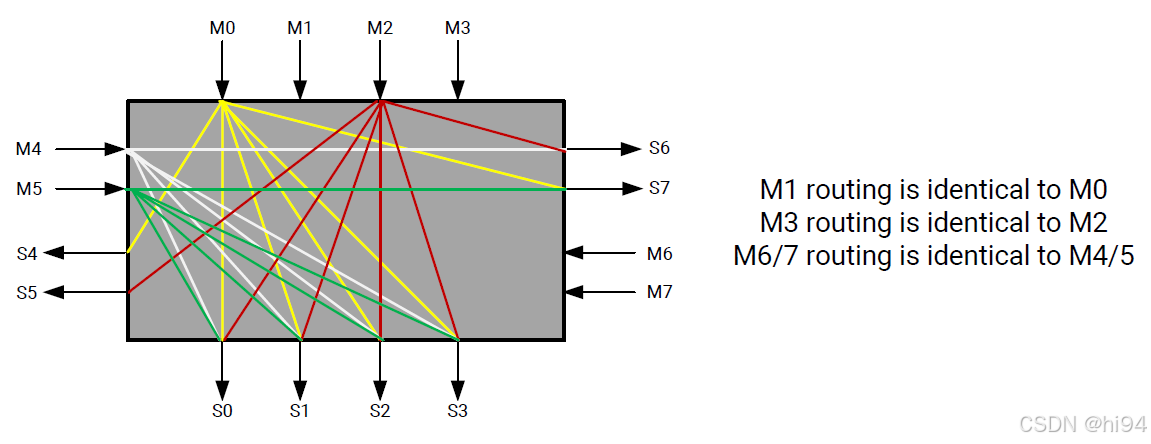

3.1 交叉開關

分段交叉開關可能會成為瓶頸,影響應用程序的實際 HBM 性能。

如上圖所示:

最快的連接是從 AXI 通道到對齊的偽通道(PC)內存地址,M0→S0(0-256 MB),M1→S1(256-512 MB),等等。這將限制設計只能訪問 32 個獨立的 256 MB 段 PC。為了性能權衡,分段交叉開關允許任何 AXI 主設備訪問 8 GB HBM 范圍內的任何地址。這與 DDR 配置不同,如果 AXI 主設備端口連接到 DDR0,那么只能訪問 DDR0 內的地址。對于 HBM,如果地址不在對齊的偽通道(PC)內,那么它將通過上述的本地 4x4 連接性或通過 L/R 連接上的另一個 4x4 開關來穿越分段交叉開關到達正確的 PC。當你指示工具將一個主 AXI 接口連接到多個 PC 時,有一個內部機制使用特定內核主設備的內存規范。

性能會受到兩個因素的影響:

- 開關中的每個連接具有相同的帶寬。

- 從 4x4 開關到另一個 4x4 開關的穿越會增加延遲。

3.2?Throughput

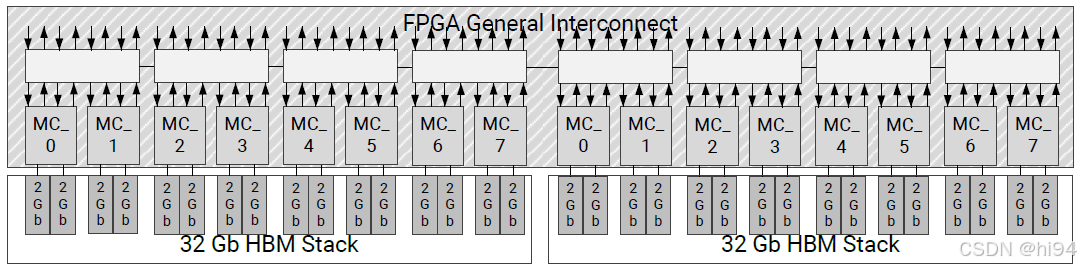

1)從內存控制器的角度

- 每個 HBM stack 包含八個 MC,每個 MC 包含兩個 PC(Pseudo Channels)。

- PC 位寬為 64 bit,且數據信號以 IP 配置中 HBM 時鐘頻率的雙倍速率切換(DDR)。

- 若配置的時鐘頻率為 900 MHz,則 HBM stack 的切換速率可通過以下公式計算:

( 64 bit / PC ) × ( 2 ch / MC ) × ( 8 MC ) × 900 MHz × 2 = 1,843,200 Mb/s = 230,400 MB/s

對于雙堆棧器件,該值翻倍至?460,800 MB/s。

2)從用戶邏輯角度

- HBM 的每個 AXI 端口寬度為 256 位,每個 PC 對應一個 AXI 端口。

- 當 HBM 運行于 900 MHz,用戶邏輯 AXI 時鐘為 450 MHz 以實現速率匹配。

- 計算公式如下:

( 256 bit / AXI ) × ( 2 ch / MC ) × ( 8 MC ) × 450 MHz =?1,843,200 Mb/s = 230,400 MB/s

對于配置 32 個 AXI 端口的雙堆棧器件,該值翻倍至?460,800 MB/s。

3)效率損耗

上述為 HBM 理論 Throughput,但與所有傳統 DDR 器件類似,HBM stack 中的存儲陣列需通過刷新維持數據完整性:

- HBM 的基礎刷新間隔(tREFI)為 3.9 us。

- 4H 器件的刷新命令周期(tRFC)為 260 ns,8H 器件則為 350 ns。

- 考慮刷新開銷后,4H 器件的峰值效率將損失約 7%,8H 器件約損失 9%。

與傳統 DDR 存儲器相同,tREFI 會隨溫度升高而縮短:

- 當堆棧溫度上升時,刷新操作會占用更多 HBM 接口時間(效率降低)。

- 0°C 至 85°C 時,tREFI 為 3.9 us。

- 85°C 至 95°C 時,tREFI 將縮減至 1.95 us。

PS:4H Device (4 GB per Stack),8H Device (8 GB per Stack)

3.3 Global Addressing

訪問方式上,有 2 種方式,global 模式和非 global 模式,在非 global 模式下,每個用戶通過偽隨機通道只能訪問對應的 256MB 空間;global 模式下,每個偽隨機通道可以訪問整個 HBM 空間。

性能上,每個 AXI 用戶接口(偽隨機通道)的數據位寬為 256bit,最高工作頻率為 450M,所以每個用戶接口的最大性能為:256bit*450M = 14400MB/s。在 global 模式下,通過一個偽隨機通道,訪問其他的控制器對應的存儲空間,性能會降低,具體見 PG276 上的說明。

根據xilinx提供的文檔 pg276,HBM 單個 stack 的理論最大性能為:(256 bits per AXI port) x (2 ports per memory controller) x (8 channels) x 450 MHz = 230400MB/s,整體性能為 460800MB/s。

3.4 時鐘

必須提供給HBM核心的三種時鐘類型包括:

- HBM_REF_CLK_x:驅動鎖相環(PLL),生成八個內存控制器的時鐘以及HBM堆棧的內存時鐘。每個 HBM 堆棧對應一個 PLL。此時鐘必須源自 MMCM/BUFG 或 BUFG,也可由其他時鐘的級聯時鐘源派生,但其原始時鐘必須來自與 HBM 同一 SLR 內的 GCIO 引腳。驅動 GCIO 的時鐘發生器抖動需小于3皮秒均方根值(3 pS RMS)。

- APB_x_PCLK:用于 APB 寄存器端口訪問,可與其他時鐘異步。每個 HBM 堆棧有一個 APB 時鐘端口,可源自級聯時鐘源、MMCM 或 GCIO 引腳。

- AXI_xx_ACLK:每個 AXI 端口的時鐘,可與其他時鐘異步,時鐘源可以是級聯時鐘源、MMCM 或 GCIO 引腳。

全局路由交換機無獨立時鐘輸入,而是共享某個 AXI_xx_ACLK 時鐘。軟件會自動選擇用戶所選內存控制器中位于中間的一個時鐘(通過查看 hbm_0.v 文件中的 CLK_SEL_xx 參數可確認,僅一個參數標記為 TRUE)。

為實現最佳性能,所選的 AXI 時鐘應為所有 AXI 端口時鐘中頻率最高的一個。

3.5?Packaging and Pinouts

《UG575,UltraScale and UltraScale+ FPGAs Packaging and Pinouts》

4. 總結

以上是使用 HBM 的基本操作,后續補充:

- HBM 帶寬監控

- DDR 性能優化

)

)

》)