🌈個人主頁:慢了半拍

🔥 創作專欄:《史上最強算法分析》?|?《無味生》?|《史上最強C語言講解》?|?《史上最強C練習解析》|《史上最強C++講解》|《史上最強計組》|《史上最強數據結構》

🏆我的格言:一切只是時間問題。?

?

?

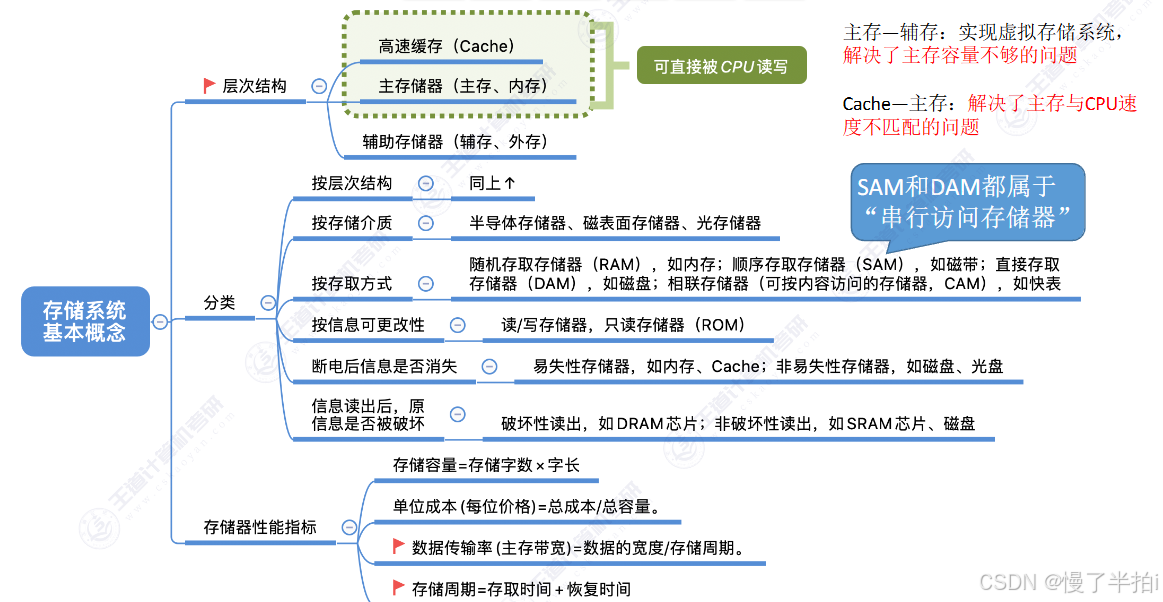

一、存儲器概念

1.1 存儲器的分類

可按照不同分類方式進行分類

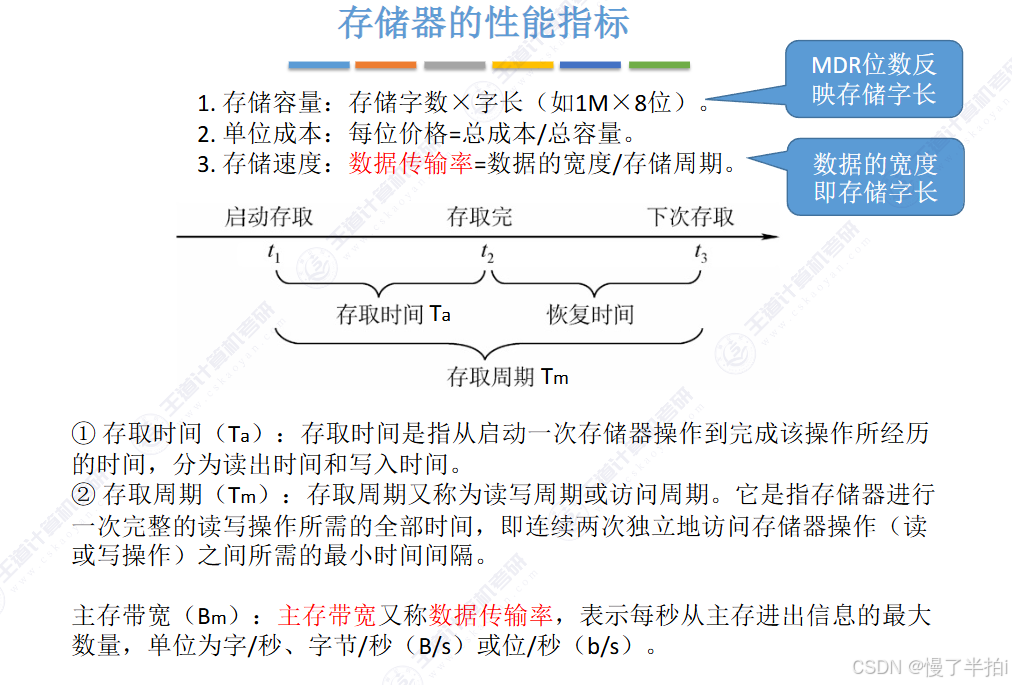

1.2 存儲器的性能指標

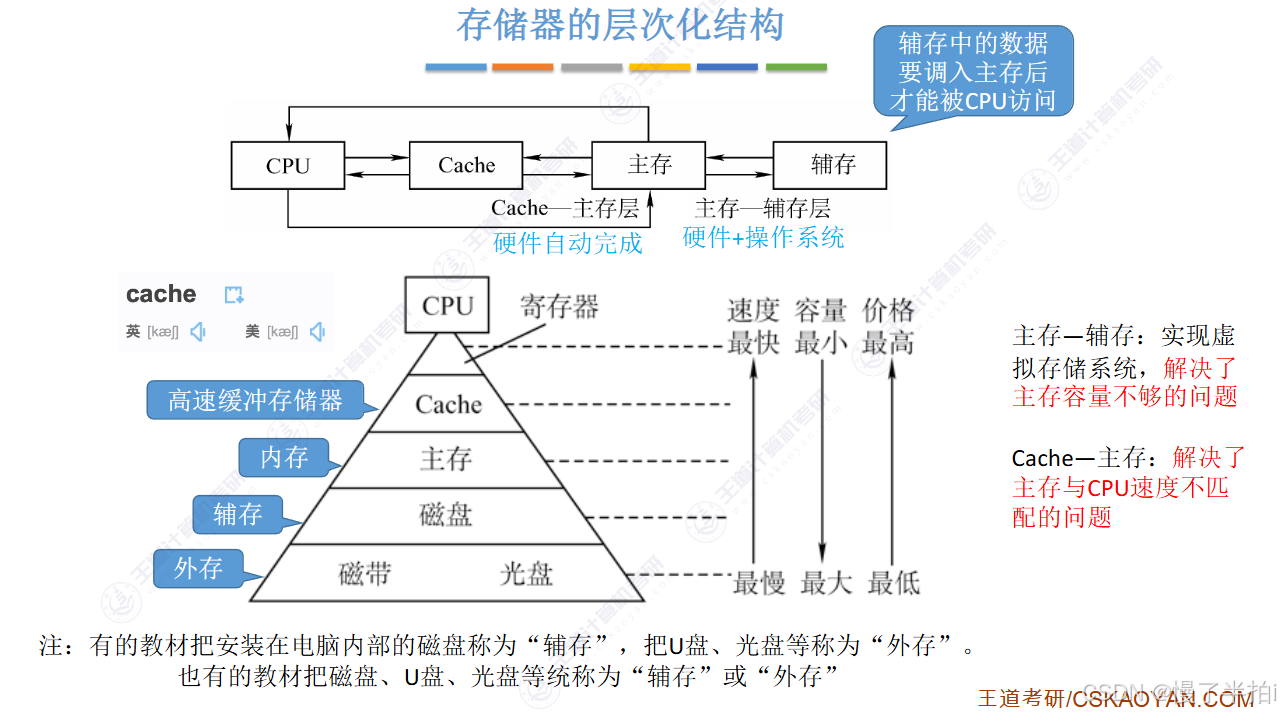

1.3 多級層次的存儲系統

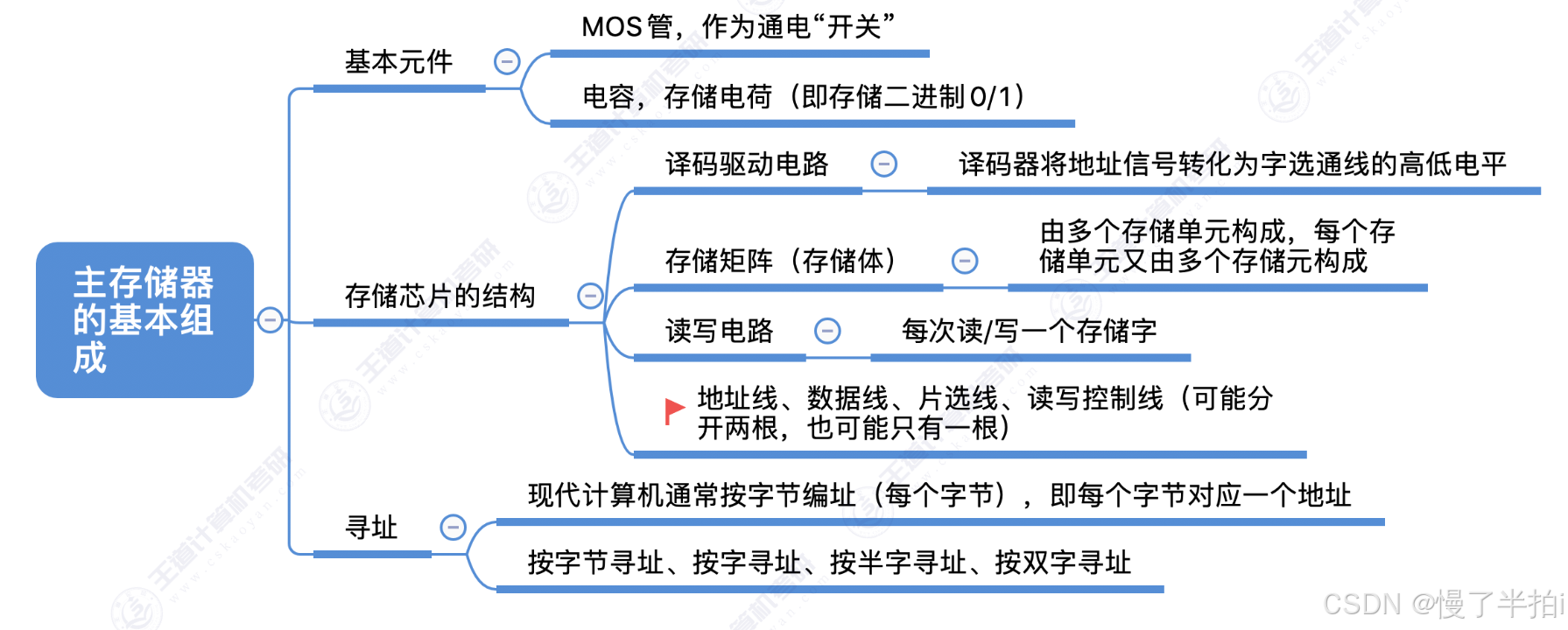

二、主存儲器

2.1?主存儲器的基本組成?

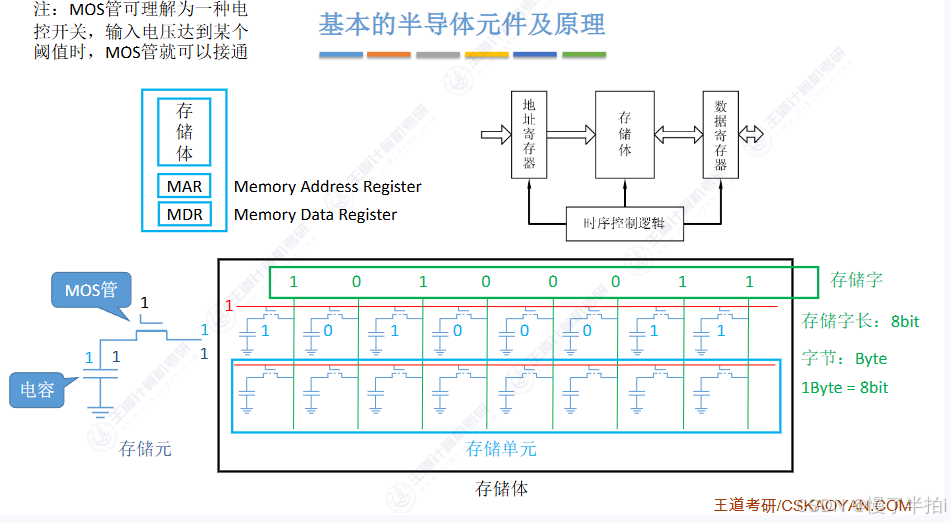

1.半導體基本原理

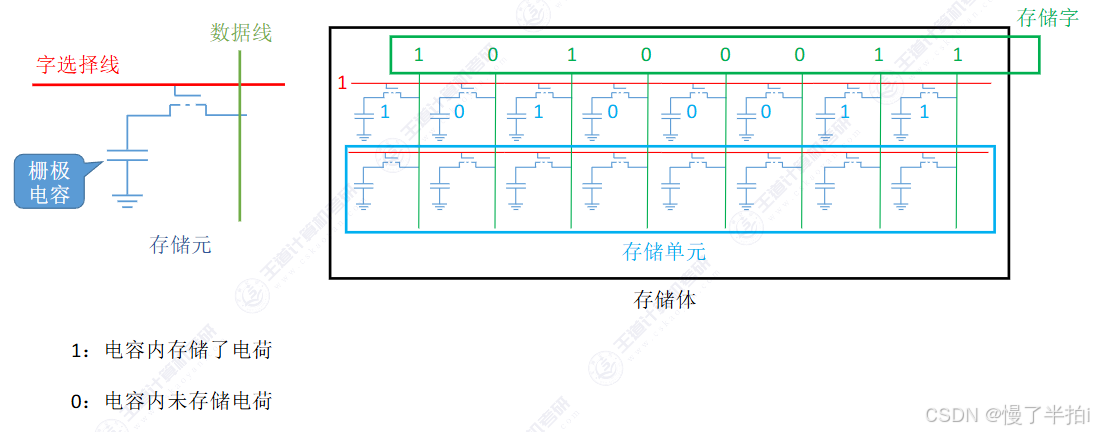

1)存儲體的構成

- 三大部分: 主存儲器邏輯上可分為存儲體、MAR(地址寄存器)和MDR(數據寄存器)三大部分

- 層級關系: 存儲體由多個存儲單元構成,每個存儲單元又由多個存儲元(存儲元件)構成

- 最小單位: 一個存儲元件可存放一位二進制數據(0或1)

2)半導體元件介紹:MOS管

- 工作原理: 用電控制的開關,當控制端電壓達到閾值(如5V)時導通,否則絕緣

- 半導體特性: 既不是導體也不是絕緣體,電壓條件滿足時變為導體

- 圖示說明: 控制端加高電平畫實線表示導通,低電平畫虛線表示絕緣

3)半導體元件介紹:電容

- 結構組成: 由兩塊金屬板和中間絕緣體構成,下板接地(0V)

- 充電原理: 上板加高電平(如5V)時產生電壓差,電荷移動形成充電

- 數據表示: 充電狀態表示二進制1,未充電表示二進制0

4)二進制數據的讀取原理

- 讀取過程:

- 給MOS管控制端加高電平使其導通

- 若電容有電荷(表示1),電荷流出產生可檢測電流

- 若電容無電荷(表示0),無電流輸出

-

檢測方式: 通過監測輸出線是否有電流判斷存儲的是0還是1

5)二進制數據的寫入原理

- 寫入1:

- 數據線加高電平(5V)

- MOS管控制端加高電平使其導通

- 電容上板電壓5V,下板0V,產生充電

- MOS管斷開后電荷保留

- 寫入0: 數據線加低電平(0V或1V),電壓差不足不充電

6)存儲單元與存儲體的概念

- 存儲單元: 一行連接的存儲元件構成一個存儲單元(存儲字)

- 存儲體: 多個存儲單元構成存儲體(存儲矩陣)

- 字長說明: 存儲字長取決于每行存儲元件數量(如8個存儲元件=8位字長)

- 重要區別: 字節固定8位,存儲字長由具體存儲體結構決定

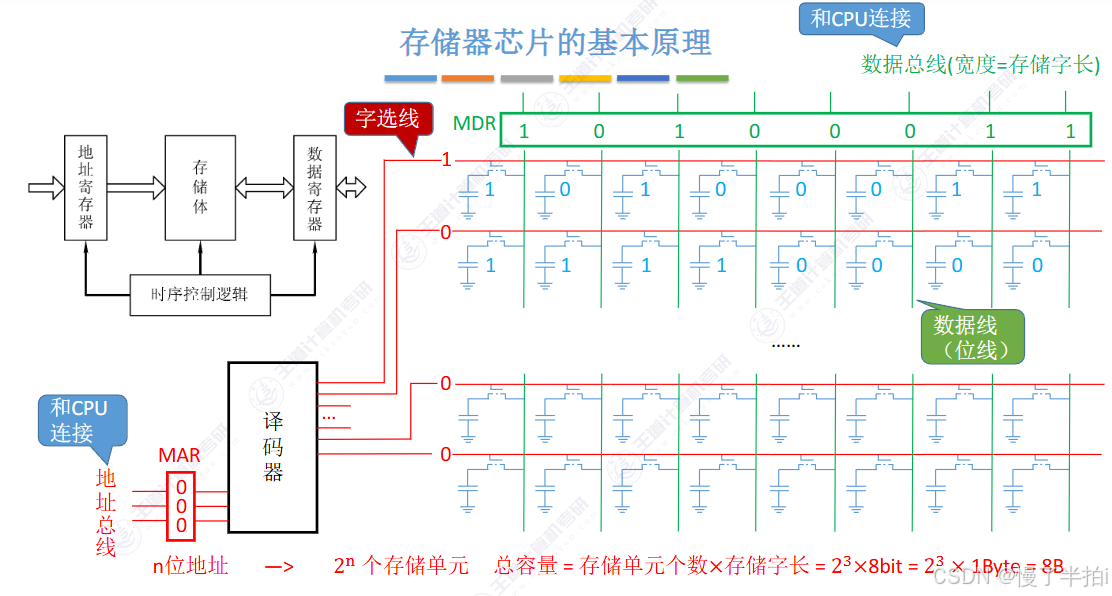

2.存儲芯片的基本原理

- 地址譯碼: n位地址對應?2^n?個存儲單元,譯碼器將地址轉換為某條選通線的高電平

- 讀取過程示例: 地址000對應第0根選擇線,選中第一個存儲字的所有存儲元件

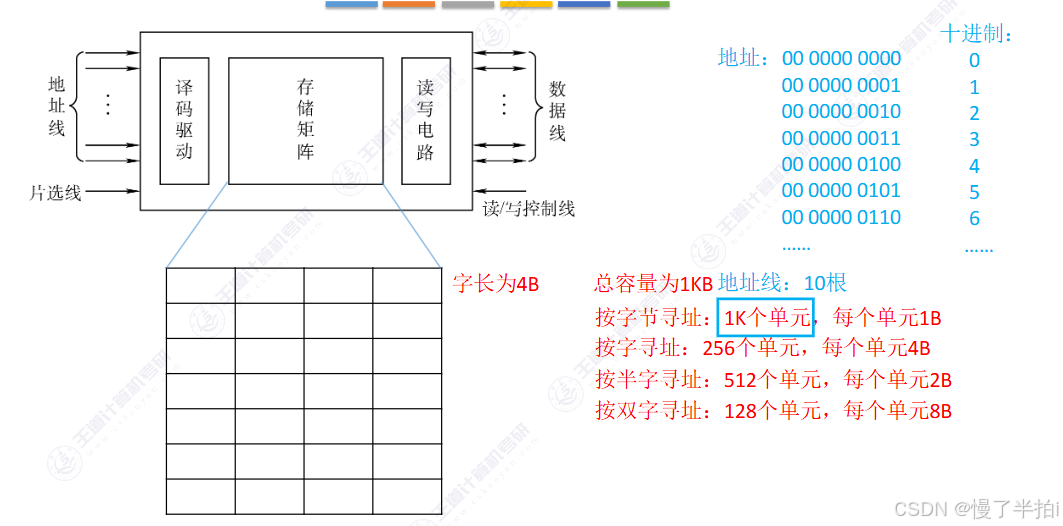

1)存儲芯片的邏輯構成

- 核心部件:

- 存儲矩陣(存儲體)

- 譯碼驅動電路(含譯碼器和驅動器)

- 讀寫電路(含控制電路)

- 外部接口:

- 地址線(接收CPU地址)

- 數據線(傳輸數據)

- 片選線(確定芯片是否可用)

- 讀寫控制線(控制讀寫操作)

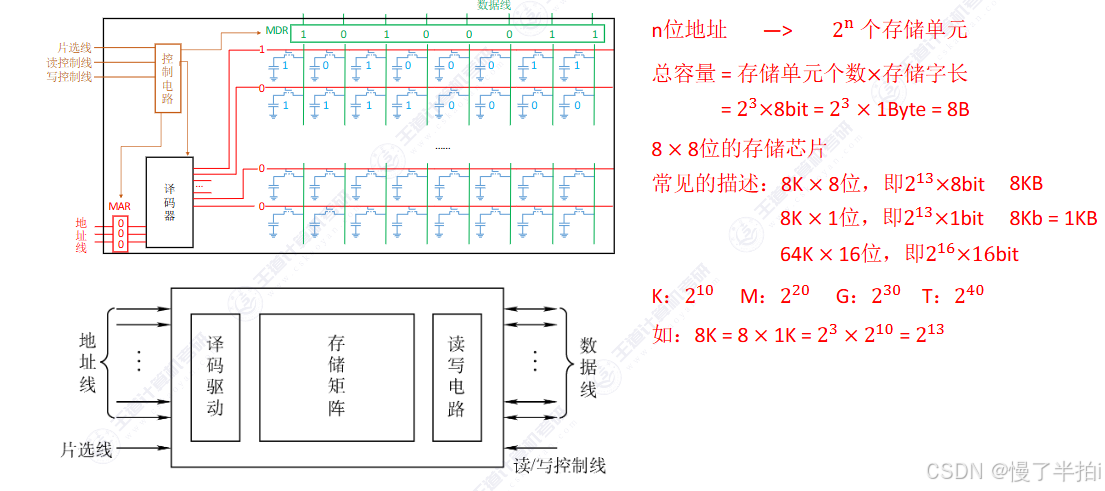

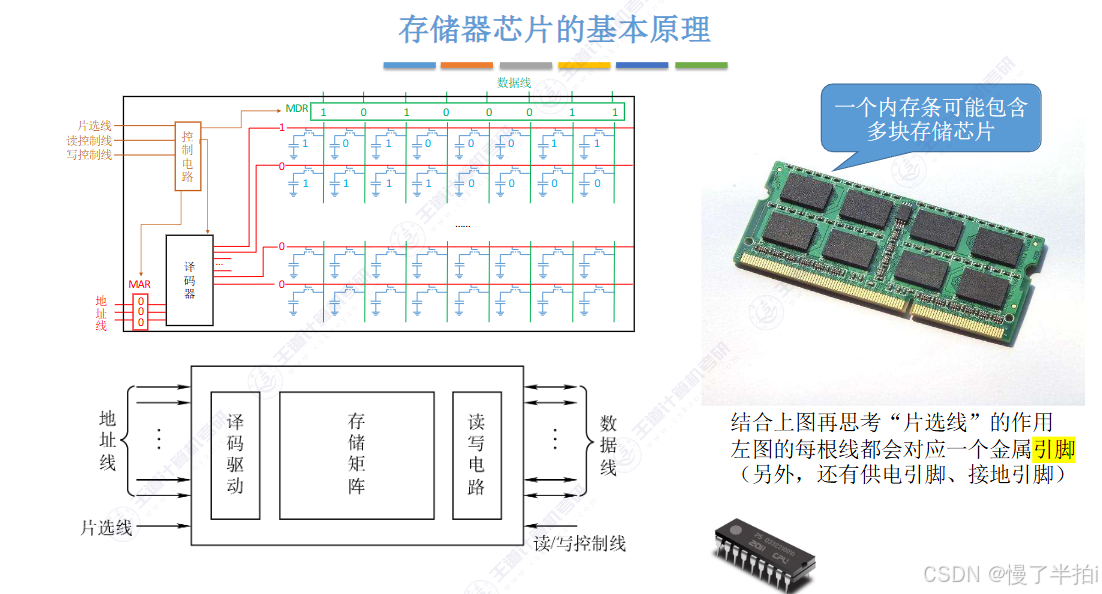

2)存儲芯片的物理構成

- 片選信號作用: 在多芯片系統中選擇特定芯片工作(低電平有效)

- 引腳計算:

- 地址線數量=地址位數

- 數據線數量=存儲字長位數

- 必選引腳: 片選線+讀寫控制線(1或2根)

- 容量表示: 采用"存儲單元數×存儲字長"格式(如8K×8位表示8K單元,每單元8位)

- 實際應用: 內存條由多塊存儲芯片組成,總容量為各芯片容量之和

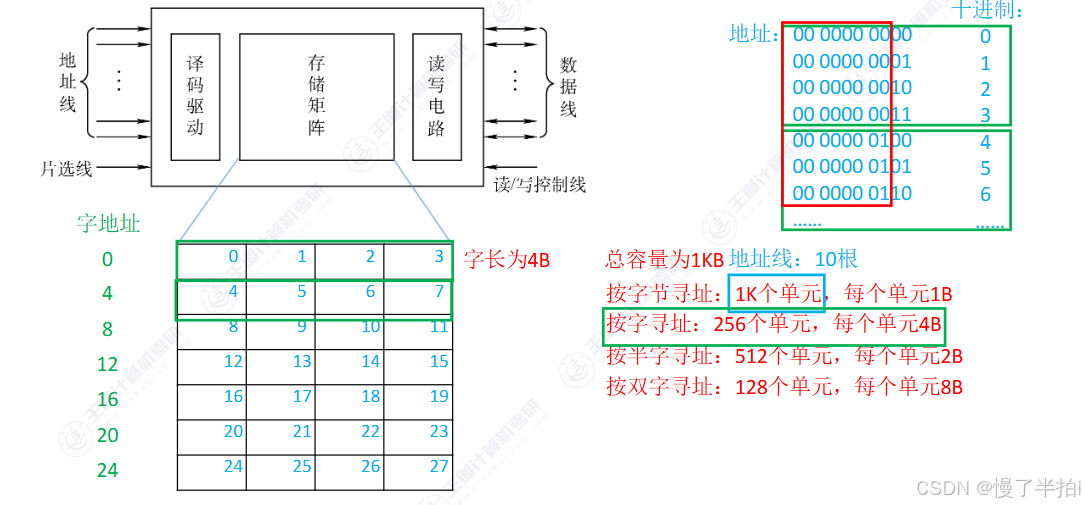

3.如何實現不同的尋址方式

1)存儲芯片的基本結構

- 核心組件:由地址線、譯碼驅動電路、存儲矩陣、讀寫電路、數據線、片選線和讀/寫控制線組成

- 存儲單元:圖示中的小方格表示1個字節(8比特),一整行表示1個存儲字(示例中字長為4字節)

- 容量計算:示例芯片總容量為1KB(256個字×4字節),對應需要10根地址線(210=10242^{10}=1024210=1024)

2)編址方式

- 字節編址

- 基本規則:現代計算機按字節編址,每個字節對應唯一地址(示例中地址范圍0-1023)

- 地址分配:連續分配地址,如0號字節、1號字節...1023號字節

- 其他編址方式

- 字尋址:1個字=4字節,字地址左移2位得起始字節地址(如1號字→二進制1左移2位=4)

- 半字尋址:1個半字=2字節,地址轉換需左移1位

- 雙字尋址:1個雙字=8字節,地址轉換需左移3位

- 單元數量:1KB存儲器的尋址單元數分別為:字節尋址1024個、字尋址256個、半字尋址512個、雙字尋址128個

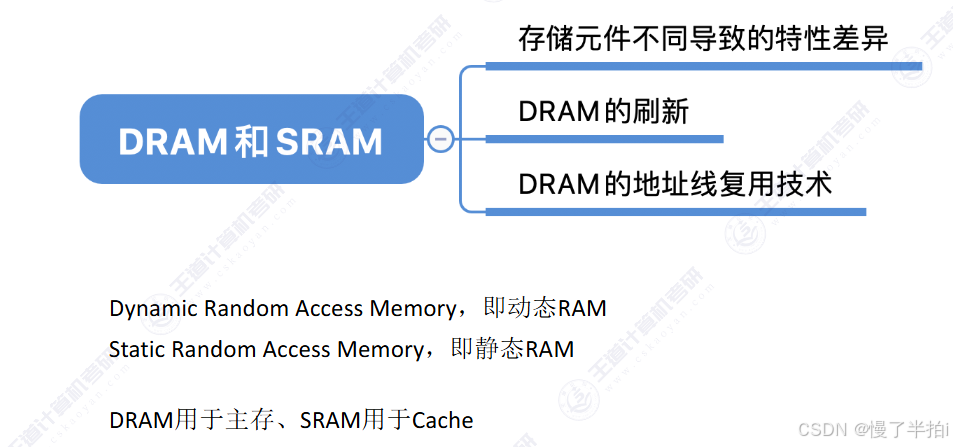

2.2?SRAM 芯片和 DRAM 芯片

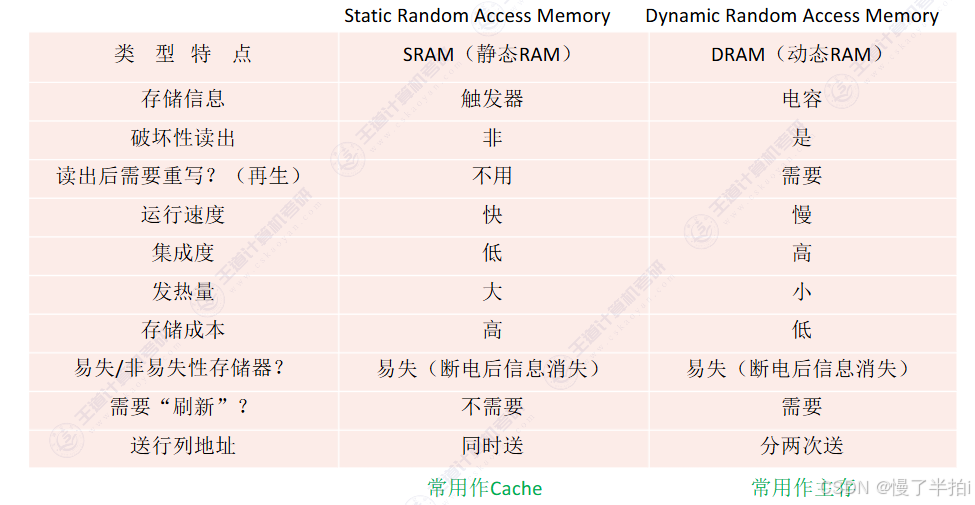

1.SRAM與DRAM基本概念

- RAM定義: 隨機訪問存儲器(Random Access Memory)的特點是存儲單元讀取速度不隨物理位置改變

- DRAM全稱: Dynamic Random Access Memory(動態隨機存取存儲器)

- SRAM全稱: Static Random Access Memory(靜態隨機存取存儲器)

- 典型應用:

- DRAM用于制造主存

- SRAM用于制造Cache(高速緩沖存儲器)

- 高頻考點: 兩種存儲芯片的特性對比是考試重點

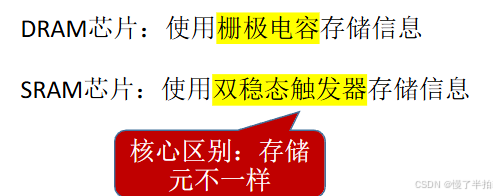

2.存儲元件差異

- DRAM存儲原理:? 使用電容的充放電來存儲信息? ? ?需要定期刷新保持數據

- SRAM存儲原理:? 使用雙穩態觸發器存儲信息? ? ?不需要刷新操作

- 核心區別: 兩種芯片的存儲元件物理特性不同導致其他特性差異

3.DRAM與SRAM對比

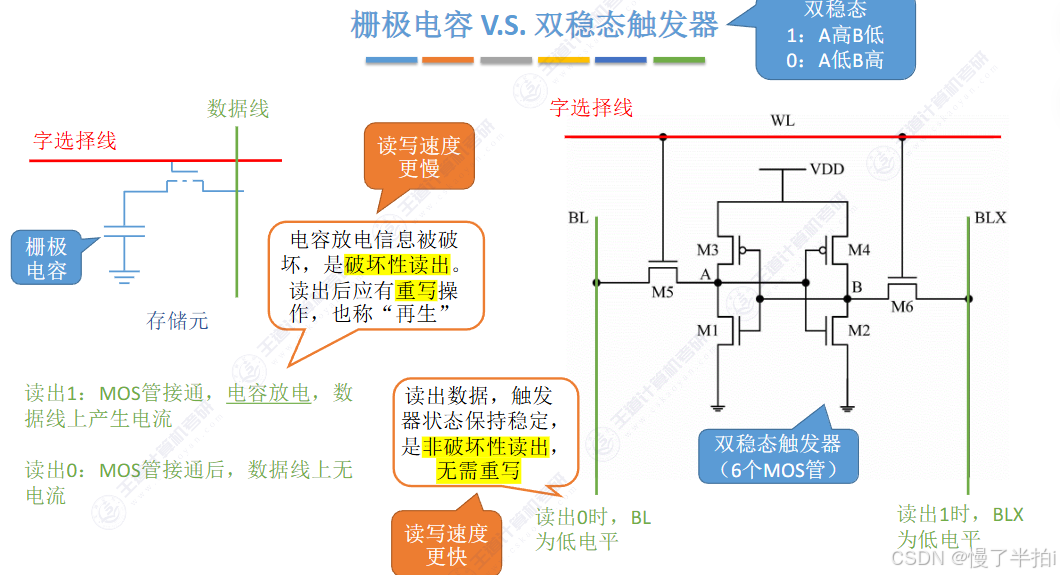

- DRAM存儲原理

- 存儲機制:通過柵極電容存儲電荷表示二進制信息,

1對應電容存儲電荷(5V高電平),0對應無電荷(0V低電平)

- 寫入操作:字選擇線加5V高電平使MOS管導通,數據線輸入5V(寫1)或0V(寫0)決定電容是否存儲電荷

- 電荷分布:寫1時上金屬板聚集正電荷(5V),下金屬板接地(0V)形成壓差;寫0時兩極板無壓差

- 存儲機制:通過柵極電容存儲電荷表示二進制信息,

- SRAM存儲原理

- 存儲機制:采用6個MOS管構成雙穩態觸發器,1對應A點高電平/B點低電平,0對應A點低電平/B點高電平

- 讀出操作:

- 讀1時BLX輸出低電平? ? ?讀0時BL輸出低電平

- 寫入操作:

- 寫0:BL加低電平,BLX加高電平? ? ?寫1:BL加高電平,BLX加低電平

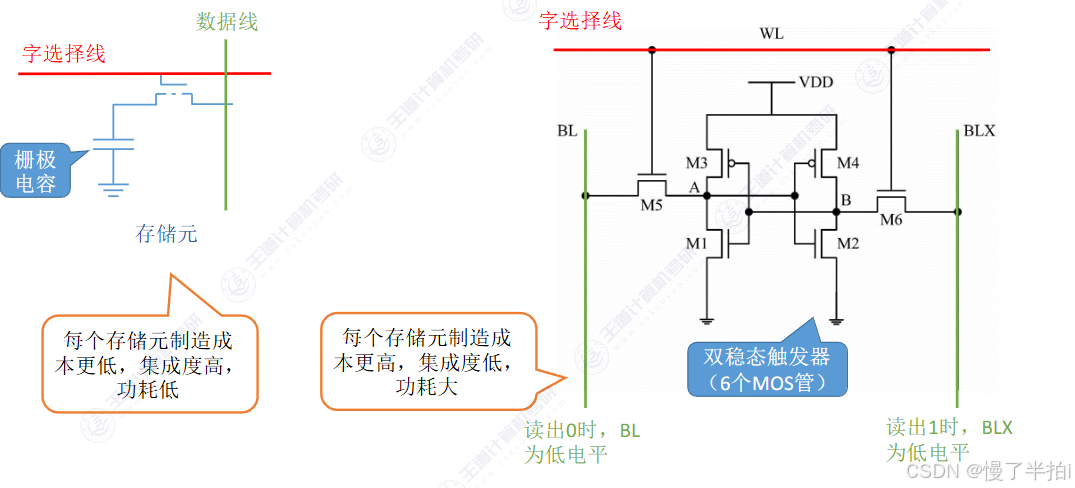

- 存儲元件特性對比

- 物理結構:

- DRAM:1個電容+1個MOS管

- SRAM:6個MOS管構成觸發器

- 制造成本:DRAM單元成本顯著低于SRAM

- 集成度:DRAM體積小集成度高,SRAM體積大集成度低

- 功耗差異:DRAM電路簡單功耗低,SRAM電路復雜功耗高

- 物理結構:

- DRAM與SRAM芯片特性

- 易失性:兩者均為斷電信息消失的易失性存儲器

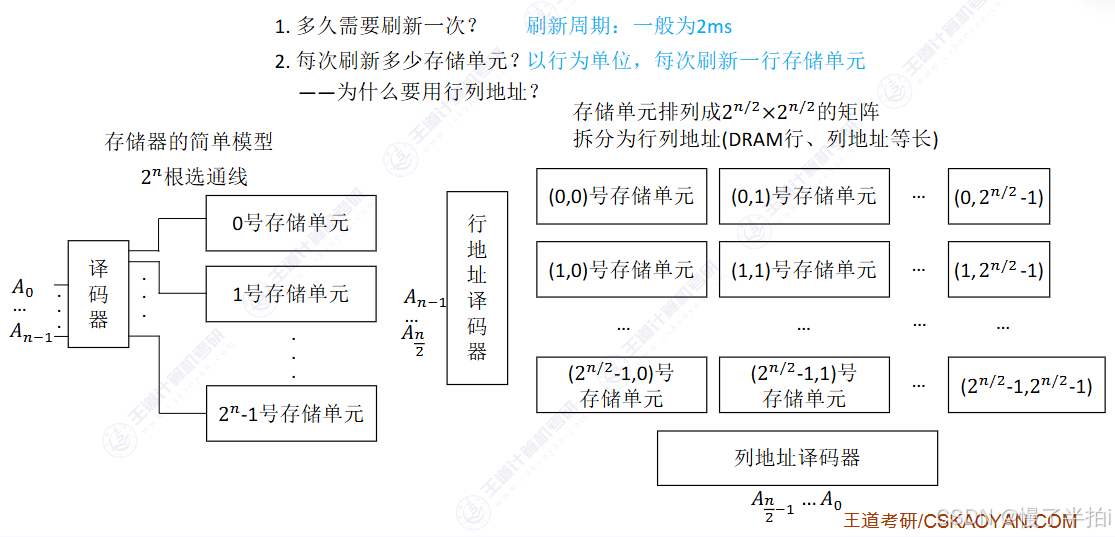

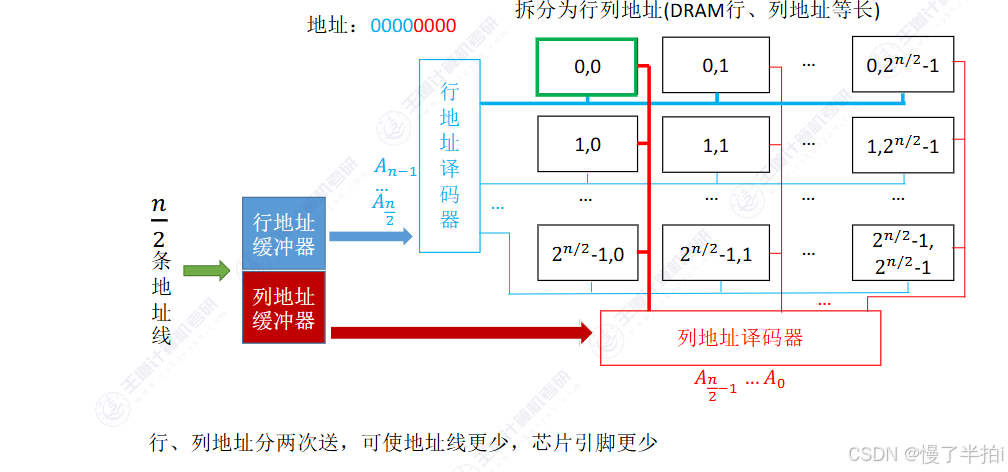

- DRAM刷新機制

刷新頻率:由于電容最多只能保持兩毫秒的電荷,所以必須在兩毫秒之內給電容重新充電刷新

刷新單位:以行為單位進行刷新,每次刷新一行存儲單元(每個存儲單元由多個存儲元構成)

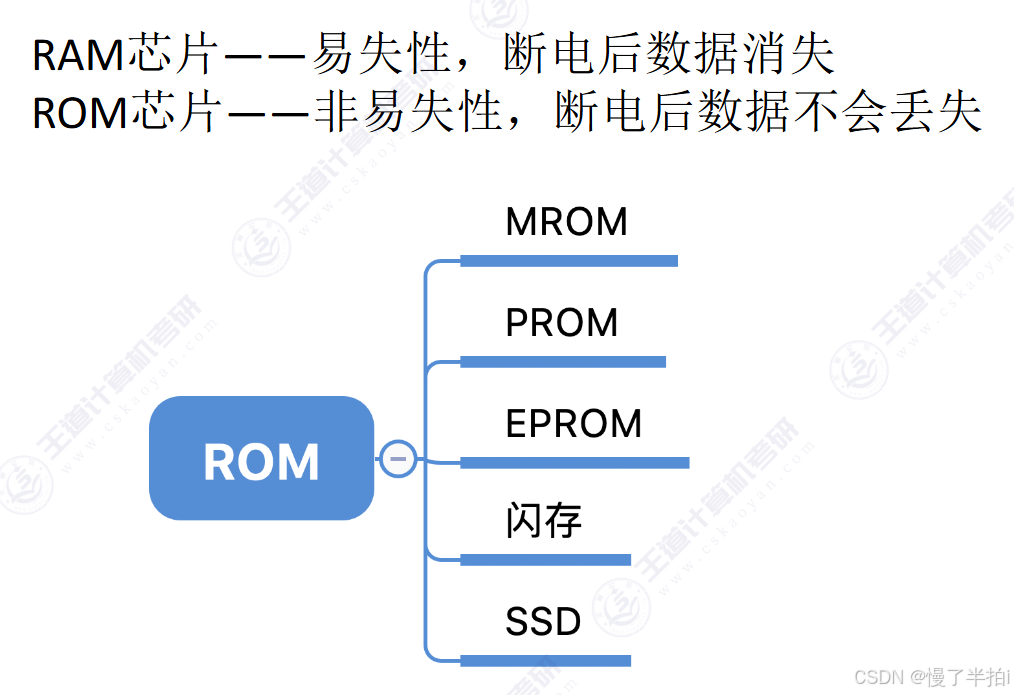

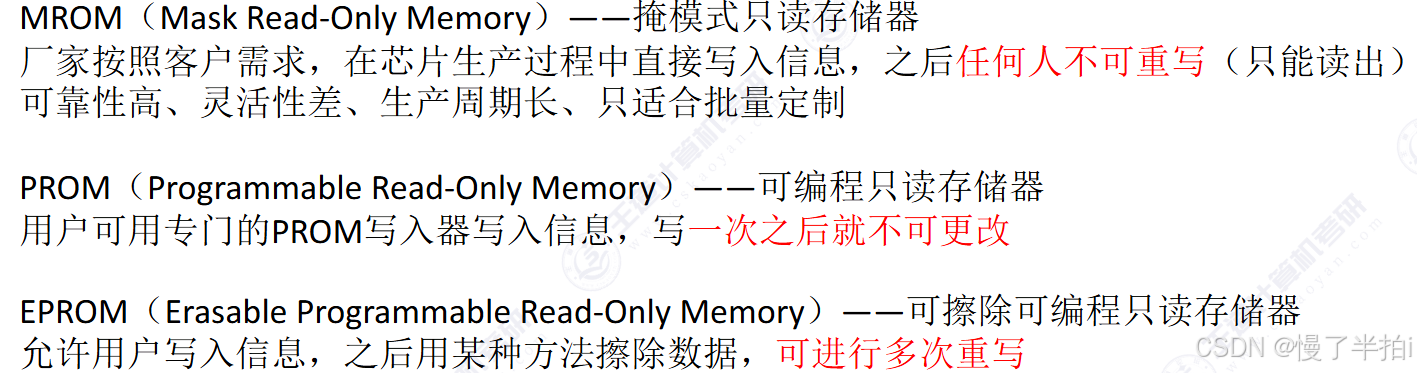

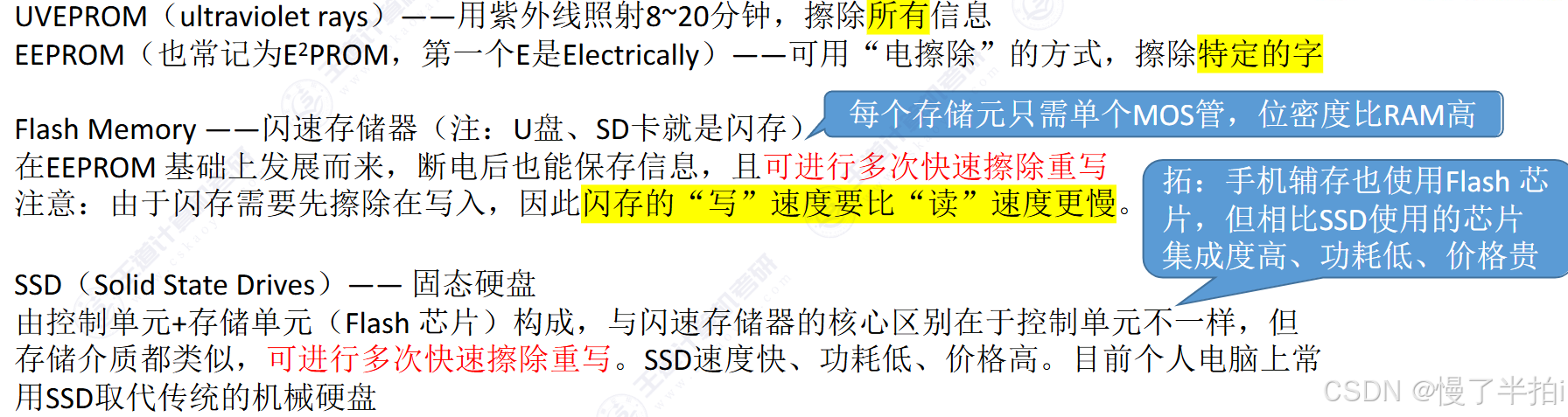

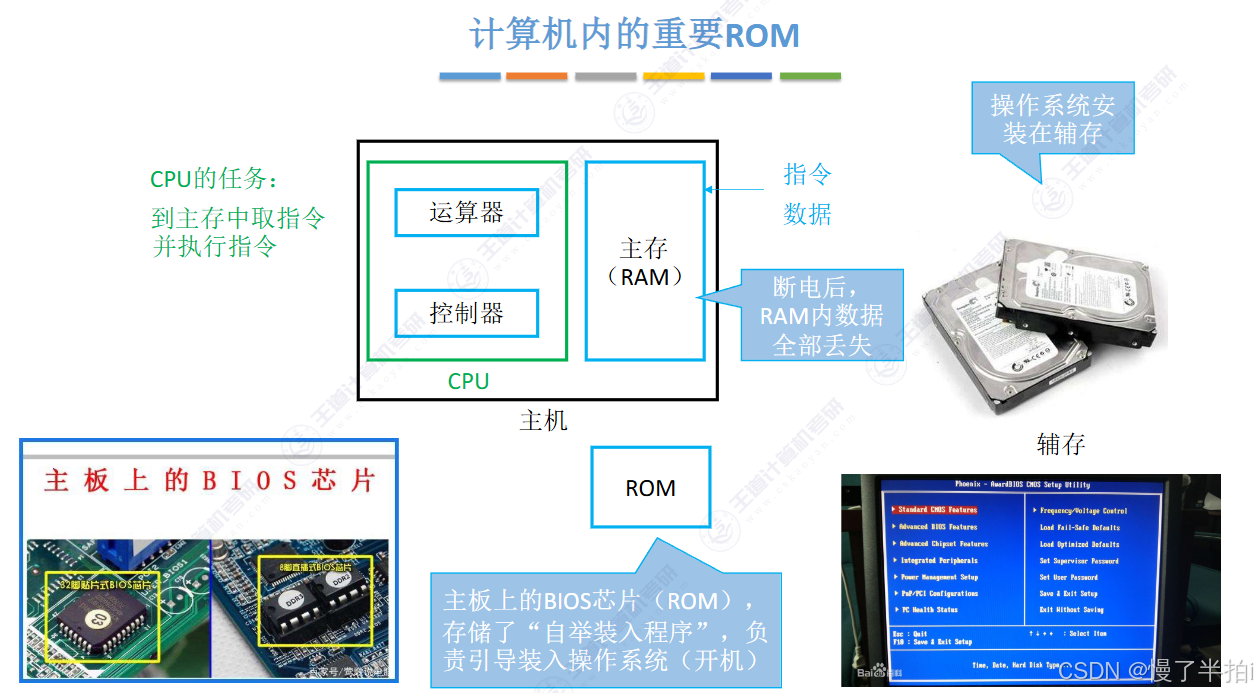

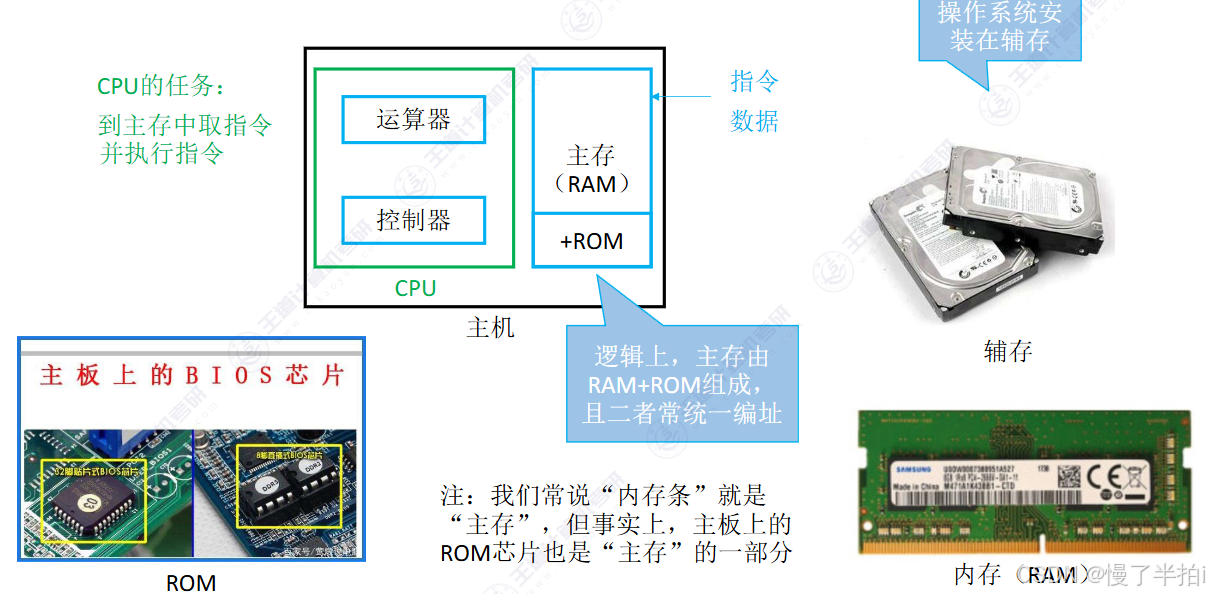

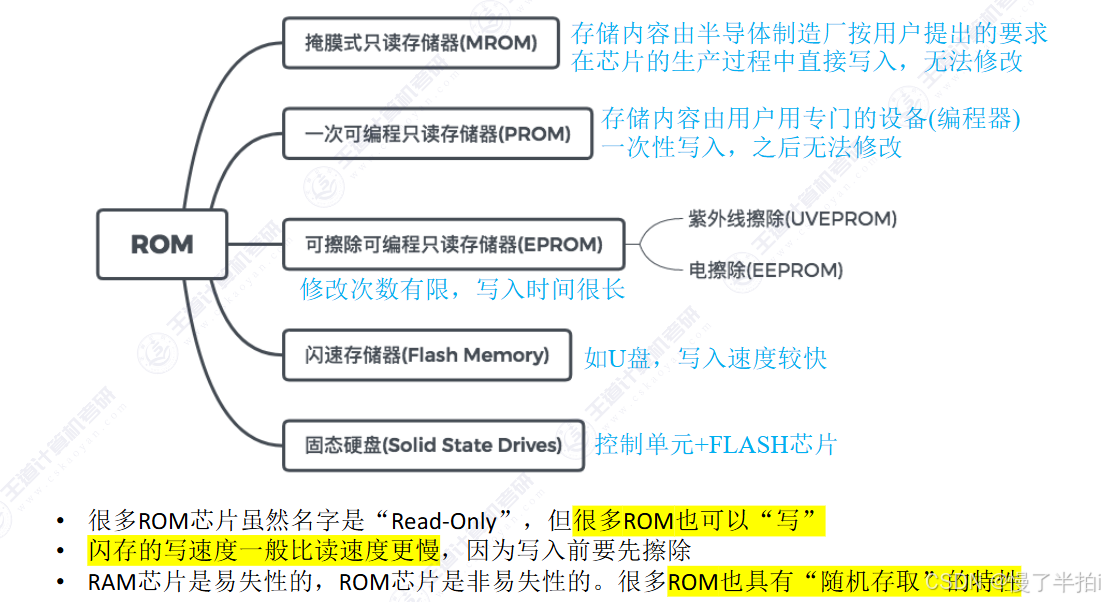

2.3 只讀存儲器?

2.4?多模塊存儲器?

三、主存儲器與 CPU 的連接

3.1 連接原理

3.2 主存容量的擴展

3.3 存儲芯片的地址分配和片選

3.4 存儲器與CPU的連接

四、外部存儲器

4.1 磁盤存儲器

4.2 固態硬盤

五、高速緩沖存儲器

5.1 程序訪問的局部性原理

5.2 Cache的基本工作原理

5.3 Cache和主存的映射方式

5.4 Cache 中主存塊的替換算法?

5.5 Cache寫策略

六、虛擬存儲器

6.1 虛擬存儲器的基本概念

6.2 頁式虛擬存儲器

6.3 段式虛擬存儲器

6.4 段頁式虛擬存儲器

6.5虛擬存儲器與 Cache 的比較

部署前后端分離程序)

)

路由)

)