第1-2周:基礎項目 - 4位加法器和計數器

目標:掌握Verilog基本語法和模塊設計。

-

第1周:

- 學習Verilog的基本語法和結構(模塊、端口、數據類型)。

- 設計并實現一個4位加法器。

- 編寫測試平臺(Testbench)對4位加法器進行功能仿真。

-

第2周:

- 學習組合邏輯設計的最佳實踐。

- 設計并實現一個4位同步計數器。

- 編寫測試平臺,對計數器進行仿真和驗證。

第3-4周:進階項目 - 多路選擇器和譯碼器

目標:深入理解組合邏輯電路和Verilog語法。

-

第3周:

- 學習多路選擇器的工作原理。

- 設計并實現一個4:1多路選擇器。

- 編寫測試平臺,對多路選擇器進行仿真和驗證。

-

第4周:

- 學習譯碼器的工作原理。

- 設計并實現一個3:8譯碼器。

- 編寫測試平臺,對譯碼器進行仿真和驗證。

第5-6周:時序邏輯設計 - 寄存器和FIFO

目標:掌握時序邏輯電路設計方法。

-

第5周:

- 學習寄存器的基本概念和設計方法。

- 設計并實現一個8位移位寄存器。

- 編寫測試平臺,對移位寄存器進行仿真和驗證。

-

第6周:

- 學習FIFO(先進先出隊列)的工作原理。

- 設計并實現一個簡單的FIFO。

- 編寫測試平臺,對FIFO進行仿真和驗證。

第7-8周:狀態機設計 - 簡單UART模塊

目標:理解和設計有限狀態機(FSM)。

-

第7周:

- 學習有限狀態機的概念和設計方法。

- 設計并實現一個簡單的UART發送器。

- 編寫測試平臺,對UART發送器進行仿真和驗證。

-

第8周:

- 設計并實現一個簡單的UART接收器。

- 編寫測試平臺,對UART接收器進行仿真和驗證。

第9-10周:項目整合 - UART通信系統

目標:將多個模塊整合成一個完整的系統。

-

第9周:

- 將UART發送器和接收器整合成一個完整的通信系統。

- 設計并實現UART通信系統的頂層模塊。

- 編寫測試平臺,對整個系統進行仿真和驗證。

-

第10周:

- 在FPGA開發板上實現UART通信系統。

- 測試系統在實際硬件上的性能和功能。

- 進行調試和優化。

第11-12周:高級項目 - 簡單CPU設計

目標:綜合應用所學知識設計一個簡單的CPU。

- 第11周:

- 學習CPU的基本工作原理和結構。

- 設計并實現一個簡單的CPU數據路徑。

- 編寫測試平臺,對數據路徑進行仿真和驗證。

- 第12周:

- 設計并實現CPU的控制單元。

- 整合數據路徑和控制單元,完成CPU設計。

- 編寫測試平臺,對整個CPU進行仿真和驗證。

- 在FPGA開發板上實現并測試CPU。

資源推薦

-

書籍:

- 《Verilog HDL》 by Samir Palnitkar

- 《FPGA Prototyping by Verilog Examples》 by Pong P. Chu

-

在線課程:

- Coursera上的“FPGA Design for Embedded Systems”

- edX上的“Digital Design using Verilog”

-

開發板:

-

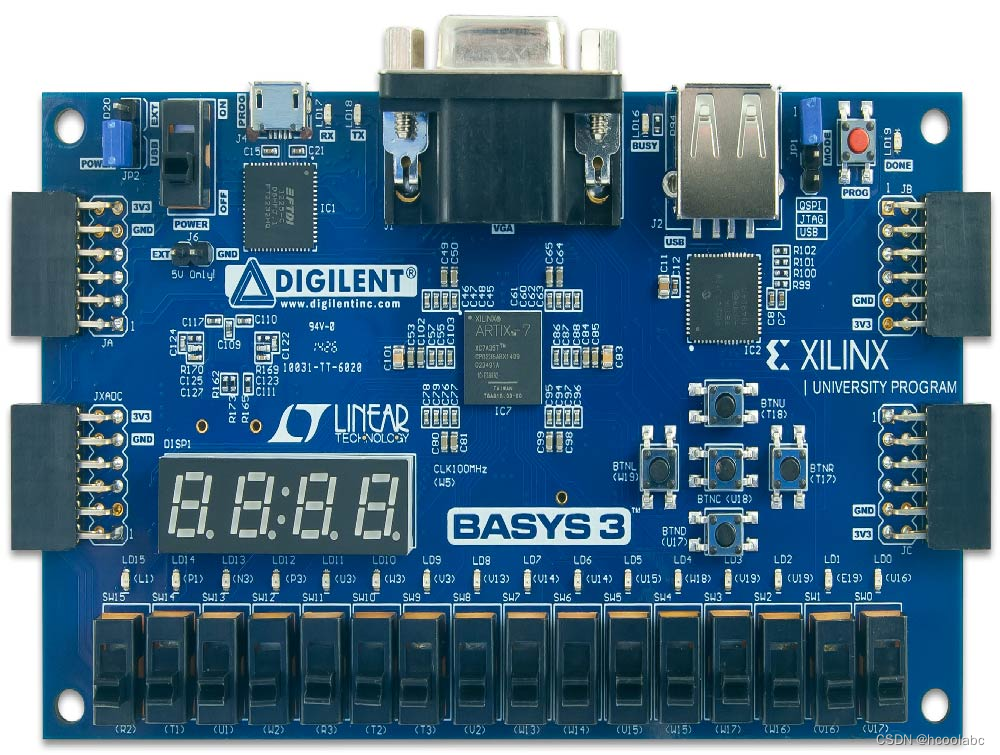

Xilinx的開發板

-

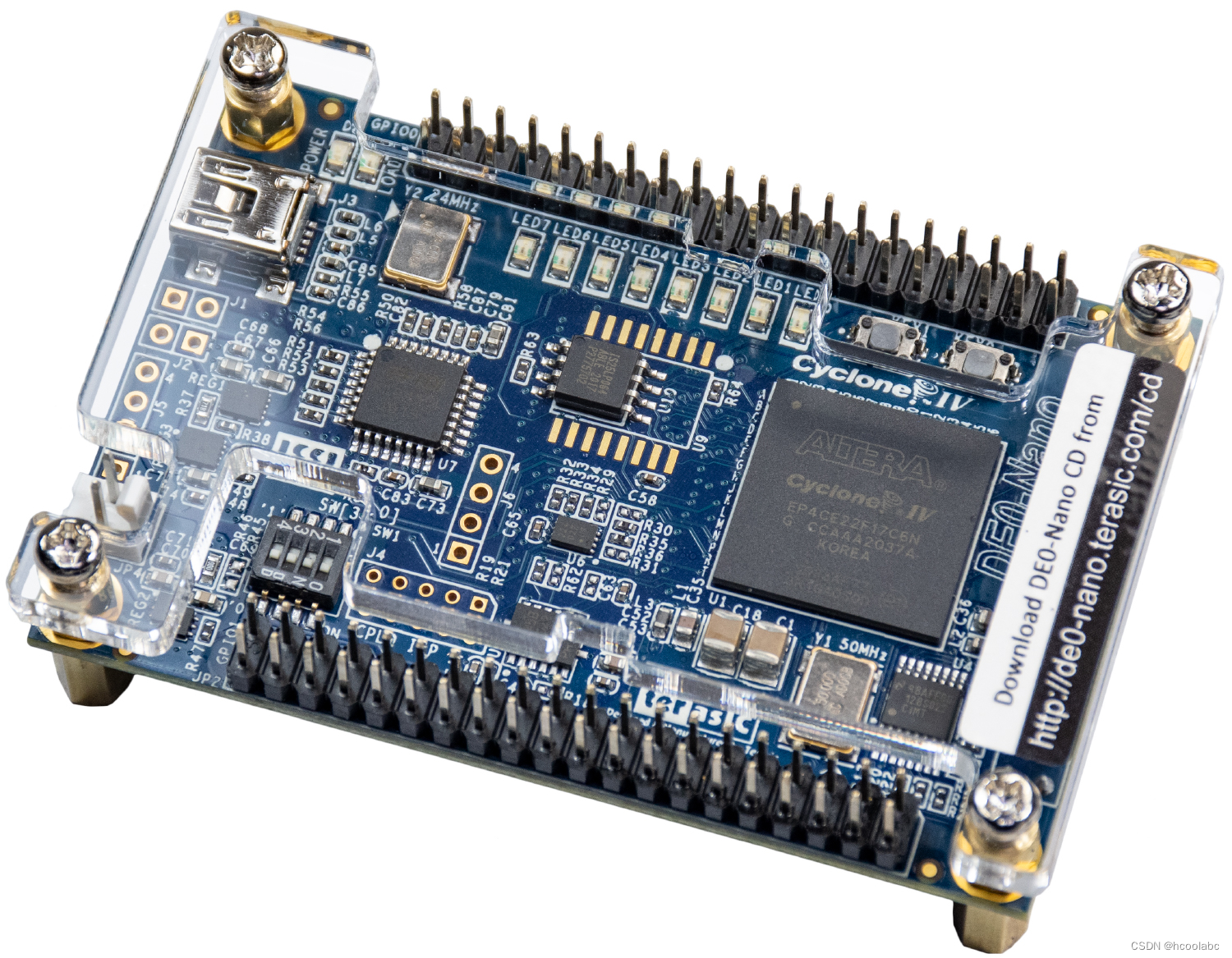

Intel的開發板

-

-

通過嚴格按照周計劃進行學習和實踐,可以有效地掌握FPGA設計的基本技能和方法,為更復雜的項目打下堅實的基礎。

--direct)

)

?)

![[Information Sciences 2023]用于假新聞檢測的相似性感知多模態提示學習](http://pic.xiahunao.cn/[Information Sciences 2023]用于假新聞檢測的相似性感知多模態提示學習)

![洛谷 AT_abc169_d [ABC169D] Div Game 題解](http://pic.xiahunao.cn/洛谷 AT_abc169_d [ABC169D] Div Game 題解)