請閱讀【ARM Cache 及 MMU/MPU 系列文章專欄導讀】

及【嵌入式開發學習必備專欄】

文章目錄

- Direct access to internal memory

- L1 cache encodings

- L1 Cache Data 寄存器

- Cache 數據讀取代碼實現

Direct access to internal memory

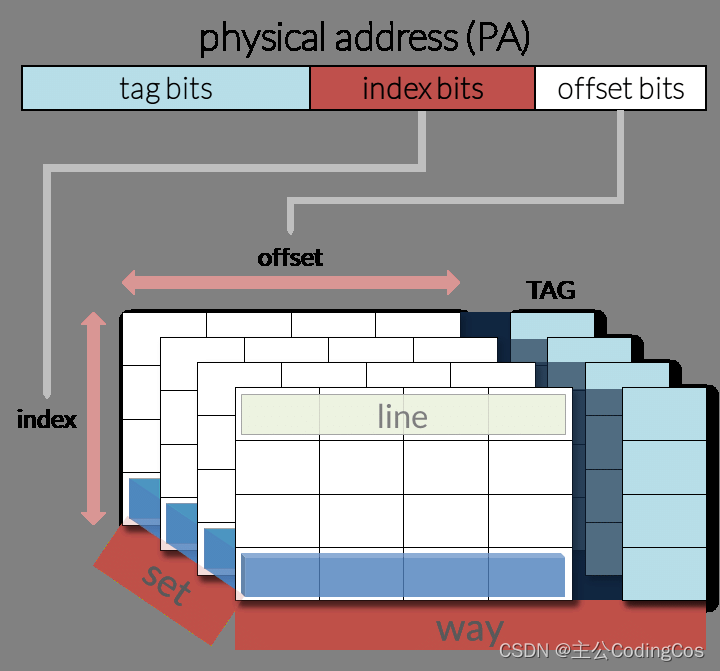

在ARMv8架構中,緩存(Cache)是用來加速數據訪問的關鍵組件,它利用了程序執行中的局部性原理來提高性能。緩存中的每一行(Cache Line)通常包含了兩個主要部分:實際的數據和一個標記(Tag)。這個標記用來標識存儲在緩存行中的數據在內存中的位置。

圖 1-1 4-way, 4-sets set-associative cache

關于cache 中 set 和 way 的定義見文章:【ARM Cache 系列文章 1 – Cache基礎概念學習】

ARMv9架構中,核心提供了一種機制,可以通過實現定義的系統寄存器

:最大回撤率)

)

——水印注釋(Watermark))