題目匯總版--鏈接:?

【硬件-筆試面試題】硬件/電子工程師,筆試面試題匯總版,持續更新學習,加油!!!-CSDN博客

【硬件-筆試面試題-92】硬件/電子工程師,筆試面試題(知識點:米勒效應,米勒平臺)

1、題目

米勒效應,米勒平臺

2、知識點

米勒效應(Miller Effect)是高頻電子電路中一種重要的寄生電容影響現象,由美國工程師約翰?米爾頓?米勒(John Milton Miller)于 1920 年提出。它描述了放大器中輸入電容因電壓放大作用而等效增大的現象,會顯著影響電路的高頻性能,是高頻設計中必須考慮的關鍵問題。

一、米勒效應的本質

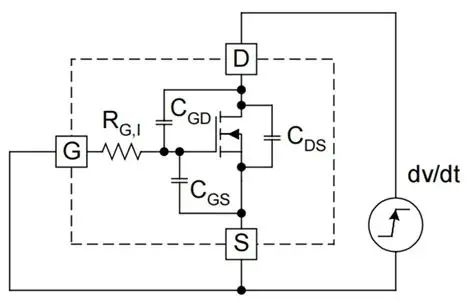

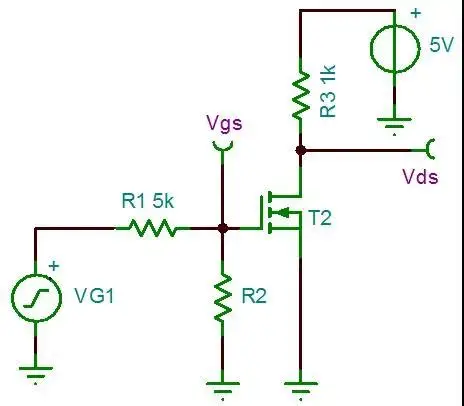

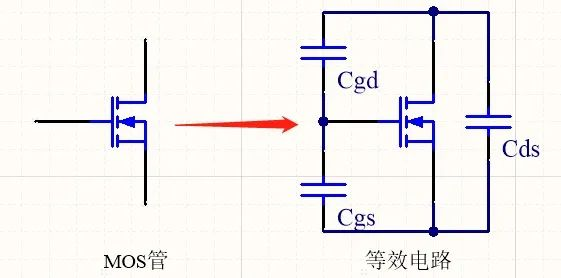

在共射(或共源)放大電路中,晶體管(BJT 或 MOS 管)的輸出端與輸入端之間存在寄生電容(如 BJT 的集電結電容\(C_{bc}\),MOS 管的柵漏電容\(C_{gd}\))。當電路工作在高頻時,這一電容會因輸出與輸入之間的電壓放大作用,在輸入端呈現出等效電容增大的現象,即米勒效應。

核心原理:

設晶體管的輸入輸出間寄生電容為C,電壓放大倍數為\(A_v\)(輸出電壓與輸入電壓的比值,通常為負值,因共射電路反相),則輸入端的等效米勒電容\(C_{M}\)為:\(C_M = C \times (1 - A_v)\)

- 對于共射放大器,\(A_v\)為負值(如\(A_v = -100\)),則\(C_M = C \times (1 + |A_v|)\),即等效電容是原電容的\((1 + |A_v|)\)倍。

- 例如:若\(C = 1pF\),\(|A_v| = 100\),則\(C_M = 101pF\),寄生電容被放大了 100 倍。

二、米勒效應的產生條件

米勒效應的產生需要兩個關鍵條件:

- 存在跨接于輸入與輸出之間的電容(可以是器件寄生電容,也可以是分布電容);

- 電路具有電壓放大作用(輸入與輸出之間存在電壓增益\(A_v \neq 0\))。

這兩個條件在大多數放大器(如共射、共源放大電路)中天然存在,因此米勒效應是高頻放大電路中的普遍現象。

三、對電路性能的影響

米勒效應的核心危害是增大輸入端等效電容,進而影響電路的高頻響應:

-

降低帶寬: 輸入端的等效米勒電容\(C_M\)會與信號源內阻\(R_s\)形成 RC 低通濾波網絡(時間常數\(\tau = R_s \times C_M\)),導致高頻信號衰減,使放大器的帶寬(截止頻率)降低。 截止頻率計算公式:\(f_H \approx \frac{1}{2\pi R_s C_M}\),\(C_M\)越大,\(f_H\)越低。

-

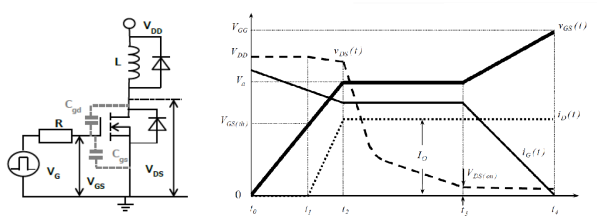

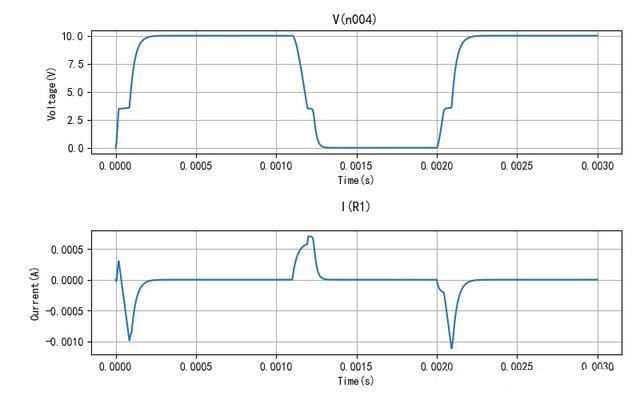

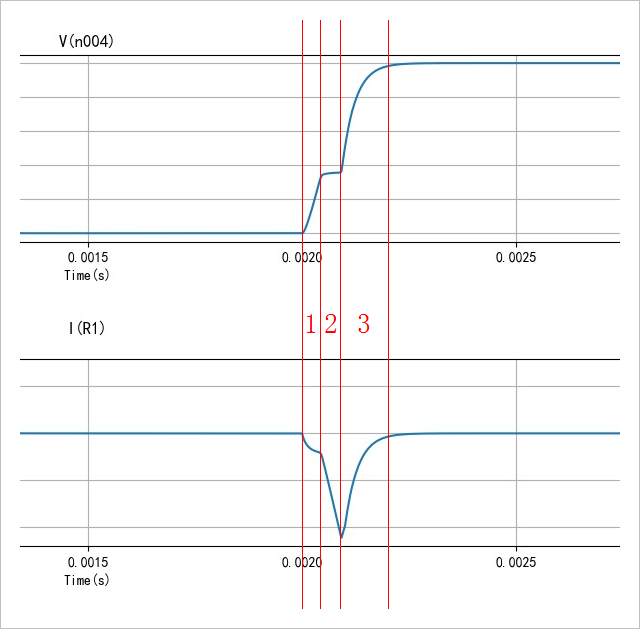

增加信號延遲: 米勒電容的充放電需要時間,會導致輸入信號的相位延遲,尤其在高速開關電路(如數字邏輯門、高頻脈沖放大)中,可能引發信號失真。

-

降低輸入阻抗: 高頻時,電容的容抗\(X_C = \frac{1}{2\pi f C_M}\)隨頻率升高而減小,導致放大器的輸入阻抗下降,加重信號源的負載。

四、抑制米勒效應的方法

在高頻電路設計中,需通過以下手段減小米勒效應的影響:

-

采用共基極(或共柵極)組態: 共基極電路中,晶體管的基極(或柵極)接地,輸入信號加在發射極(或源極),輸出信號從集電極(或漏極)取出。此時,輸入與輸出之間的寄生電容跨接于低阻抗節點(發射極)和高阻抗節點(集電極),電壓增益\(A_v \approx 1\)(無電壓放大),米勒效應幾乎可以忽略。

- 優勢:共基極電路帶寬遠高于共射電路,適合高頻放大(如射頻電路)。

-

使用屏蔽和隔離技術: 減少輸入與輸出端之間的分布電容(如 PCB 布線時避免輸入線與輸出線平行,增加間距或加接地屏蔽層),從源頭降低跨接電容C。

-

采用負反饋補償: 通過外部電路引入負反饋,降低輸入輸出之間的有效電壓增益\(A_v\),從而減小米勒電容\(C_M = C(1 - A_v)\)。

-

拆分電容(米勒分裂技術): 在高頻功率放大電路中,通過在晶體管的輸入輸出端之間串聯電阻,將寄生電容 “分裂” 為兩個較小的電容,分別等效到輸入和輸出端,降低對輸入端的影響。

-

選用高頻特性好的器件: 選擇寄生電容(如\(C_{bc}\)、\(C_{gd}\))小的高頻晶體管(如射頻 BJT、GaN MOS 管),從器件層面減小米勒效應的基礎。

五、典型應用場景與案例

-

高頻放大器設計: 共射放大器在低頻時增益高,但高頻因米勒效應帶寬受限;而共基放大器無米勒效應,適合作為高頻信號的緩沖或放大(如電視機的高頻頭電路)。

-

數字邏輯門: CMOS 反相器中,柵漏電容\(C_{gd}\)會產生米勒效應,導致開關速度下降。因此,高速數字電路(如 GHz 級 CPU)需通過優化器件結構(減小\(C_{gd}\))和布線來抑制米勒效應。

-

射頻電路: 在射頻功率放大器中,米勒效應會導致輸入阻抗隨頻率變化,影響阻抗匹配,需通過上述米勒分裂技術或共基組態優化。

總結

米勒效應是高頻電路中因寄生電容和電壓放大共同作用導致的輸入電容等效增大現象,主要危害是降低帶寬、增加延遲。理解其原理后,可通過選擇合適的電路組態(如共基極)、優化器件和布線、采用補償技術等方式抑制其影響,這對高頻電子設計(如通信、雷達、高速數字電路)至關重要。

題目匯總--鏈接:

【硬件-筆試面試題】硬件/電子工程師,筆試面試題匯總版,持續更新學習,加油!!!-CSDN博客

)

)

)