VGA顯示彩條和圖片

文章目錄

- VGA顯示彩條和圖片

- 一、VGA簡介

- 二、功能設計

- 1、彩條設計

- 2、圖片設計

- 三、結果展示

- 四、代碼

一、VGA簡介

VGA(Video Graphics Array)是IBM在1987年隨PS/2機?起推出的?種視頻,具有分辨率?、顯?速率快、顏?豐富等優點,在彩 ?顯?器領域得到了?泛的應?。不?持熱插拔,不?持?頻傳輸。對于?些嵌?式VGA顯?系統,可以在不使?VGA顯?卡和計算機的 情況下,實現VGA圖像的顯?和控制。VGA顯?器具有成本低、結構簡單、應?靈活的優點。

VGA的顯示原理是:CRT (陰極射線管)以“Z”型掃描的方式將陰極射線槍發出的電子束打在涂有熒光粉的災光屏上,廣土RUD 4日方換行的過程中,電下L一行,電子槍都要回到屏幕的下一行左邊的起始位置,并且在換行的過程中,電子槍需要消隱,避免破壞已經成像的像素。

標準的VGA接口是15針的D型接口,分成3排,每排5個孔,是顯卡上應用最為廣泛的接口類型,絕大多數顯卡都帶有此種接口。它傳輸紅、綠、藍模擬信號以及同步信號(水平同步信號和垂直同步信號)。

VGA的時序包括同步信號、消隱區,還有顏色數據的輸出。行場時序均可分為4部分:同步脈沖、顯示后沿、顯示時序、顯示前沿。

行掃描時序:

同步脈沖a:代表新一行像素掃描的開始,同時也是上一行掃描的結束。

顯示時序c:是真正圖像的顯示區域,在此階段,像素逐個顯示出來,即在這一階段控制紅、綠、藍三基色信號輸出對應像素的 RGB值。

顯示后沿b和顯示前沿d:這兩個階段是消隱時刻,消隱區紅、綠、藍三基色信號都為0(黑色)或根據實際情況處理。

**場掃描時序:**時序與行掃描相同。

有效區域

常見VGA分辨率參數表

| 分辨率 | 像素時鐘 (MHz) | Active行有效區 (Pixels) | Front Porch行顯示前沿 (Pixels) | Sync Pulse行有效 (Pixels) | Back Porch行顯示后沿 (Pixels) | Total 行總像素(Pixels) | Active 場有效區(Lines) | Front Porch 場顯示前沿(Lines) | Sync Pulse 場有效區(Lines) | Back Porch 場顯示后沿(Lines) | Total 場總像素(Lines) |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 640×480@60 | 25.175 | 640 | 16 | 96 | 48 | 800 | 480 | 10 | 2 | 33 | 525 |

| 800×600@60 | 40.000 | 800 | 40 | 128 | 88 | 1056 | 600 | 1 | 4 | 23 | 628 |

| 1280×720@60 | 74.250 | 1280 | 110 | 40 | 220 | 1650 | 720 | 5 | 5 | 20 | 750 |

| 1024×768@60 | 65.000 | 1024 | 24 | 136 | 160 | 1344 | 768 | 3 | 6 | 29 | 806 |

| 1920×1080@60 | 148.50 | 1920 | 88 | 44 | 148 | 2200 | 1080 | 4 | 5 | 36 | 1125 |

本次運用的開發板通過權電阻網絡進行數模轉換

可知采用的為RGB565格式。

二、功能設計

在了解了VGA時序之后,即可設計出完整的流程。

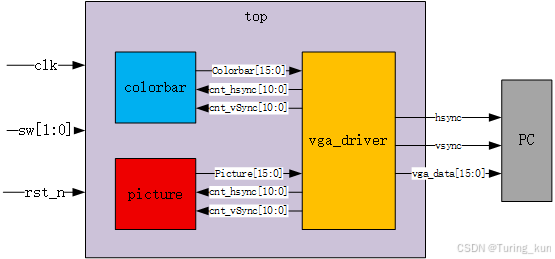

通過sw開關控制顯示彩條還是顯示圖片,VGA通過轉接線連至PC進行顯示。

1、彩條設計

//colorbar(8個橫條紋)

always @(posedge clk or negedge rst_n)begin if(!rst_n)colorbar <= 16'h0000;else beginif((cnt_vsync >= `V_SP + `V_BP) && (cnt_vsync < `V_SP + `V_BP + (`V_AV>>3)))colorbar <= 16'hf8_00;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>3)) && (cnt_vsync < `V_SP + `V_BP + (`V_AV>>2)))colorbar <= 16'hff_e0;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>2)) && (cnt_vsync < `V_SP + `V_BP + ((`V_AV>>2) + (`V_AV>>3))))colorbar <= 16'h04_00;else if((cnt_vsync >= `V_SP + `V_BP + ((`V_AV>>2) + (`V_AV>>3))) && (cnt_vsync < `V_SP + `V_BP + (`V_AV>>1)))colorbar <= 16'h80_10;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>1)) && (cnt_vsync < `V_SP + `V_BP + (`V_AV>>1) + (`V_AV>>3)))colorbar <= 16'h00_1f;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>1) + (`V_AV>>3)) && (cnt_vsync < `V_SP + `V_BP + (`V_AV>>1) + (`V_AV>>2)))colorbar <= 16'hfd_20;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>1) + (`V_AV>>2)) && (cnt_vsync < `V_SP + `V_BP + ((`V_AV>>1) + (`V_AV>>2) + (`V_AV>>3))))colorbar <= 16'hf7_be;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>1) + (`V_AV>>2) + (`V_AV>>3)) && (cnt_vsync < `V_SP + `V_BP + `V_AV))colorbar <= 16'h80_10;else colorbar <= 16'h00_00;end

end

按照vga顯示時序,在有效區分成8個等分的區域,顯示八個彩條。

2、圖片設計

采用一個ROM,將圖片數據存入ROM,由于開發板資源有限,圖片只能采用一個極小的格式進行存儲。

ken_rom ken_rom_inst (.address ( address ),.clock ( clk ),.q ( data ));always @( posedge clk or negedge rst_n ) beginif ( !rst_n ) beginaddress <= 0;// 復位時清零ROM地址endelse if ( flag_clear_rom_address ) begin //計數滿清零address <= 0;endelse if (( (cnt_hsync >= 144) && (cnt_hsync < 233) ) && ((cnt_vsync >= 35) && (cnt_vsync < 161)))begin //在有效區域內+1address <= address + 1;endelse begin //無效區域保持address <= address;end

end

assign flag_clear_rom_address = ((address == 11214 - 1) );

(ps:本次主要為驗證VGA功能,ROM的地址選擇和圖片的位圖有些缺點)

三、結果展示

開關為01,顯示圖片(地址有誤導致圖片錯位)

開關撥到其他位置顯示彩條

四、代碼

1、top

module top (input clk ,input rst_n ,input [1:0] sw ,output hsync ,output vsync ,output [15:0] vga_data

);wire [15:0] colorbar;

wire [10:0] cnt_hsync;

wire [10:0] cnt_vsync;

wire [15:0] ken_data;color_bar inst_color_bar(.clk (clk ),.rst_n (rst_n ),.cnt_hsync (cnt_hsync),.cnt_vsync (cnt_vsync),.colorbar (colorbar )

);vga_driver inst_vga_driver(.clk (clk ),.rst_n (rst_n ),.sw (sw ),.ken_data (ken_data ),.colorbar (colorbar ),.hsync (hsync ),.vsync (vsync ),.cnt_hsync (cnt_hsync),.cnt_vsync (cnt_vsync),.h_vld (h_vld ),.v_vld (v_vld ),.vga_data (vga_data )

);picture inst_picture(.clk (clk),.rst_n (rst_n),.sw (sw),.cnt_hsync (cnt_hsync),.cnt_vsync (cnt_vsync),.data (ken_data)

);endmodule

2、color_bar

`include "param.v" module color_bar( input clk ,input rst_n ,input [10:0] cnt_hsync,input [10:0] cnt_vsync,output reg [15:0] colorbar

);//colorbar(8個橫條紋)

always @(posedge clk or negedge rst_n)begin if(!rst_n)colorbar <= 16'h0000;else beginif((cnt_vsync >= `V_SP + `V_BP) && (cnt_vsync < `V_SP + `V_BP + (`V_AV>>3)))colorbar <= 16'hf8_00;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>3)) && (cnt_vsync < `V_SP + `V_BP + (`V_AV>>2)))colorbar <= 16'hff_e0;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>2)) && (cnt_vsync < `V_SP + `V_BP + ((`V_AV>>2) + (`V_AV>>3))))colorbar <= 16'h04_00;else if((cnt_vsync >= `V_SP + `V_BP + ((`V_AV>>2) + (`V_AV>>3))) && (cnt_vsync < `V_SP + `V_BP + (`V_AV>>1)))colorbar <= 16'h80_10;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>1)) && (cnt_vsync < `V_SP + `V_BP + (`V_AV>>1) + (`V_AV>>3)))colorbar <= 16'h00_1f;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>1) + (`V_AV>>3)) && (cnt_vsync < `V_SP + `V_BP + (`V_AV>>1) + (`V_AV>>2)))colorbar <= 16'hfd_20;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>1) + (`V_AV>>2)) && (cnt_vsync < `V_SP + `V_BP + ((`V_AV>>1) + (`V_AV>>2) + (`V_AV>>3))))colorbar <= 16'hf7_be;else if((cnt_vsync >= `V_SP + `V_BP + (`V_AV>>1) + (`V_AV>>2) + (`V_AV>>3)) && (cnt_vsync < `V_SP + `V_BP + `V_AV))colorbar <= 16'h80_10;else colorbar <= 16'h00_00;end

endendmodule

3、picture

`include "param.v"module picture(input clk,input rst_n,input [1:0] sw,input [10:0] cnt_hsync,input [10:0] cnt_vsync,output [15:0] data

);wire flag_clear_rom_address;reg [14:0] address;ken_rom ken_rom_inst (.address ( address ),.clock ( clk ),.q ( data ));always @( posedge clk or negedge rst_n ) beginif ( !rst_n ) beginaddress <= 0;// 復位時清零ROM地址endelse if ( flag_clear_rom_address ) begin //計數滿清零address <= 0;endelse if (( (cnt_hsync >= 144) && (cnt_hsync < 233) ) && ((cnt_vsync >= 35) && (cnt_vsync < 161)))begin //在有效區域內+1address <= address + 1;endelse begin //無效區域保持address <= address;end

end

assign flag_clear_rom_address = ((address == 11214 - 1) );

endmodule

4、vga_driver

`include "param.v" module vga_driver( input clk ,input rst_n ,input [1:0] sw ,input [15:0] colorbar , //RGB565 input [15:0] ken_data , output hsync ,output vsync ,output reg [10:0] cnt_hsync,output reg [10:0] cnt_vsync,output h_vld ,output v_vld ,output reg [15:0] vga_data

);wire add_cnt_vsync;

wire end_cnt_vsync;wire add_cnt_hsync;

wire end_cnt_hsync;//行同步always @(posedge clk or negedge rst_n)begin if(!rst_n)begincnt_hsync <= 'd0;end else if(add_cnt_hsync)begin if(end_cnt_hsync)begin cnt_hsync <= 'd0;endelse begin cnt_hsync <= cnt_hsync + 1'b1;end end

end assign add_cnt_hsync = 1;

assign end_cnt_hsync = add_cnt_hsync && cnt_hsync == `H_TOTAL -1;//場同步always @(posedge clk or negedge rst_n)begin if(!rst_n)begincnt_vsync <= 'd0;end else if(add_cnt_vsync)begin if(end_cnt_vsync)begin cnt_vsync <= 'd0;endelse begin cnt_vsync <= cnt_vsync + 1'b1;end end

end assign add_cnt_vsync = end_cnt_hsync;

assign end_cnt_vsync = add_cnt_vsync && cnt_vsync == `V_TOTAL - 1;//hsync

assign hsync = (cnt_hsync < `H_SP )? 1'b0 : 1'b1;

//vsync

assign vsync = (cnt_vsync < `V_SP )? 1'b0 : 1'b1;//h_vld

assign h_vld = (cnt_hsync >= `H_SP + `H_BP) && (cnt_hsync < `H_TOTAL - `H_FP);

//v_vld

assign v_vld = (cnt_vsync >= `V_SP + `V_BP) && (cnt_vsync < `V_TOTAL - `V_FP);//vga_dataalways @(*)begincase(sw)2'b01 : vga_data = (( (cnt_hsync >= 144) && (cnt_hsync < 233) ) && ((cnt_vsync >= 35) && (cnt_vsync < 161))) ? ken_data : 16'h0000;default:vga_data = (h_vld && v_vld) ? colorbar : 16'd0;endcase

endendmodule

5、param

`define PIXEL_640_480

// `define PIXEL_800_600

// `define PIXEL_1920_1080`ifdef PIXEL_640_480

//行同步信號`define H_SP 96`define H_BP 48 //顯示后沿`define H_AV 640 //有效區域`define H_FP 16 //顯示前沿`define H_TOTAL 800 //總像素//場同步信號`define V_SP 2`define V_BP 33 //顯示后沿`define V_AV 480 //有效區域`define V_FP 10 //顯示前沿`define V_TOTAL 525 //總像素`elsif PIXEL_800_600

//行同步信號`define H_SP 128`define H_BP 88 //顯示后沿`define H_AV 800 //有效區域`define H_FP 40 //顯示前沿`define H_TOTAL 1056 //總像素//場同步信號`define V_SP 4`define V_BP 23 //顯示后沿`define V_AV 600 //有效區域`define V_FP 1 //顯示前沿`define V_TOTAL 628 //總像素`elsif PIXEL_1920_1080

//行同步信號`define H_SP 44`define H_BP 148 //顯示后沿`define H_AV 1920 //有效區域`define H_FP 88 //顯示前沿`define H_TOTAL 2200 //總像素//場同步信號`define V_SP 5`define V_BP 36 //顯示后沿`define V_AV 1080 //有效區域`define V_FP 4 //顯示前沿`define V_TOTAL 1125 //總像素

`endif

![week2-[一維數組]出現次數](http://pic.xiahunao.cn/week2-[一維數組]出現次數)

)