目錄

1.引言

2.算法仿真效果

3.算法涉及理論知識概要

3.1 16QAM調制軟解調原理

3.2 幀同步

3.3 卷積編碼,維特比譯碼

4.Verilog程序接口

5.參考文獻

6.完整算法代碼文件獲得

1.引言

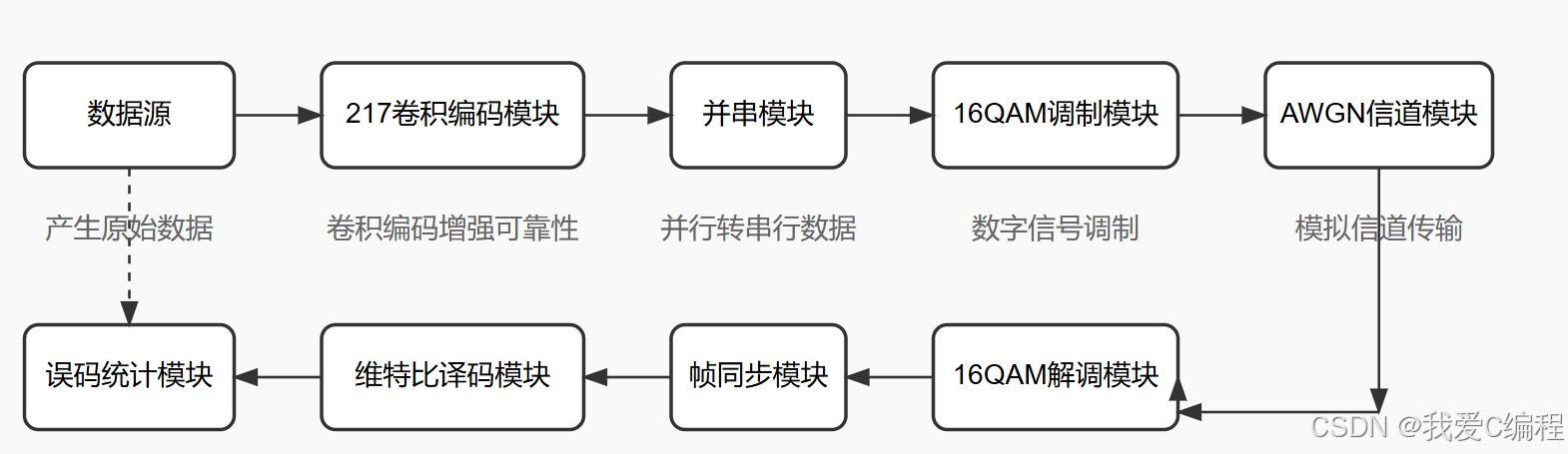

? ? ? ? 基于FPGA的16QAM軟解調+卷積編碼Viterbi譯碼通信系統開發,包含幀同步,高斯信道,誤碼統計,可設置SNR。系統包括16QAM調制模塊,16QAM軟解調模塊,217卷積編碼模塊,維特比譯碼模塊,AWGN信道模塊,誤碼統計模塊,幀同步模塊,數據源模塊等。

2.算法仿真效果

本系統是在

基于FPGA的16QAM軟解調+幀同步系統verilog開發,包含testbench,高斯信道,誤碼統計,可設置SNR_quartus 幀同步 仿真圖-CSDN博客

基礎上,增加了217卷積編碼,維特比譯碼(不使用編譯碼IP核),從而提升系統性能。

vivado2022.2測試

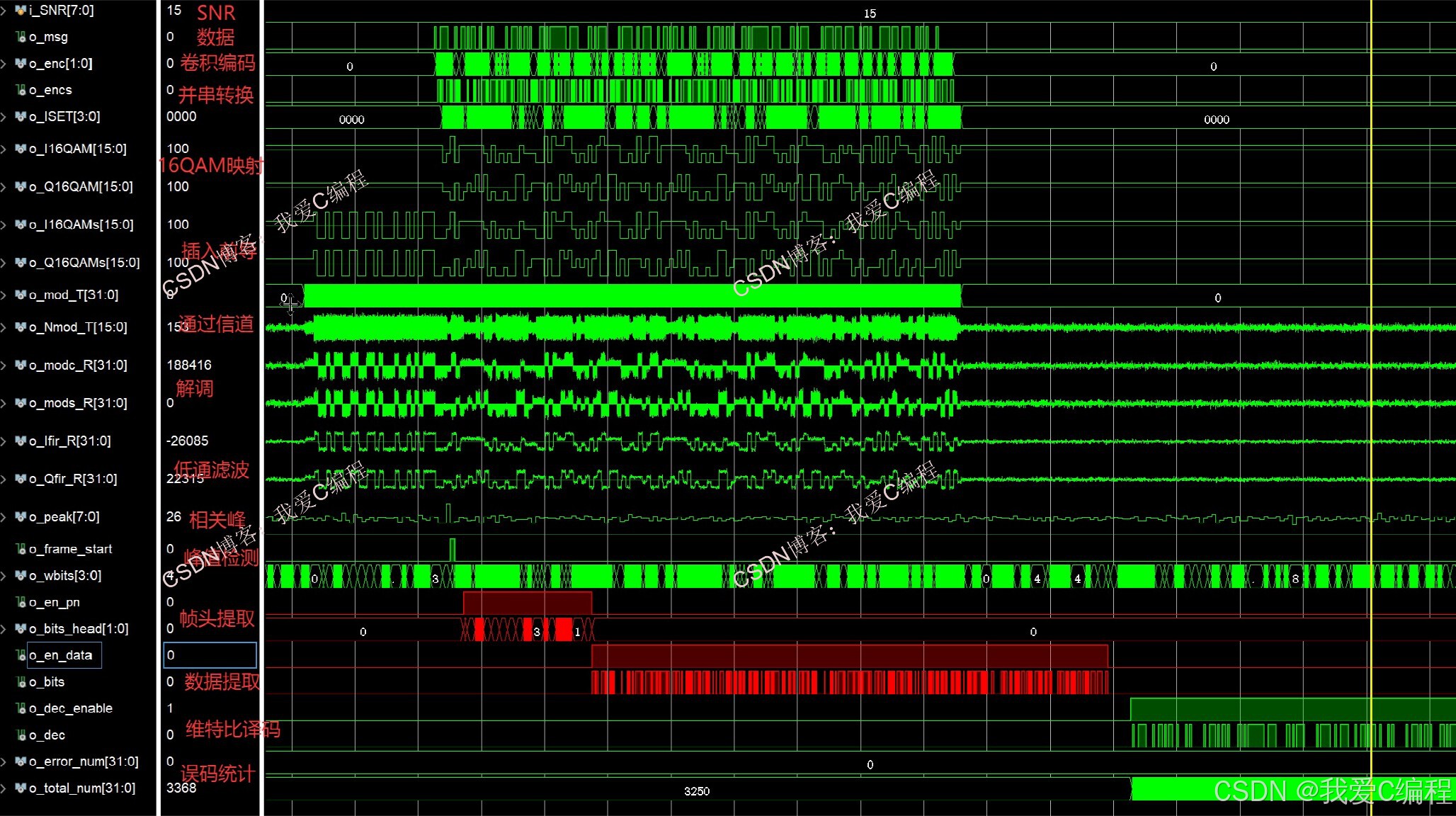

設置SNR=15db

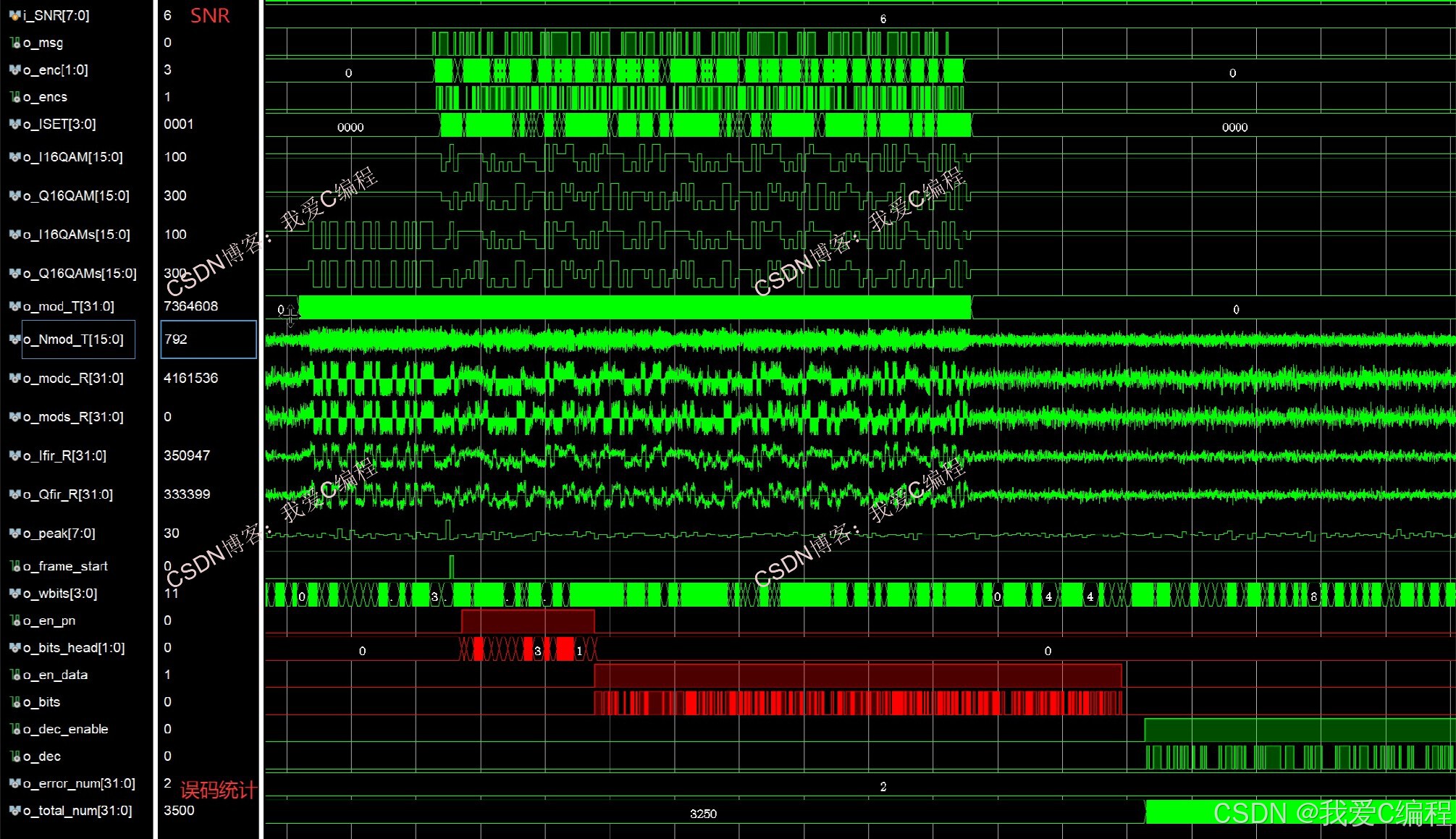

設置SNR=6db

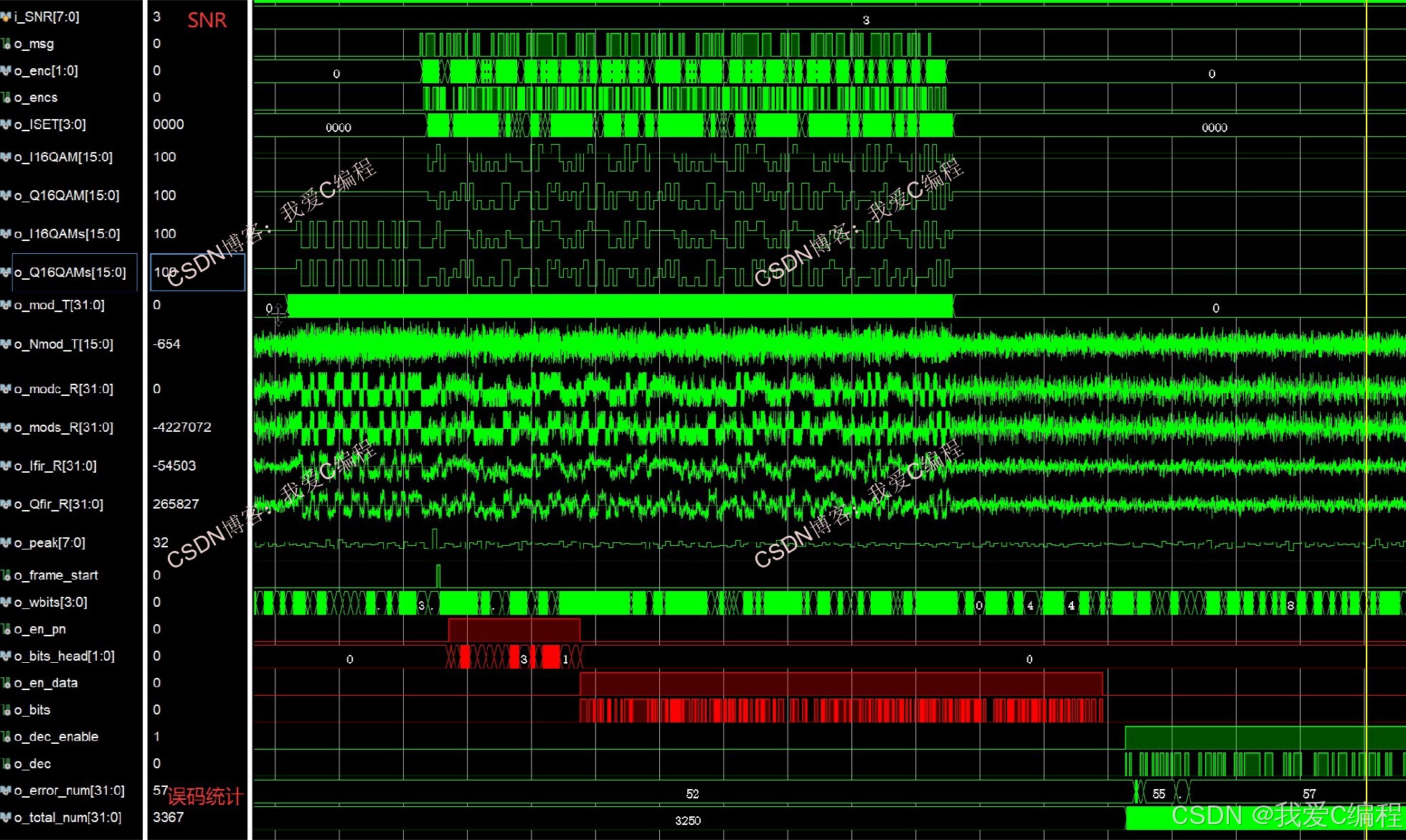

設置SNR=3db

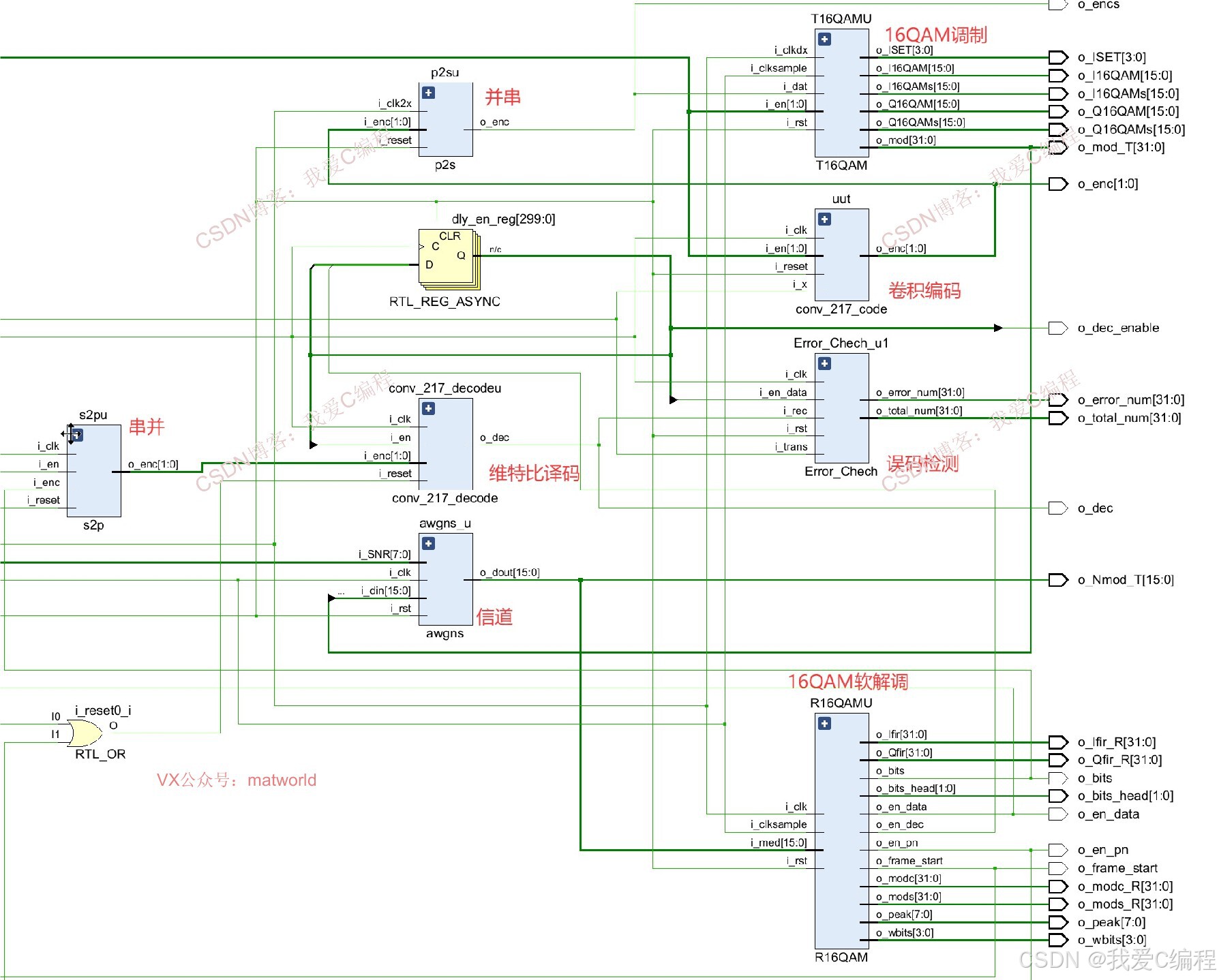

系統RTL結構圖如下圖所示:

3.算法涉及理論知識概要

整體系統結構如下所示(其中解調部分為軟解調算法實現):

3.1 16QAM調制軟解調原理

? ? ? ?16QAM是用兩路獨立的正交4ASK信號疊加而成,4ASK是用多電平信號去鍵控載波而得到的信號。它是2ASK調制的推廣,和2ASK相比,這種調制的優點在于信息傳輸速率高。正交幅度調制是利用多進制振幅鍵控(MASK)和正交載波調制相結合產生的。16進制的正交振幅調制是一種振幅相位聯合鍵控信號。16QAM的產生有2種方法:

(1)正交調幅法,它是有2路正交的四電平振幅鍵控信號疊加而成;

(2)復合相移法:它是用2路獨立的四相位移相鍵控信號疊加而成。

這里采用正交調幅法。 ? ? ??

? ? ? ?數字信號是通過FPGA的輸出端口生成的。在16QAM調制中,每個符號包含4個比特,因此需要一個4位二進制計數器來生成數字信號。計數器的輸出被映射到星座圖上的一個點,然后通過數字到模擬轉換器(DAC)轉換為模擬信號。串/并變換器將速率為Rb的二進制碼元序列分為兩路,速率為Rb/2.2-4電平變換為Rb/2的二進制碼元序列變成速率為RS=Rb/log216的4個電平信號,4電平信號與正交載波相乘,完成正交調制,兩路信號疊加后產生 16QAM信號.在兩路速率為Rb/2 的二進制碼元序列中,經 2-4電平變換器輸出為4電平信號,即M=16.經4電平正交幅度調制和疊加后,輸出16個信號狀態,即16QAM.

? ? ? 16QAM信號采取正交相干解調的方法解調,解調器首先對收到的16QAM 信號進行正交相干解調,一路與cosωct 相乘,一路與sinωct相乘。然后經過低通濾波器,低通濾波器LPF濾除乘法器產生的高頻分量,獲得有用信號,低通濾波器LPF輸出經抽樣判決可恢復出電平信號。

? ? ? ?16QAM軟解調是一種常用的數字調制解調技術,用于將接收到的16QAM調制的信號轉換為原始數據。該技術結合了16種相位和振幅的調制方式,通過軟判決算法對接收信號進行解調,16QAM軟解調的系統原理是將接收到的16QAM調制信號轉換為軟判決結果,從而恢復原始數據。軟解調是一種非硬判決的解調方法,它利用接收信號的采樣值和相位信息來判斷信號所處的調制狀態,并對其進行解調。在16QAM軟解調中,接收信號經過采樣后,通過比較采樣值和16個調制點的距離,選擇最近的調制點作為解調結果。

? ? ? ?16QAM調制將每四個比特映射到一個復數點上,共有16種相位和振幅的調制方式。每個復數點對應一個調制符號,通過軟解調,我們可以確定接收到的信號所對應的調制符號,進而推導出原始數據。

3.2 幀同步

? ? ? ?在數字通信中,信息通常是以幀為單位進行組織和傳輸的。幀同步的目的是確定每一幀的起始位置,以便接收端能夠正確地解調出每幀中的數據。

? ? ? ?設發送的幀結構為:幀同步碼 + 信息碼元序列 。幀同步碼是具有特定規律的碼序列,用于接收端識別幀的起始。

? ? ? ?幀同步的過程就是在接收序列中尋找與幀同步碼匹配的位置,一旦找到匹配位置,就確定了幀的起始位置,后續的碼元就可以按照幀結構進行正確的劃分和處理。

3.3 卷積編碼,維特比譯碼

? ? ? ? 卷積編碼是一種前向糾錯編碼方式,特別適用于無線通信和其他信道條件惡劣的應用場景。它主要通過卷積算子將信息序列映射成冗余度更高的碼字序列。典型的卷積編碼器由兩個移位寄存器和一個加法器構成,遵循一定的生成多項式進行編碼。

? ? ? ?設信息序列是 u(n),卷積編碼器的兩個生成多項式為 G1?(D) 和 G2?(D),則編碼輸出v(n) 可以表示為:

v(n)=u(n)G1?(D)+u(n?1)G2?(D)+…

此處D 是延遲算子,實際表達形式取決于具體選擇的生成多項式階數及系數。

? ? ? ?維特比譯碼是用于最大似然序列估計的一種動態規劃算法,廣泛應用于卷積編碼以及其他序列編碼的譯碼過程中。在卷積編碼中,維特比譯碼器通過構造一棵稱為“狀態轉移圖”或“trellis”的樹狀結構來尋找最有可能的原始信息序列路徑。

4.Verilog程序接口

module TOPS_16QAM(

input i_clk,

input i_clkdx,

input i_clkd2x,

input i_rst,

input signed[7:0]i_SNR,

input[1:0]i_en,

input i_dat,

//卷積編碼

output [1:0]o_enc,

output o_encs,output [3:0]o_ISET,

output signed[15:0]o_I16QAM,

output signed[15:0]o_Q16QAM,

output signed[15:0]o_I16QAMs,

output signed[15:0]o_Q16QAMs,

output signed[31:0]o_mod_T,

output signed[15:0]o_Nmod_T,output signed[31:0]o_modc_R,

output signed[31:0]o_mods_R,

output signed[31:0]o_Ifir_R,

output signed[31:0]o_Qfir_R,

output [3:0]o_wbits,

output o_bits,

output [1:0]o_bits_head,

output [7:0]o_peak,

output o_en_data,

output o_en_pn,

output o_frame_start,

output o_dec_enable,

output o_dec,

output signed[31:0]o_error_num,

output signed[31:0]o_total_num

);5.參考文獻

[1]向勁松,陳懷柔.QAM調制下基于卷積碼與累加編碼調制級聯的糾錯碼性能研究[J].半導體光電, 2023(6):924-930.

6.完整算法代碼文件獲得

完整程序見博客首頁左側或者打開本文底部

V

)

)

)

順序表算法題)

異常:從底層原理到架構級防御,老司機的實戰經驗)