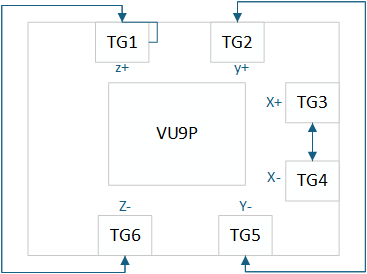

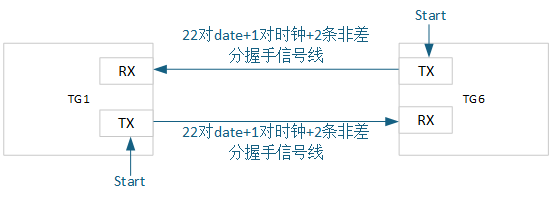

????????本次實驗的目的是通過VU9P開發板的6個TG接口,采用固定連接的方式,即X+和X-維度互聯,其框圖如下所示:

IP參數配置

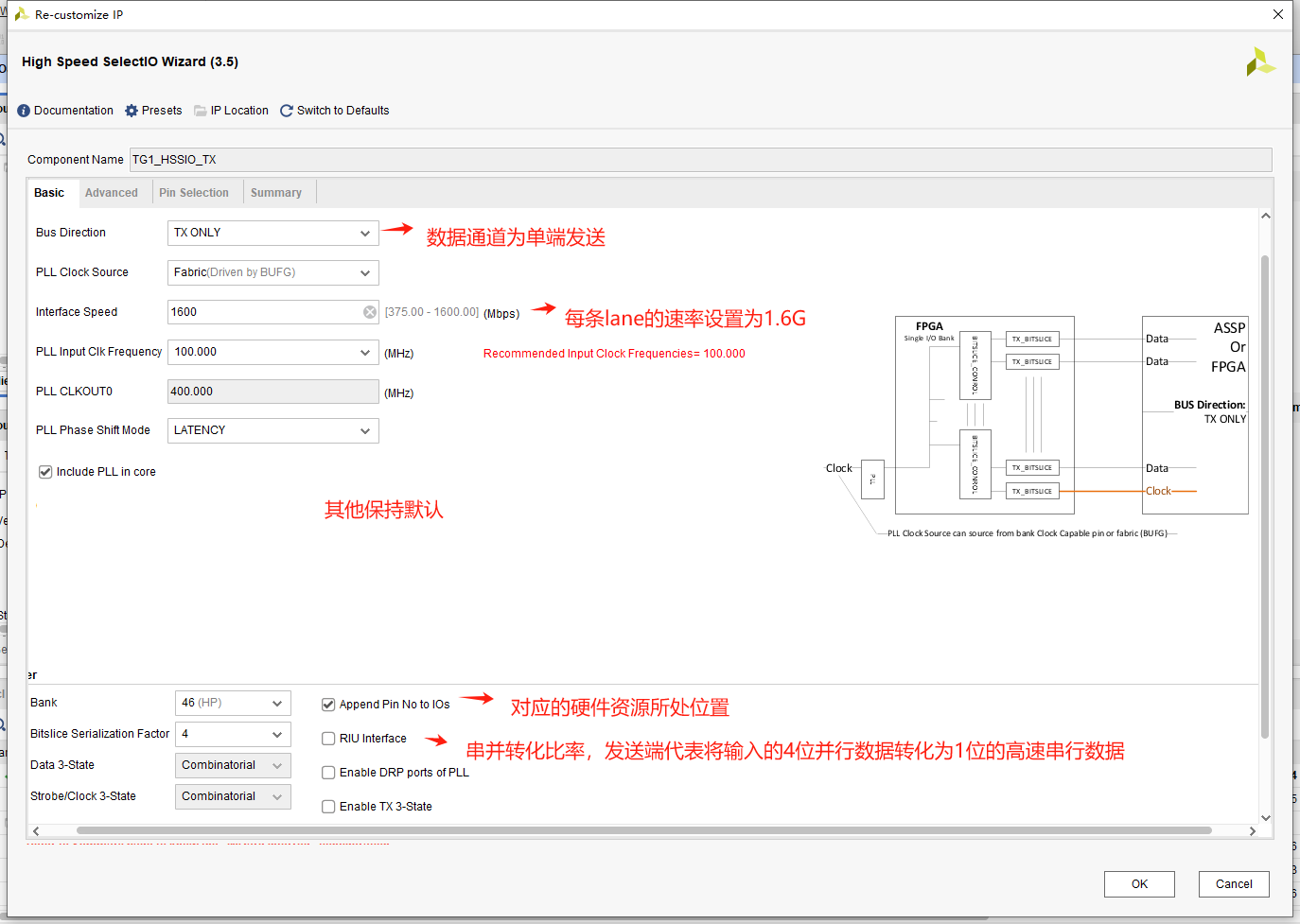

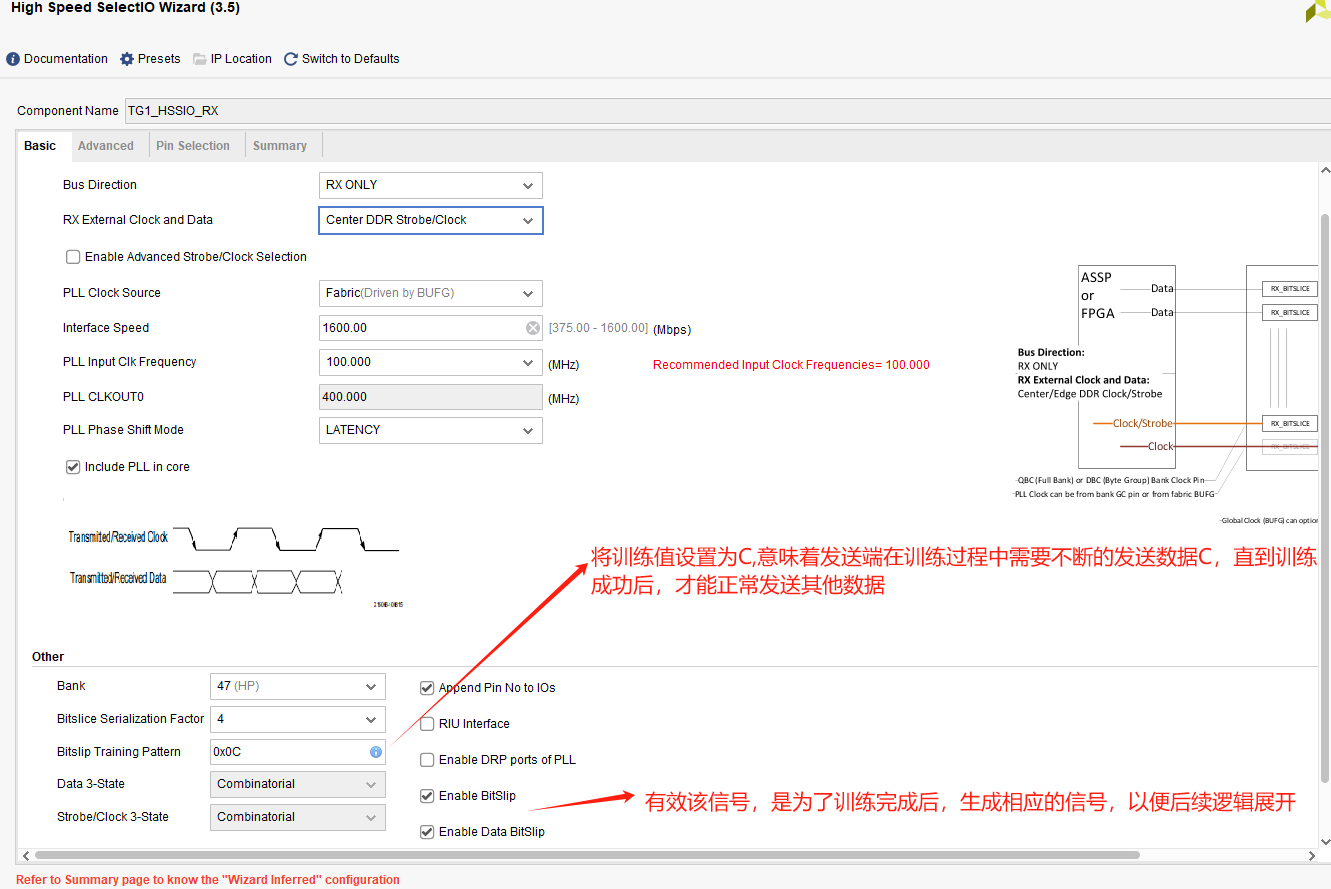

??????????通過調用High Speed?SelectIO Wizard來實現數據通路,High Speed SelectIO Wizard ip有24對數據通道,且其數據通路方向(BUS Direction)可以是 單向發送(TX ONLY),單向接受(RX ONLY),雙向分時復用(BIDIR),獨立收發(TX + RX),由于一個TG接口由48對LVDS lane 組成,其中24對用于發送數據,24對用于接收數據,所以本次實驗將例化兩個High Speed?SelectIO Wizard分別用于發送和接受,因此一個IP的數據通路方向為單向發送,另一個為單向接收。

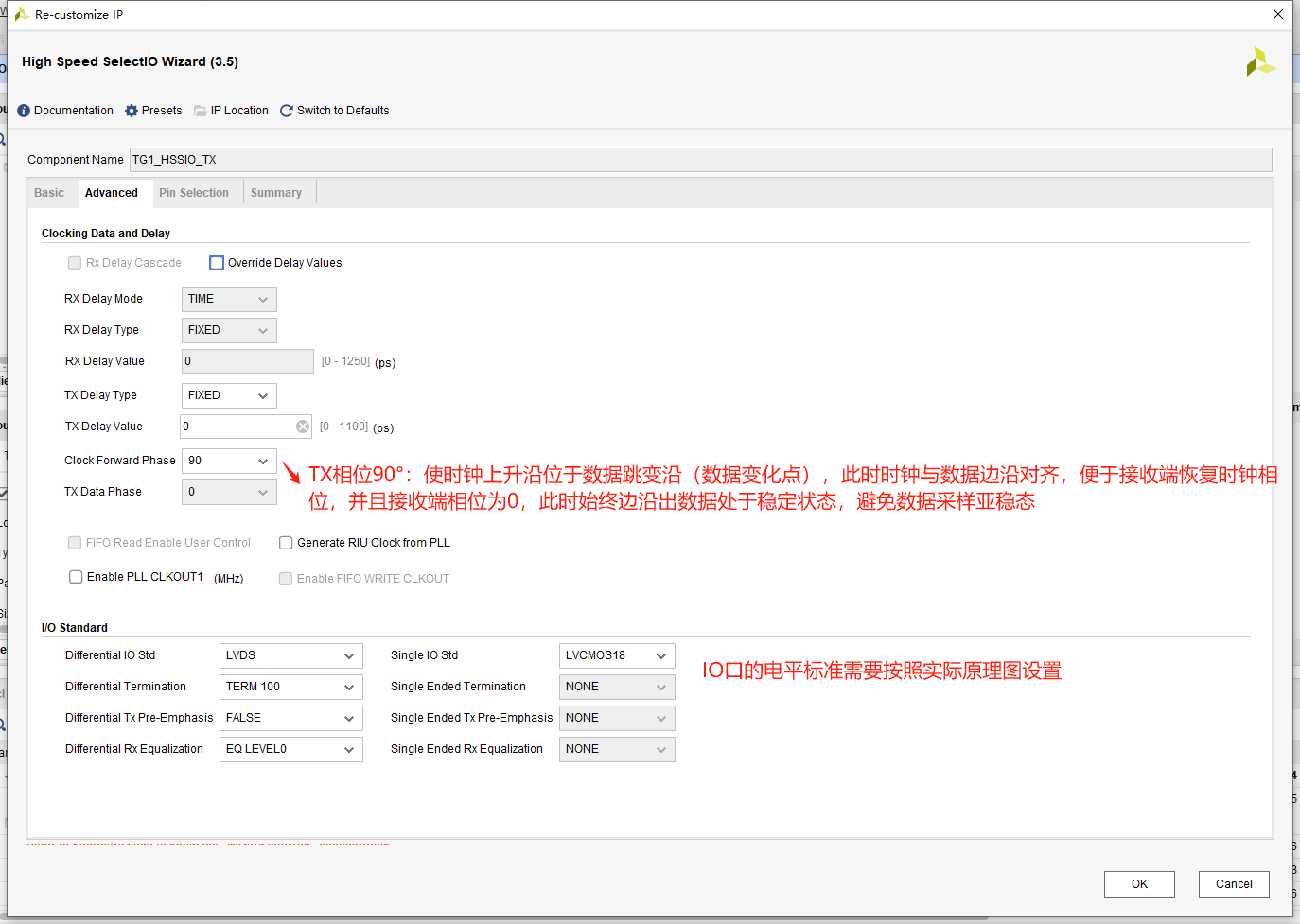

TX模塊配置

? ? ? ? 要求單條lane的速率跑到最高1600Mbps,即1.6G bps,因此其IP的TX模塊基本配置如下:

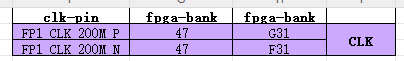

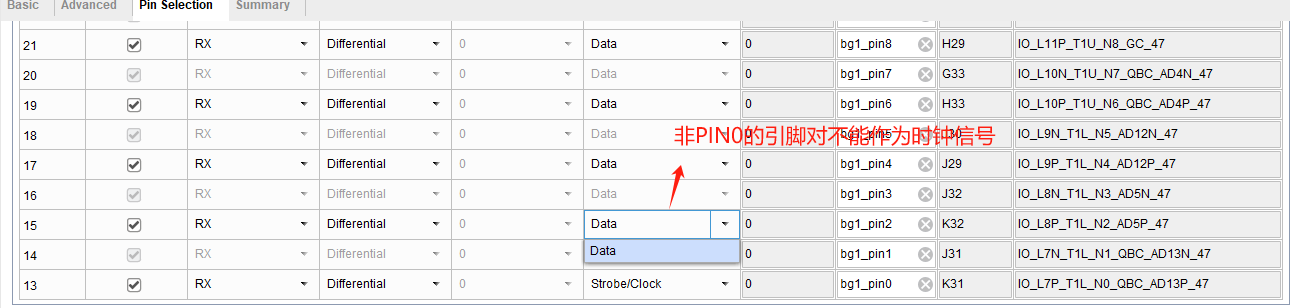

而對于Pin Selection部分的參數配置,需注意以下幾個點:

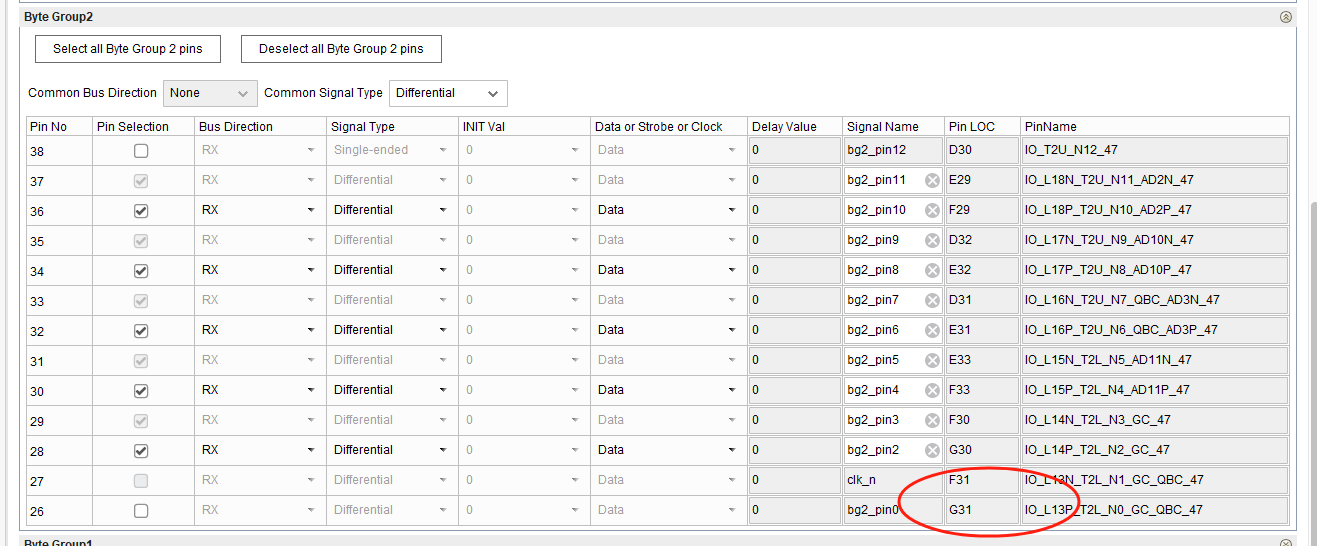

? ? ? ? 對于ip的24對LVDS lane,需要選擇一對lane作為時鐘通道,而由于引腳G31,F31是一對差分時鐘引腳,不能作為數據通道,也不能作為ip的時鐘通道,所以對于某個該引腳對所在的TG不能使用這一對lane,那么其數據通道就只能使用22對。為方便其他TG使用同一邏輯,那么都只使用22對數據lane,一對時鐘lane。

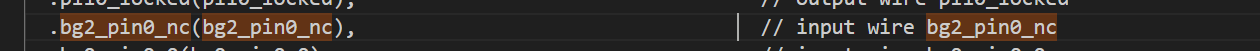

????????雖然G31所在的lane并沒有勾選,但是ip生成后,還是會生成一個特殊的信號,bg2_pin0_nc,需要將這個信號例化到頂層文件中,并且需要將引腳綁上,如此才能正確編譯。

? ? ? ? RX模塊配置之前,需要先了解一個itslip Training Pattern的原理,并了解其訓練原理。在Xilinx High Speed SelectIO Wizard IP中,當配置為??RX ONLY??模式時,??Bitslip Training Pattern??參數用于??接收端的數據邊界校準??,其核心作用是通過預定義的比特序列實現串行數據到并行數據的精確對齊。以下是詳細解析:

???Bitslip Training Pattern的作用原理??

??解決相位不確定性??

在高速串行接口中,接收端(RX)需將串行數據流轉換為并行數據,但初始采樣相位可能未對齊數據邊界(如8:1解串時,1位偏移會導致整個字節錯位)。Bitslip機制通過移位操作逐步調整數據邊界,直至檢測到預置的??Training Pattern??(訓練序列)表明對齊成功。??校準流程??

??步驟1??:發送端(TX)連續發送固定的訓練序列(如

0x0C)。??步驟2??:接收端對并行輸出數據應用

BITSLIP脈沖,每次移位1位(SDR模式)或按DDR模式交替移位。??步驟3??:當接收數據與預設的

Bitslip Training Pattern匹配時,停止移位并鎖定邊界。

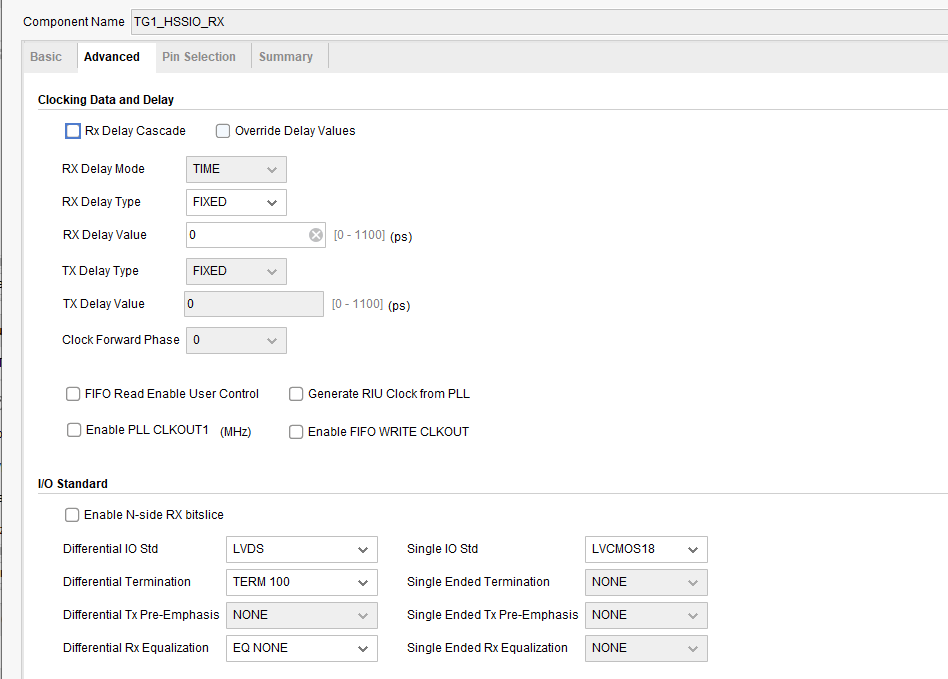

RX模塊配置

Advanced界面配置其他默認,電平配置跟隨開發板實際情況配置:

而在配置Pin seltion界面時,需注意一點,其時鐘信號只能是選擇每一個Group的PIN0位置的一對lane,所以對于時鐘信號的選擇,推薦先對RX的ip進行設置,然后根據原理圖找到TX實際與之相連的IO所對應的lane作為時鐘信號。如下圖所示:

其他中間的信號有些可選為時鐘信號,但是編譯會報錯。

設計方案

整體設計方案:

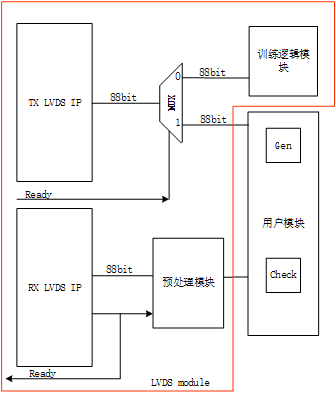

下面是LVDS_module部分的框圖:

上圖展示的是一條LVDS通路中的信號構成,其中22對data差分信號線用于傳遞數據,1對時鐘差分信號線,加上兩條非差分信號線用于傳遞握手信號。

start信號:通過vio控制,其用于TX復位標識,便于人為控制訓練的開始。

對于握手信號的解釋:

flag_to_rx? ? :發送模塊生成,傳遞到接收模塊,其定義為:當發送模塊的初始化序列完成標志rst_seq_done為1后,flag_to_rx? ?為1,發送模塊的rst_seq_done有效后變回0,其余時刻都為0。

flag_from_tx:接收來自發送模塊傳遞過來的 “flag_to_rx? ”信號。且需要對其進行上升沿下降沿定位。

????????當其上升沿出現,代表與之連接的TX模塊的IP復位完成,并且該上升沿可以作為RX IP的復位信號標志。及其上升沿出現后,對RX IP復位有效。

????????而下降沿出現,代表與之連接的RX模塊的IP復位完成,那么該信號可作為發送數據包發送訓練數據0x0C和正常數據的一個分割點,出現之前一直發0x0C,出現之后正常發數據。

TX模塊信號解析

對于TX模塊的IP的其他信號需要注意,其中需要注意的一些信號:

1. 控制與狀態信號

| ??信號名?? | ??方向?? | ??位寬?? | ??功能說明?? |

|---|---|---|---|

rst | Input | 1-bit | 全局復位信號(高有效) |

riu_clk | Input | 1-bit | RIU(Reconfigurable I/O)配置接口時鐘(典型值100MHz) |

pll0_locked | Output | 1-bit | PLL鎖定狀態指示(1=鎖定,0=失鎖) |

rst_seq_done | Output | 1-bit | 初始化序列完成標志(1=就緒) |

vtc_rdy_bscX | Output | 1-bit*8 | 各Bank的VTU(Voltage/Timing Unit)校準完成信號(X=0~7) |

en_vtc_bscX | Input | 1-bit*8 | VTU校準使能信號(需拉高以激活延時控制) |

dly_rdy_bscX | Output | 1-bit*7 | Bank內延時單元校準完成信號(索引1~7) |

TX的ip操作流程:上電后拉高en_vtc_bscX?→ 等待vtc_rdy_bscX和dly_rdy_bscX變高 → 最終rst_seq_done有效 → 開始發送數據。所以一般將en_vtc_bscX直接置為1。

2. 時鐘管理信號???

| ??信號名?? | ??方向?? | ??功能說明?? |

|---|---|---|

clk | Input | 用戶邏輯數據時鐘(頻率需匹配PLL設置) |

shared_pll0_clkoutphy_out | Output | PLL輸出的高速串行時鐘(連接至IO引腳或下一級IP) |

pll0_clkout0 | Output | PLL分頻后的并行參考時鐘(用戶邏輯同步時鐘) |

3. 數據通道信號(按Bank分組)??

| ??信號格式?? | ??方向?? | ??位寬?? | ??功能說明?? |

|---|---|---|---|

bgX_pinY_Z | Output | 1-bit | Bank X(0~3)的引腳 Y(0~11)輸出數據(直連FPGA物理引腳) |

data_from_fabric_bgX_pinY_Z | Input | 4-bit | ??用戶邏輯輸入數據??(與bgX_pinY_Z關聯,發送時IP將4位并轉1位串行) |

??數據流示例??(Bank 0 Pin 0):

用戶邏輯 →?data_from_fabric_bg0_pin0_0[3:0]?→ HSSIO IP → 串行化為單比特流 →?bg0_pin0_0輸出

下面代碼塊為High Speed SelectIO Wizard設置為單向發送模塊生成的.veo文件內容:

TG1_HSSIO_TX your_instance_name (.vtc_rdy_bsc0(vtc_rdy_bsc0), // output wire vtc_rdy_bsc0.en_vtc_bsc0(en_vtc_bsc0), // input wire en_vtc_bsc0.vtc_rdy_bsc1(vtc_rdy_bsc1), // output wire vtc_rdy_bsc1.en_vtc_bsc1(en_vtc_bsc1), // input wire en_vtc_bsc1.vtc_rdy_bsc2(vtc_rdy_bsc2), // output wire vtc_rdy_bsc2.en_vtc_bsc2(en_vtc_bsc2), // input wire en_vtc_bsc2.vtc_rdy_bsc3(vtc_rdy_bsc3), // output wire vtc_rdy_bsc3.en_vtc_bsc3(en_vtc_bsc3), // input wire en_vtc_bsc3.vtc_rdy_bsc4(vtc_rdy_bsc4), // output wire vtc_rdy_bsc4.en_vtc_bsc4(en_vtc_bsc4), // input wire en_vtc_bsc4.vtc_rdy_bsc5(vtc_rdy_bsc5), // output wire vtc_rdy_bsc5.en_vtc_bsc5(en_vtc_bsc5), // input wire en_vtc_bsc5.vtc_rdy_bsc6(vtc_rdy_bsc6), // output wire vtc_rdy_bsc6.en_vtc_bsc6(en_vtc_bsc6), // input wire en_vtc_bsc6.vtc_rdy_bsc7(vtc_rdy_bsc7), // output wire vtc_rdy_bsc7.en_vtc_bsc7(en_vtc_bsc7), // input wire en_vtc_bsc7.dly_rdy_bsc0(dly_rdy_bsc0), // output wire dly_rdy_bsc0.dly_rdy_bsc1(dly_rdy_bsc1), // output wire dly_rdy_bsc1.dly_rdy_bsc2(dly_rdy_bsc2), // output wire dly_rdy_bsc2.dly_rdy_bsc3(dly_rdy_bsc3), // output wire dly_rdy_bsc3.dly_rdy_bsc4(dly_rdy_bsc4), // output wire dly_rdy_bsc4.dly_rdy_bsc5(dly_rdy_bsc5), // output wire dly_rdy_bsc5.dly_rdy_bsc6(dly_rdy_bsc6), // output wire dly_rdy_bsc6.dly_rdy_bsc7(dly_rdy_bsc7), // output wire dly_rdy_bsc7.rst_seq_done(rst_seq_done), // output wire rst_seq_done.shared_pll0_clkoutphy_out(shared_pll0_clkoutphy_out), // output wire shared_pll0_clkoutphy_out.pll0_clkout0(pll0_clkout0), // output wire pll0_clkout0.rst(rst), // input wire rst.clk(clk), // input wire clk.riu_clk(riu_clk), // input wire riu_clk.pll0_locked(pll0_locked), // output wire pll0_locked.bg0_pin0_0(bg0_pin0_0), // output wire bg0_pin0_0.data_from_fabric_bg0_pin0_0(data_from_fabric_bg0_pin0_0), // input wire [3 : 0] data_from_fabric_bg0_pin0_0.bg0_pin1_1(bg0_pin1_1), // output wire bg0_pin1_1.bg0_pin2_2(bg0_pin2_2), // output wire bg0_pin2_2.data_from_fabric_bg0_pin2_2(data_from_fabric_bg0_pin2_2), // input wire [3 : 0] data_from_fabric_bg0_pin2_2.bg0_pin3_3(bg0_pin3_3), // output wire bg0_pin3_3.bg0_pin4_4(bg0_pin4_4), // output wire bg0_pin4_4.data_from_fabric_bg0_pin4_4(data_from_fabric_bg0_pin4_4), // input wire [3 : 0] data_from_fabric_bg0_pin4_4.bg0_pin5_5(bg0_pin5_5), // output wire bg0_pin5_5.bg0_pin6_6(bg0_pin6_6), // output wire bg0_pin6_6.data_from_fabric_bg0_pin6_6(data_from_fabric_bg0_pin6_6), // input wire [3 : 0] data_from_fabric_bg0_pin6_6.bg0_pin7_7(bg0_pin7_7), // output wire bg0_pin7_7.bg0_pin8_8(bg0_pin8_8), // output wire bg0_pin8_8.data_from_fabric_bg0_pin8_8(data_from_fabric_bg0_pin8_8), // input wire [3 : 0] data_from_fabric_bg0_pin8_8.bg0_pin9_9(bg0_pin9_9), // output wire bg0_pin9_9.bg0_pin10_10(bg0_pin10_10), // output wire bg0_pin10_10.data_from_fabric_bg0_pin10_10(data_from_fabric_bg0_pin10_10), // input wire [3 : 0] data_from_fabric_bg0_pin10_10.bg0_pin11_11(bg0_pin11_11), // output wire bg0_pin11_11.bg1_pin0_13(bg1_pin0_13), // output wire bg1_pin0_13.data_from_fabric_bg1_pin0_13(data_from_fabric_bg1_pin0_13), // input wire [3 : 0] data_from_fabric_bg1_pin0_13.bg1_pin1_14(bg1_pin1_14), // output wire bg1_pin1_14.bg1_pin2_15(bg1_pin2_15), // output wire bg1_pin2_15.data_from_fabric_bg1_pin2_15(data_from_fabric_bg1_pin2_15), // input wire [3 : 0] data_from_fabric_bg1_pin2_15.bg1_pin3_16(bg1_pin3_16), // output wire bg1_pin3_16.bg1_pin4_17(bg1_pin4_17), // output wire bg1_pin4_17.data_from_fabric_bg1_pin4_17(data_from_fabric_bg1_pin4_17), // input wire [3 : 0] data_from_fabric_bg1_pin4_17.bg1_pin5_18(bg1_pin5_18), // output wire bg1_pin5_18.bg1_pin6_19(bg1_pin6_19), // output wire bg1_pin6_19.data_from_fabric_bg1_pin6_19(data_from_fabric_bg1_pin6_19), // input wire [3 : 0] data_from_fabric_bg1_pin6_19.bg1_pin7_20(bg1_pin7_20), // output wire bg1_pin7_20.bg1_pin8_21(bg1_pin8_21), // output wire bg1_pin8_21.data_from_fabric_bg1_pin8_21(data_from_fabric_bg1_pin8_21), // input wire [3 : 0] data_from_fabric_bg1_pin8_21.bg1_pin9_22(bg1_pin9_22), // output wire bg1_pin9_22.bg1_pin10_23(bg1_pin10_23), // output wire bg1_pin10_23.data_from_fabric_bg1_pin10_23(data_from_fabric_bg1_pin10_23), // input wire [3 : 0] data_from_fabric_bg1_pin10_23.bg1_pin11_24(bg1_pin11_24), // output wire bg1_pin11_24.bg2_pin2_28(bg2_pin2_28), // output wire bg2_pin2_28.data_from_fabric_bg2_pin2_28(data_from_fabric_bg2_pin2_28), // input wire [3 : 0] data_from_fabric_bg2_pin2_28.bg2_pin3_29(bg2_pin3_29), // output wire bg2_pin3_29.bg2_pin4_30(bg2_pin4_30), // output wire bg2_pin4_30.data_from_fabric_bg2_pin4_30(data_from_fabric_bg2_pin4_30), // input wire [3 : 0] data_from_fabric_bg2_pin4_30.bg2_pin5_31(bg2_pin5_31), // output wire bg2_pin5_31.bg2_pin6_32(bg2_pin6_32), // output wire bg2_pin6_32.data_from_fabric_bg2_pin6_32(data_from_fabric_bg2_pin6_32), // input wire [3 : 0] data_from_fabric_bg2_pin6_32.bg2_pin7_33(bg2_pin7_33), // output wire bg2_pin7_33.bg2_pin8_34(bg2_pin8_34), // output wire bg2_pin8_34.data_from_fabric_bg2_pin8_34(data_from_fabric_bg2_pin8_34), // input wire [3 : 0] data_from_fabric_bg2_pin8_34.bg2_pin9_35(bg2_pin9_35), // output wire bg2_pin9_35.bg2_pin10_36(bg2_pin10_36), // output wire bg2_pin10_36.data_from_fabric_bg2_pin10_36(data_from_fabric_bg2_pin10_36), // input wire [3 : 0] data_from_fabric_bg2_pin10_36.bg2_pin11_37(bg2_pin11_37), // output wire bg2_pin11_37.bg3_pin0_39(bg3_pin0_39), // output wire bg3_pin0_39.data_from_fabric_bg3_pin0_39(data_from_fabric_bg3_pin0_39), // input wire [3 : 0] data_from_fabric_bg3_pin0_39.bg3_pin1_40(bg3_pin1_40), // output wire bg3_pin1_40.bg3_pin2_41(bg3_pin2_41), // output wire bg3_pin2_41.data_from_fabric_bg3_pin2_41(data_from_fabric_bg3_pin2_41), // input wire [3 : 0] data_from_fabric_bg3_pin2_41.bg3_pin3_42(bg3_pin3_42), // output wire bg3_pin3_42.bg3_pin4_43(bg3_pin4_43), // output wire bg3_pin4_43.data_from_fabric_bg3_pin4_43(data_from_fabric_bg3_pin4_43), // input wire [3 : 0] data_from_fabric_bg3_pin4_43.bg3_pin5_44(bg3_pin5_44), // output wire bg3_pin5_44.bg3_pin6_45(bg3_pin6_45), // output wire bg3_pin6_45.data_from_fabric_bg3_pin6_45(data_from_fabric_bg3_pin6_45), // input wire [3 : 0] data_from_fabric_bg3_pin6_45.bg3_pin7_46(bg3_pin7_46), // output wire bg3_pin7_46.bg3_pin8_47(bg3_pin8_47), // output wire bg3_pin8_47.data_from_fabric_bg3_pin8_47(data_from_fabric_bg3_pin8_47), // input wire [3 : 0] data_from_fabric_bg3_pin8_47.bg3_pin9_48(bg3_pin9_48), // output wire bg3_pin9_48.bg3_pin10_49(bg3_pin10_49), // output wire bg3_pin10_49.data_from_fabric_bg3_pin10_49(data_from_fabric_bg3_pin10_49), // input wire [3 : 0] data_from_fabric_bg3_pin10_49.bg3_pin11_50(bg3_pin11_50) // output wire bg3_pin11_50

);RX模塊信號解析

??1. 控制與狀態信號??

| ??信號名?? | ??方向?? | ??功能說明?? |

|---|---|---|

rst | Input | 全局復位信號(高有效) |

riu_clk | Input | RIU配置接口時鐘(100-200MHz) |

pll0_locked | Output | 內置PLL鎖定狀態(1=鎖定) |

rst_seq_done | Output | RX初始化序列完成標志(1=就緒) |

vtc_rdy_bscX | Output | Bank X的VTU時序單元校準完成信號 |

en_vtc_bscX | Input | Bank X的VTU校準使能信號(需拉高,例化直接置1) |

dly_rdy_bscX | Output | Bank X的IDELAY延時單元校準完成信號 |

???2. Bitslip數據對齊控制??

| ??信號名?? | ??功能說明?? |

|---|---|

start_bitslip | ??輸入??:啟動Bitslip校準序列(脈沖觸發) |

rx_bitslip_sync_done | ??輸出??:所有通道Bitslip對齊完成標志 |

bitslip_error_XX | ??輸出??:通道XX的對齊錯誤指示(1=檢測到錯誤,如超時或訓練序列不匹配) |

fifo_rd_data_valid | ??輸出??:解串后的并行數據有效標志 |

??Bitslip工作流程??:

拉高start_bitslip?→ IP自動發送訓練序列 → 移位檢測匹配 →?rx_bitslip_sync_done變高

若超時未對齊 →?bitslip_error_XX報錯本次實驗中,由于在配置RX的時候,

Bitslip Training Pattern參數配置的是0x0C,意味著RX的IP在“拉高start_bitslip?→ IP自動發送訓練序列 → 移位檢測匹配 →?rx_bitslip_sync_done變高”這個流程中,從外界也就是TX模塊傳遞進來的數據要一直穩定的為C,直到訓練結束后,才能發送其他數據。

???3. 數據時鐘管理??

| ??信號名?? | ??方向?? | ??功能說明?? |

|---|---|---|

clk | Input | 用戶邏輯參考時鐘(需與PLL輸入同源) |

shared_pll0_clkoutphy_out | Output | 高速串行采樣時鐘(供其他模塊使用) |

pll0_clkout0 | Output | PLL生成的并行輸出時鐘(用于同步data_to_fabric_*) |

fifo_rd_clk_XX | Input | 通道XX的FIFO讀取時鐘(用戶自定義) |

???4. 數據通道信號(按Bank分組)??

| ??信號格式?? | ??方向?? | ??位寬?? | ??功能說明?? |

|---|---|---|---|

bgX_pinY_Z | ??Input?? | 1-bit | Bank X的引腳Y輸入數據(直連FPGA物理引腳) |

data_to_fabric_bgX_pinY_Z | Output | 4-bit | ??解串后的并行數據??(ISERDES將1位串行數據轉換為4位并行輸出至用戶邏輯) |

??數據流示例??(Bank 0 Pin 0):

外部引腳輸入 →?bg0_pin0_0?→ ISERDES解串 →?data_to_fabric_bg0_pin0_0[3:0]?→ 用戶邏輯

???5. FIFO狀態信號??

| ??信號名?? | ??方向?? | ??功能說明?? |

|---|---|---|

fifo_empty_XX | Output | 通道XX的FIFO空標志(1=無數據可讀) |

fifo_rd_data_valid | Output | FIFO讀取數據有效標志 |

下面代碼塊為High Speed SelectIO Wizard設置為單向接收模塊生成的.veo文件內容:

TG1_HSSIO_RX your_instance_name (.fifo_rd_data_valid(fifo_rd_data_valid), // output wire fifo_rd_data_valid.start_bitslip(start_bitslip), // input wire start_bitslip.rx_bitslip_sync_done(rx_bitslip_sync_done), // output wire rx_bitslip_sync_done.bitslip_error_0(bitslip_error_0), // output wire bitslip_error_0.bitslip_error_2(bitslip_error_2), // output wire bitslip_error_2.bitslip_error_4(bitslip_error_4), // output wire bitslip_error_4.bitslip_error_6(bitslip_error_6), // output wire bitslip_error_6.bitslip_error_8(bitslip_error_8), // output wire bitslip_error_8.bitslip_error_10(bitslip_error_10), // output wire bitslip_error_10.bitslip_error_13(bitslip_error_13), // output wire bitslip_error_13.bitslip_error_15(bitslip_error_15), // output wire bitslip_error_15.bitslip_error_17(bitslip_error_17), // output wire bitslip_error_17.bitslip_error_19(bitslip_error_19), // output wire bitslip_error_19.bitslip_error_21(bitslip_error_21), // output wire bitslip_error_21.bitslip_error_23(bitslip_error_23), // output wire bitslip_error_23.bitslip_error_28(bitslip_error_28), // output wire bitslip_error_28.bitslip_error_30(bitslip_error_30), // output wire bitslip_error_30.bitslip_error_32(bitslip_error_32), // output wire bitslip_error_32.bitslip_error_34(bitslip_error_34), // output wire bitslip_error_34.bitslip_error_36(bitslip_error_36), // output wire bitslip_error_36.bitslip_error_39(bitslip_error_39), // output wire bitslip_error_39.bitslip_error_41(bitslip_error_41), // output wire bitslip_error_41.bitslip_error_43(bitslip_error_43), // output wire bitslip_error_43.bitslip_error_45(bitslip_error_45), // output wire bitslip_error_45.bitslip_error_47(bitslip_error_47), // output wire bitslip_error_47.bitslip_error_49(bitslip_error_49), // output wire bitslip_error_49.fifo_rd_clk_0(fifo_rd_clk_0), // input wire fifo_rd_clk_0.fifo_rd_clk_2(fifo_rd_clk_2), // input wire fifo_rd_clk_2.fifo_rd_clk_4(fifo_rd_clk_4), // input wire fifo_rd_clk_4.fifo_rd_clk_6(fifo_rd_clk_6), // input wire fifo_rd_clk_6.fifo_rd_clk_8(fifo_rd_clk_8), // input wire fifo_rd_clk_8.fifo_rd_clk_10(fifo_rd_clk_10), // input wire fifo_rd_clk_10.fifo_rd_clk_13(fifo_rd_clk_13), // input wire fifo_rd_clk_13.fifo_rd_clk_15(fifo_rd_clk_15), // input wire fifo_rd_clk_15.fifo_rd_clk_17(fifo_rd_clk_17), // input wire fifo_rd_clk_17.fifo_rd_clk_19(fifo_rd_clk_19), // input wire fifo_rd_clk_19.fifo_rd_clk_21(fifo_rd_clk_21), // input wire fifo_rd_clk_21.fifo_rd_clk_23(fifo_rd_clk_23), // input wire fifo_rd_clk_23.fifo_rd_clk_28(fifo_rd_clk_28), // input wire fifo_rd_clk_28.fifo_rd_clk_30(fifo_rd_clk_30), // input wire fifo_rd_clk_30.fifo_rd_clk_32(fifo_rd_clk_32), // input wire fifo_rd_clk_32.fifo_rd_clk_34(fifo_rd_clk_34), // input wire fifo_rd_clk_34.fifo_rd_clk_36(fifo_rd_clk_36), // input wire fifo_rd_clk_36.fifo_rd_clk_39(fifo_rd_clk_39), // input wire fifo_rd_clk_39.fifo_rd_clk_41(fifo_rd_clk_41), // input wire fifo_rd_clk_41.fifo_rd_clk_43(fifo_rd_clk_43), // input wire fifo_rd_clk_43.fifo_rd_clk_45(fifo_rd_clk_45), // input wire fifo_rd_clk_45.fifo_rd_clk_47(fifo_rd_clk_47), // input wire fifo_rd_clk_47.fifo_rd_clk_49(fifo_rd_clk_49), // input wire fifo_rd_clk_49.fifo_empty_0(fifo_empty_0), // output wire fifo_empty_0.fifo_empty_2(fifo_empty_2), // output wire fifo_empty_2.fifo_empty_4(fifo_empty_4), // output wire fifo_empty_4.fifo_empty_6(fifo_empty_6), // output wire fifo_empty_6.fifo_empty_8(fifo_empty_8), // output wire fifo_empty_8.fifo_empty_10(fifo_empty_10), // output wire fifo_empty_10.fifo_empty_13(fifo_empty_13), // output wire fifo_empty_13.fifo_empty_15(fifo_empty_15), // output wire fifo_empty_15.fifo_empty_17(fifo_empty_17), // output wire fifo_empty_17.fifo_empty_19(fifo_empty_19), // output wire fifo_empty_19.fifo_empty_21(fifo_empty_21), // output wire fifo_empty_21.fifo_empty_23(fifo_empty_23), // output wire fifo_empty_23.fifo_empty_28(fifo_empty_28), // output wire fifo_empty_28.fifo_empty_30(fifo_empty_30), // output wire fifo_empty_30.fifo_empty_32(fifo_empty_32), // output wire fifo_empty_32.fifo_empty_34(fifo_empty_34), // output wire fifo_empty_34.fifo_empty_36(fifo_empty_36), // output wire fifo_empty_36.fifo_empty_39(fifo_empty_39), // output wire fifo_empty_39.fifo_empty_41(fifo_empty_41), // output wire fifo_empty_41.fifo_empty_43(fifo_empty_43), // output wire fifo_empty_43.fifo_empty_45(fifo_empty_45), // output wire fifo_empty_45.fifo_empty_47(fifo_empty_47), // output wire fifo_empty_47.fifo_empty_49(fifo_empty_49), // output wire fifo_empty_49.vtc_rdy_bsc0(vtc_rdy_bsc0), // output wire vtc_rdy_bsc0.en_vtc_bsc0(en_vtc_bsc0), // input wire en_vtc_bsc0.vtc_rdy_bsc1(vtc_rdy_bsc1), // output wire vtc_rdy_bsc1.en_vtc_bsc1(en_vtc_bsc1), // input wire en_vtc_bsc1.vtc_rdy_bsc2(vtc_rdy_bsc2), // output wire vtc_rdy_bsc2.en_vtc_bsc2(en_vtc_bsc2), // input wire en_vtc_bsc2.vtc_rdy_bsc3(vtc_rdy_bsc3), // output wire vtc_rdy_bsc3.en_vtc_bsc3(en_vtc_bsc3), // input wire en_vtc_bsc3.vtc_rdy_bsc4(vtc_rdy_bsc4), // output wire vtc_rdy_bsc4.en_vtc_bsc4(en_vtc_bsc4), // input wire en_vtc_bsc4.vtc_rdy_bsc5(vtc_rdy_bsc5), // output wire vtc_rdy_bsc5.en_vtc_bsc5(en_vtc_bsc5), // input wire en_vtc_bsc5.vtc_rdy_bsc6(vtc_rdy_bsc6), // output wire vtc_rdy_bsc6.en_vtc_bsc6(en_vtc_bsc6), // input wire en_vtc_bsc6.vtc_rdy_bsc7(vtc_rdy_bsc7), // output wire vtc_rdy_bsc7.en_vtc_bsc7(en_vtc_bsc7), // input wire en_vtc_bsc7.dly_rdy_bsc0(dly_rdy_bsc0), // output wire dly_rdy_bsc0.dly_rdy_bsc1(dly_rdy_bsc1), // output wire dly_rdy_bsc1.dly_rdy_bsc2(dly_rdy_bsc2), // output wire dly_rdy_bsc2.dly_rdy_bsc3(dly_rdy_bsc3), // output wire dly_rdy_bsc3.dly_rdy_bsc4(dly_rdy_bsc4), // output wire dly_rdy_bsc4.dly_rdy_bsc5(dly_rdy_bsc5), // output wire dly_rdy_bsc5.dly_rdy_bsc6(dly_rdy_bsc6), // output wire dly_rdy_bsc6.dly_rdy_bsc7(dly_rdy_bsc7), // output wire dly_rdy_bsc7.rst_seq_done(rst_seq_done), // output wire rst_seq_done.shared_pll0_clkoutphy_out(shared_pll0_clkoutphy_out), // output wire shared_pll0_clkoutphy_out.pll0_clkout0(pll0_clkout0), // output wire pll0_clkout0.rst(rst), // input wire rst.clk(clk), // input wire clk.riu_clk(riu_clk), // input wire riu_clk.pll0_locked(pll0_locked), // output wire pll0_locked.bg2_pin0_nc(bg2_pin0_nc), // input wire bg2_pin0_nc.bg0_pin0_0(bg0_pin0_0), // input wire bg0_pin0_0.data_to_fabric_bg0_pin0_0(data_to_fabric_bg0_pin0_0), // output wire [3 : 0] data_to_fabric_bg0_pin0_0.bg0_pin1_1(bg0_pin1_1), // input wire bg0_pin1_1.bg0_pin2_2(bg0_pin2_2), // input wire bg0_pin2_2.data_to_fabric_bg0_pin2_2(data_to_fabric_bg0_pin2_2), // output wire [3 : 0] data_to_fabric_bg0_pin2_2.bg0_pin3_3(bg0_pin3_3), // input wire bg0_pin3_3.bg0_pin4_4(bg0_pin4_4), // input wire bg0_pin4_4.data_to_fabric_bg0_pin4_4(data_to_fabric_bg0_pin4_4), // output wire [3 : 0] data_to_fabric_bg0_pin4_4.bg0_pin5_5(bg0_pin5_5), // input wire bg0_pin5_5.bg0_pin6_6(bg0_pin6_6), // input wire bg0_pin6_6.data_to_fabric_bg0_pin6_6(data_to_fabric_bg0_pin6_6), // output wire [3 : 0] data_to_fabric_bg0_pin6_6.bg0_pin7_7(bg0_pin7_7), // input wire bg0_pin7_7.bg0_pin8_8(bg0_pin8_8), // input wire bg0_pin8_8.data_to_fabric_bg0_pin8_8(data_to_fabric_bg0_pin8_8), // output wire [3 : 0] data_to_fabric_bg0_pin8_8.bg0_pin9_9(bg0_pin9_9), // input wire bg0_pin9_9.bg0_pin10_10(bg0_pin10_10), // input wire bg0_pin10_10.data_to_fabric_bg0_pin10_10(data_to_fabric_bg0_pin10_10), // output wire [3 : 0] data_to_fabric_bg0_pin10_10.bg0_pin11_11(bg0_pin11_11), // input wire bg0_pin11_11.bg1_pin0_13(bg1_pin0_13), // input wire bg1_pin0_13.data_to_fabric_bg1_pin0_13(data_to_fabric_bg1_pin0_13), // output wire [3 : 0] data_to_fabric_bg1_pin0_13.bg1_pin1_14(bg1_pin1_14), // input wire bg1_pin1_14.bg1_pin2_15(bg1_pin2_15), // input wire bg1_pin2_15.data_to_fabric_bg1_pin2_15(data_to_fabric_bg1_pin2_15), // output wire [3 : 0] data_to_fabric_bg1_pin2_15.bg1_pin3_16(bg1_pin3_16), // input wire bg1_pin3_16.bg1_pin4_17(bg1_pin4_17), // input wire bg1_pin4_17.data_to_fabric_bg1_pin4_17(data_to_fabric_bg1_pin4_17), // output wire [3 : 0] data_to_fabric_bg1_pin4_17.bg1_pin5_18(bg1_pin5_18), // input wire bg1_pin5_18.bg1_pin6_19(bg1_pin6_19), // input wire bg1_pin6_19.data_to_fabric_bg1_pin6_19(data_to_fabric_bg1_pin6_19), // output wire [3 : 0] data_to_fabric_bg1_pin6_19.bg1_pin7_20(bg1_pin7_20), // input wire bg1_pin7_20.bg1_pin8_21(bg1_pin8_21), // input wire bg1_pin8_21.data_to_fabric_bg1_pin8_21(data_to_fabric_bg1_pin8_21), // output wire [3 : 0] data_to_fabric_bg1_pin8_21.bg1_pin9_22(bg1_pin9_22), // input wire bg1_pin9_22.bg1_pin10_23(bg1_pin10_23), // input wire bg1_pin10_23.data_to_fabric_bg1_pin10_23(data_to_fabric_bg1_pin10_23), // output wire [3 : 0] data_to_fabric_bg1_pin10_23.bg1_pin11_24(bg1_pin11_24), // input wire bg1_pin11_24.bg2_pin2_28(bg2_pin2_28), // input wire bg2_pin2_28.data_to_fabric_bg2_pin2_28(data_to_fabric_bg2_pin2_28), // output wire [3 : 0] data_to_fabric_bg2_pin2_28.bg2_pin3_29(bg2_pin3_29), // input wire bg2_pin3_29.bg2_pin4_30(bg2_pin4_30), // input wire bg2_pin4_30.data_to_fabric_bg2_pin4_30(data_to_fabric_bg2_pin4_30), // output wire [3 : 0] data_to_fabric_bg2_pin4_30.bg2_pin5_31(bg2_pin5_31), // input wire bg2_pin5_31.bg2_pin6_32(bg2_pin6_32), // input wire bg2_pin6_32.data_to_fabric_bg2_pin6_32(data_to_fabric_bg2_pin6_32), // output wire [3 : 0] data_to_fabric_bg2_pin6_32.bg2_pin7_33(bg2_pin7_33), // input wire bg2_pin7_33.bg2_pin8_34(bg2_pin8_34), // input wire bg2_pin8_34.data_to_fabric_bg2_pin8_34(data_to_fabric_bg2_pin8_34), // output wire [3 : 0] data_to_fabric_bg2_pin8_34.bg2_pin9_35(bg2_pin9_35), // input wire bg2_pin9_35.bg2_pin10_36(bg2_pin10_36), // input wire bg2_pin10_36.data_to_fabric_bg2_pin10_36(data_to_fabric_bg2_pin10_36), // output wire [3 : 0] data_to_fabric_bg2_pin10_36.bg2_pin11_37(bg2_pin11_37), // input wire bg2_pin11_37.bg3_pin0_39(bg3_pin0_39), // input wire bg3_pin0_39.data_to_fabric_bg3_pin0_39(data_to_fabric_bg3_pin0_39), // output wire [3 : 0] data_to_fabric_bg3_pin0_39.bg3_pin1_40(bg3_pin1_40), // input wire bg3_pin1_40.bg3_pin2_41(bg3_pin2_41), // input wire bg3_pin2_41.data_to_fabric_bg3_pin2_41(data_to_fabric_bg3_pin2_41), // output wire [3 : 0] data_to_fabric_bg3_pin2_41.bg3_pin3_42(bg3_pin3_42), // input wire bg3_pin3_42.bg3_pin4_43(bg3_pin4_43), // input wire bg3_pin4_43.data_to_fabric_bg3_pin4_43(data_to_fabric_bg3_pin4_43), // output wire [3 : 0] data_to_fabric_bg3_pin4_43.bg3_pin5_44(bg3_pin5_44), // input wire bg3_pin5_44.bg3_pin6_45(bg3_pin6_45), // input wire bg3_pin6_45.data_to_fabric_bg3_pin6_45(data_to_fabric_bg3_pin6_45), // output wire [3 : 0] data_to_fabric_bg3_pin6_45.bg3_pin7_46(bg3_pin7_46), // input wire bg3_pin7_46.bg3_pin8_47(bg3_pin8_47), // input wire bg3_pin8_47.data_to_fabric_bg3_pin8_47(data_to_fabric_bg3_pin8_47), // output wire [3 : 0] data_to_fabric_bg3_pin8_47.bg3_pin9_48(bg3_pin9_48), // input wire bg3_pin9_48.bg3_pin10_49(bg3_pin10_49), // input wire bg3_pin10_49.data_to_fabric_bg3_pin10_49(data_to_fabric_bg3_pin10_49), // output wire [3 : 0] data_to_fabric_bg3_pin10_49.bg3_pin11_50(bg3_pin11_50) // input wire bg3_pin11_50

);用戶邏輯設計

用戶邏輯分為兩個部分,其一為給發送模塊構造數據包,其二為比對模塊,用于檢測接收到的包是否和發送的包一致。

TX_GEN造包模塊

? ? ? ? 該模塊的作用是,在RX模塊訓練階段,構造值為0x0C的數據,當RX模塊訓練結束后,生成正常遞增或者其他要求的88位數據(22對數據通道,每條通道構造的數據包位寬為4)。

RX_MON比對模塊

? ? ? ? 該模塊的作用是:將收到的22對4位數據重新組合成88位的數據,并通過判斷其是否與發送數據相同,輸出檢測結果。

異常:從底層原理到架構級防御,老司機的實戰經驗)

)

)