借助Verilog,在FPGA中實現了帶編碼器的兩臺電機的電機控制系統的RTL級設計。

介紹

借助硬件描述語言 (HDL) Verilog 和 AMD Vivado 設計套件,在 AMD Spartan-7 FPGA 中實現帶編碼器的兩個電機的控制器系統的 RTL 設計。

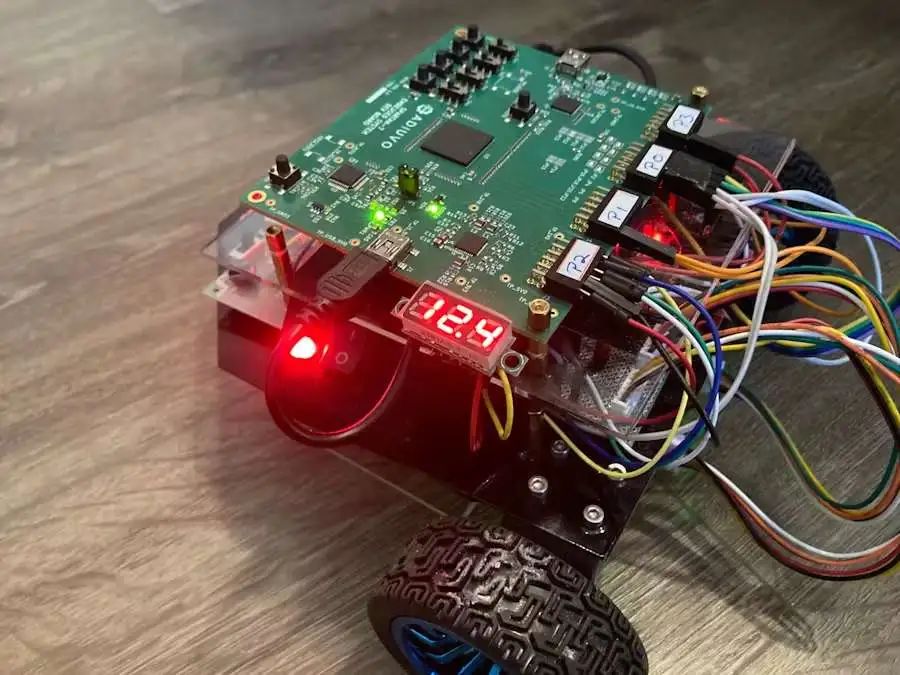

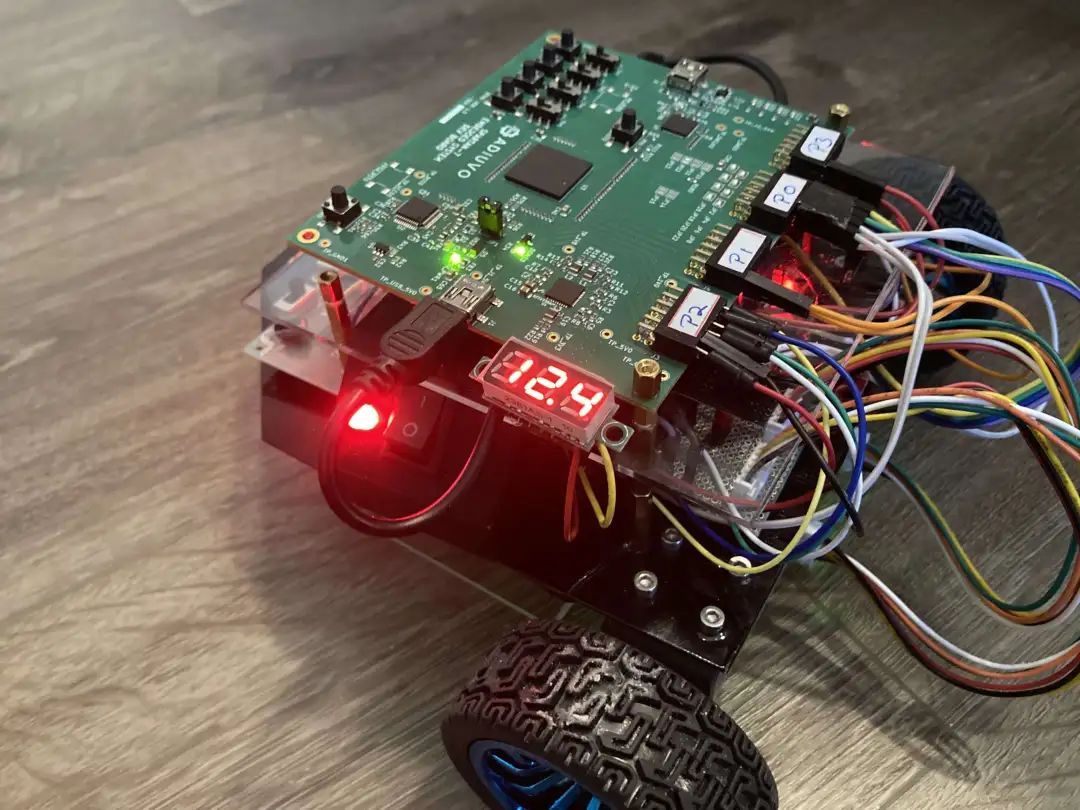

在這個項目中,使用了搭載 Spartan-7 FPGA開發板,將使用它作為電機控制器系統。

在項目開始前,肯定會有人問:“既然用MCU編程要簡單快捷得多,為什么還要用 FPGA 來做這么復雜的工作呢?” 這個問題問得好。所以,我們將簡要探討一下人們選擇 FPGA 的各種原因。

在 FPGA 與MCU的對比競爭之后,將介紹電機驅動器、H 橋、PWM、編碼器、PID 反饋控制系統、編碼和測試、收集日期的分析等多方面的基本概念。然后,將詳細介紹如何構建自己的 FPGAbot。

FPGA 與MCU

為特定產品或可交付系統選擇“最佳”處理技術,在許多方面對其成功至關重要。影響因素包括支持成本、供應鏈、盈利能力、壽命等等。從工程角度來看,決策中最具影響力的典型因素是時間、成本、面積和功耗。

FPGA 優勢

FPGA 以其低延遲、固有的并行處理能力和靈活性而聞名。此外,FPGA還能為許多獨立的計算模塊、外部傳感器和執行器等提供高確定性和精確的定時/延時。因此,會發現 FPGA 被用于許多關鍵任務應用,例如:

1)軍事和航空航天系統

雷達系統 - 例如實時(RT)信號處理和數據采集。 無人駕駛飛行器(UAV)——例如飛行控制、傳感器處理和安全通信。

航空電子設備、衛星、導彈制導系統等

2)工業控制系統(ICS)

對電網、煉油廠等關鍵基礎設施進行實時控制和監控。

工業自動化 - 機器控制,實現故障檢測、冗余和容錯控制。

功能安全——例如汽車和工業控制的容錯系統。

3)醫療器械

診斷成像系統 - 快速準確的數據處理。

病人監護——FPGA 為病人監護設備提供高性能、RT 監護和信號分析。

救生設備...

ETC。

4) 電信等

許多關鍵任務應用程序需要實時處理、確定性行為、低延遲、可編程性、并行處理能力、安全性和功率效率。

MCU優勢

對于成本敏感的產品或普通愛好者來說,MCU 是節省成本和加快系統開發周轉的更好選擇。

微控制器使用標準編程語言進行軟件開發,例如 Python/microPython 和 C/C++。FPGA 設計的學習曲線(架構、硬件描述語言、時序問題等)則要陡峭得多,需要投入大量時間和經驗才能高效完成。

MCU 也更適合外設接口和執行重復性任務。通用架構、串行執行流程以及易于外設集成的特性,使得 MCU 在非關鍵任務系統中更具吸引力。

了解了這些之后,現在讓我們深入了解移動機器人電機控制系統的細節!

高級電機控制器系統設計

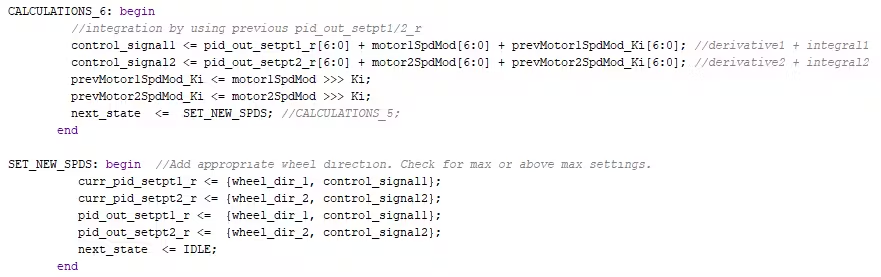

本節介紹了移動機器人電機控制器設計所需的主要外部元件和FPGA功能模塊。此外,還提供了系統的高層原理圖。

電機驅動器

FPGA 需要分別驅動兩個 12V 直流有刷電機。我以前用過 12V 直流電機,發現這個電壓水平能夠滿足我的 DIY 機器人所需的扭矩。我通常會選擇低轉速電機(例如 190 RPM),因為它們比高轉速電機提供更大的扭矩。

L298N H 橋電機驅動器是驅動 12V 電機的絕佳選擇,因為它價格低廉,業余愛好者已經寫了很多關于其使用的文章,并且易于連接。

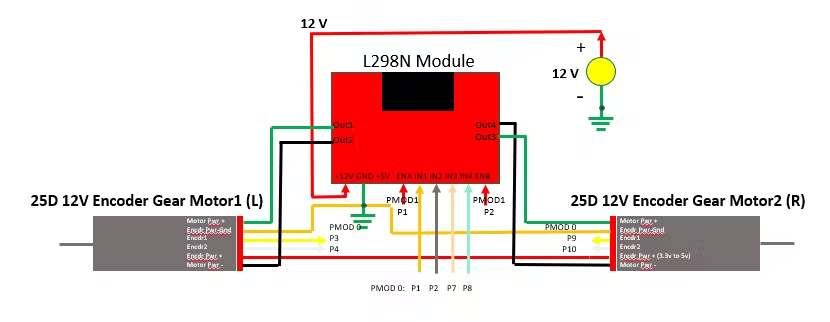

L298N 本質上是一個放大器,其數字接口由較小的輸入控制電壓(例如 3.3V 或 5V)控制,并在較大的直流電壓范圍內產生比例輸出。L298N 模塊可在 5 至 35V 直流電壓 (Vs) 范圍內工作。由于我們使用的是 12V 直流電機,因此源電壓為 12V,如圖 1 所示。

注意:如果要啟用 L298N 板載的 5V 電源調節器,則最大輸入直流電源不應超過 12V。否則,5V 直流調節器會過熱并關閉。

編碼器

我總是購買配備霍爾效應傳感器的直流電機。這些傳感器可以測量每個電機的速度和旋轉方向。在本設計中,編碼器反饋用于PID算法,以保持FPGA機器人直線穩定地移動。里程也可以根據這些信息計算出來。將在后面的技術回顧部分和FPGA電機控制器設計細節部分詳細討論編碼器的工作原理和使用方法。

因此,該系統至少需要以下功能元素:

頂層架構

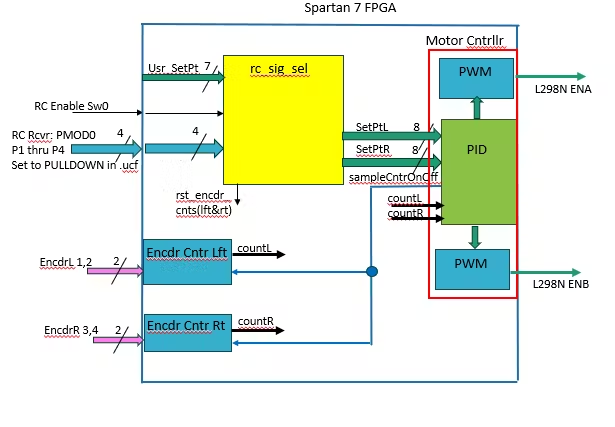

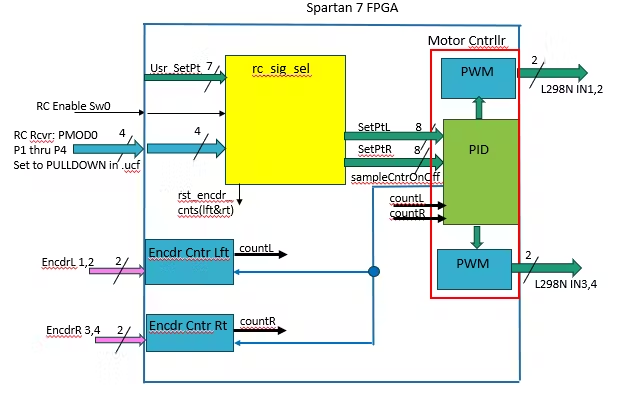

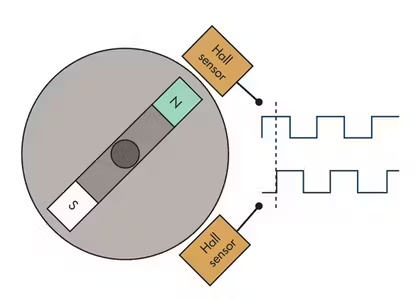

可以選擇 (1) 在使能端使用脈沖寬度調制 (PWM),并通過 IN1、2、3 和 4 上的高低邏輯電平控制方向(圖 2a);或 (2) 在所有四個輸入端口上使用 PWM,并將使能端設置為邏輯高電平(圖 2b)。雖然已經創建了這兩個版本,但在本項目描述中,將選擇選項 (1)(圖 2b)。選擇選項 (1) 的原因將在 L298N 部分解釋。

輸入設定點(PWM 的占空比設置)和旋轉方向源信號選擇器。

編碼器計數器

PID 反饋控制系統/算法將電機速度同步到設定值。

數字控制器,在本例中是 Spartan-7 FPGA。

圖1:L298N和12V編碼器電機原理圖。

圖1:L298N和12V編碼器電機原理圖。  圖 2a:帶有PWM源啟用輸入的FPGA電機控制器框圖。

圖 2a:帶有PWM源啟用輸入的FPGA電機控制器框圖。  圖2b:帶有PWM源INx輸入的FPGA電機控制器框圖。

圖2b:帶有PWM源INx輸入的FPGA電機控制器框圖。 對于上面列出的前兩點,即從設定值生成PWM信號所需的邏輯,了解L298N的工作原理非常有幫助。因此,下一節(可選閱讀)將介紹這部分內容以及其他背景知識。

技術回顧

本節將對組件進行技術回顧,并介紹與這些組件接口所需的數字和模擬概念。本節涵蓋的信息并非執行本項目的必要條件,但有助于理解創建各種模塊和邏輯的原因。

L298N電機驅動器

如圖 3 所示,L298N 可歸類為一種直流放大器,它在其輸入端轉換脈沖寬度調制 (PWM) 信號,在本例中為 0 和 3.3VDC,并將其按比例轉換為穩定的 0V 直流電壓至 Vs,如前所述。

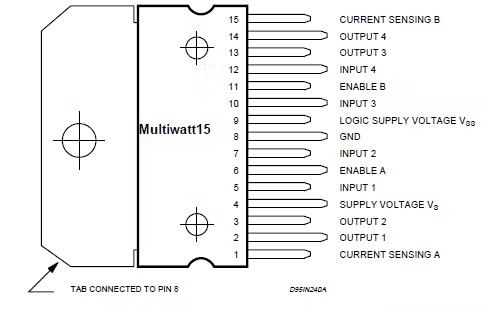

圖3:L298N電機驅動器

圖3:L298N電機驅動器 FPGA 的較低輸出電壓 0 - 3.3V 能夠驅動 TTL 邏輯輸入 (IN1 - IN4) 并使能 A 和 B 的原因在于 [1] 中列出的規格以及圖 4b 所示的規格。其中說明如下:

控制信號輸入電壓范圍:

邏輯低電平:-0.3V≤Vin≤1.5V

邏輯高電平:2.3V ≤ Vin ≤ Vss

其中,Vss 由 L298N 模塊板載的 5V 直流穩壓器供電。由于 FPGA 不會從 L298N 接收數字數據,因此無需邏輯電平轉換器。

L298N 模塊是基于 L298 集成電路 (IC) 構建的。L298 IC 是一款高電壓、高電流雙全橋驅動器。L298 IC 的額定電壓 Vs = 5V 至 46V(圖 2a 和 2b),但 L298N 模塊在 35V 以上的電壓下存在散熱和元件限制。

圖 4a:L298IC-雙全橋驅動器。[1]

圖 4a:L298IC-雙全橋驅動器。[1]  圖 4b:L298部分電氣特性列表[1]。

圖 4b:L298部分電氣特性列表[1]。 L298 雙 H 橋

讓我們快速看一下 H 橋電路。如果還沒有完全理解下面的信息,不用擔心,但為了完整性,我想補充一下。另外,如果愿意,可以跳過本節。

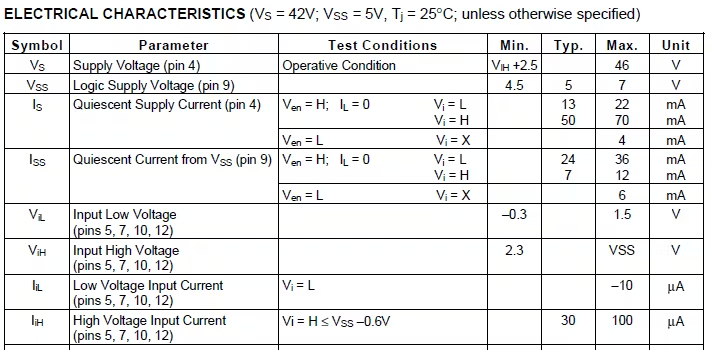

圖 5 是 [1] 中 L298 框圖的復制版。圖中展示了數字電路(與門和非門)和模擬電路(BJT 晶體管和電阻)的混合。邏輯門和 BJT 晶體管構成了電流控制電路。為了更好地理解電流控制電路的整體功能,下面給出了該圖的簡化版本及其說明。

圖5:L298IC框圖[1]

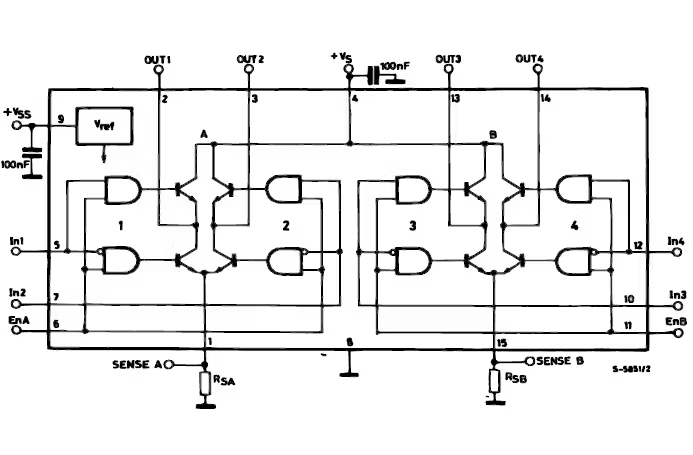

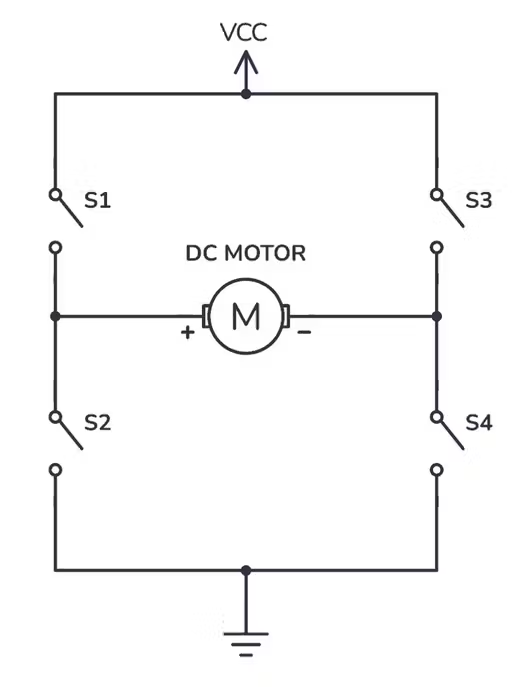

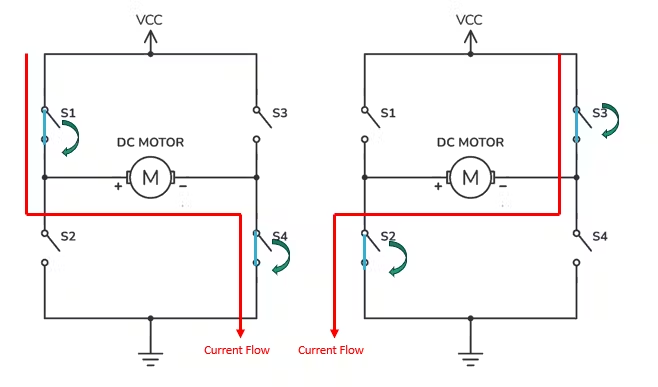

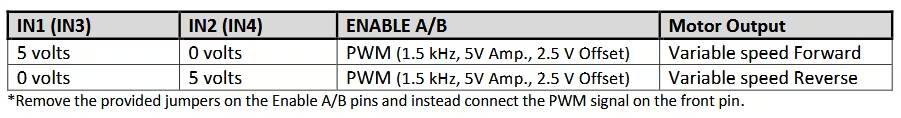

圖5:L298IC框圖[1] 圖 6 用開關概念代替了電流控制電路。這展示了 H 橋電路的工作原理,我們也將用它來解釋在 IN 引腳和 EN 引腳上使用 PWM 的區別。

圖6:簡化的單H橋電路表示

圖6:簡化的單H橋電路表示 要使電機正轉,需要閉合 S1 和 S4,完成從 Vs 經電機到地的電路(即電流路徑)。S3 和 S2 根據需要保持斷開。要使電機反轉,則需要相反的情況,即閉合 S3 和 S2,斷開 S1 和 S4。圖 7a 和 b 說明了這一概念。

圖 7a 和 b:電機正向和反向旋轉。

圖 7a 和 b:電機正向和反向旋轉。 將此電路分析與圖6聯系起來,讓我們看看用與邏輯門和BJT實現的開關。下面的邏輯方程等同于與門的輸出,我們在這里將其標記為_d(代表數字)。

SW1_d = IN1 AND ENA

SW2_d = NOT IN1 AND ENA

SW3_d = IN2 AND ENA

SW4_d = NOT IN2 AND ENA

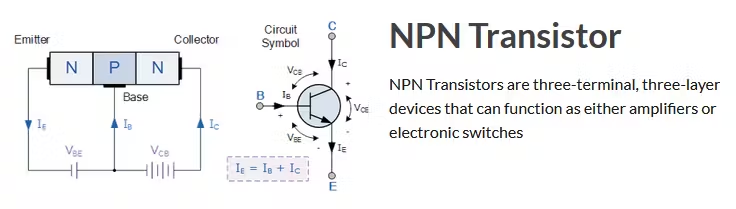

當上述任意 SWx_d 等于邏輯高電平時,相應的 BJT 導通。這是通過基極-發射極正向偏置(Vbe 超過基極輸入和發射極輸出引腳之間 +0.7V 的壓降閾值)來實現的。當集電極電壓分別大于基極和發射極電壓(Vc >> Vb > Ve)時,導通的晶體管就像一個閉合的開關。參見圖 8。

圖8:NPN晶體管[5]。

圖8:NPN晶體管[5]。 希望開關類比能夠簡化數字晶體管的控制邏輯。如果感興趣并且具備相關背景知識,建議找一本好書或參考資料,進一步了解晶體管的工作原理以及不同類型的晶體管。

接下來,如果需要復習一下 PWM,我們來快速回顧一下。如果不需要,可以跳過此部分。

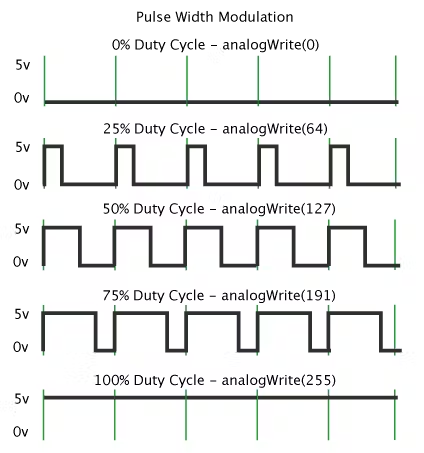

PWM

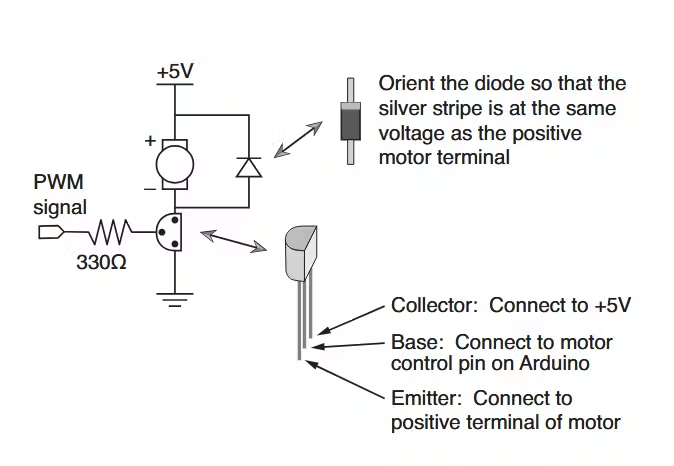

為了使連接到 L298N 電機驅動器的電機實現變速,我們使用了 PWM(脈沖寬度調制)。PWM 是一種獲取可變模擬電壓的數字方法。因此,方波數字信號的占空比(邏輯高電平時間與總脈沖周期的關系)可以通過增加或減少來改變模擬電路中的平均電壓(圖 9)。例如,如果 NPN 晶體管的基極-發射極結在給定的時間內導通時間更長,則電流會更大,從而導致集電極輸出連接和發射極(在本例中為地)之間的電壓降 (Vce) 更大。圖 10 演示了這一概念 [7]。

圖9:各種占空比產生的 PWM[6]。

圖9:各種占空比產生的 PWM[6]。  圖10:使用 PWM 和 NPN BJT 的直流電機電路[6]。

圖10:使用 PWM 和 NPN BJT 的直流電機電路[6]。 L298N PWM輸入響應特性

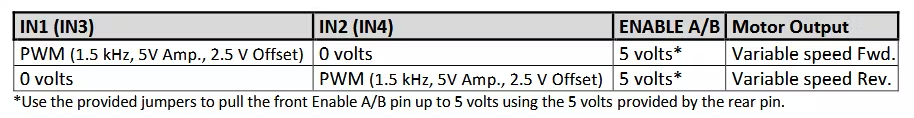

如本文開頭所述,使用 PWM 實現變速有兩種不同的方法。方法 1 是用 PWM 驅動輸入引腳(IN1、2、3 和 4),并將使能引腳設置為高電平,如圖 11a 所示。方法 2 是將輸入引腳對設置為高電平和低電平,以獲得正確的旋轉方向,并用 PWM 驅動使能引腳,以實現變速,如圖 11b 所示。

圖11a:使用PWM控制電機速度的方法1[2]。

圖11a:使用PWM控制電機速度的方法1[2]。  圖 11b:使用 PWM 控制電機速度的方法 2 [2]。

圖 11b:使用 PWM 控制電機速度的方法 2 [2]。 使用方法 1 可獲得如圖 7a 和 7b 所示的電流。唯一的區別在于每個脈沖周期內從 Vs 到 Gnd 的電流流動時間。

使用方法 2 會得到略有不同的響應。如果驅動電機正向旋轉,IN1 上的 PWM 信號將處于活動狀態,而 IN2 上的 PWM 信號將保持在低電平。由于 ENA 已通過跳線設置為邏輯高電平,因此開關切換完全由 IN1 上的有效 PWM 信號控制。將 IN2 和 ENA 都設置為受控的穩定值(0 和 1)后,SW3 始終設置為“關閉”或“打開”,SW4 始終設置為“打開”或“閉合”。但是,用于 SW4(~In1 和 EnA)的非門將在 PWM 占空比的低電平期間打開 SW2。這發生在 SW1 處于“關閉”或“打開”狀態時。因此,電機的正極和負極連接到地。這會導致在 SW2 處于“打開”狀態時釋放反向的感應電動勢 (EMF)。這種配置在較低轉速下有用,但在較高轉速下,由于反向 EMF 電壓的反復損耗,會導致更高的電流消耗。

圖12a和b:左圖,In1+PWM 周期的一部分。右圖,PWM周期的接地狀態。

圖12a和b:左圖,In1+PWM 周期的一部分。右圖,PWM周期的接地狀態。 12V直流編碼器齒輪電機

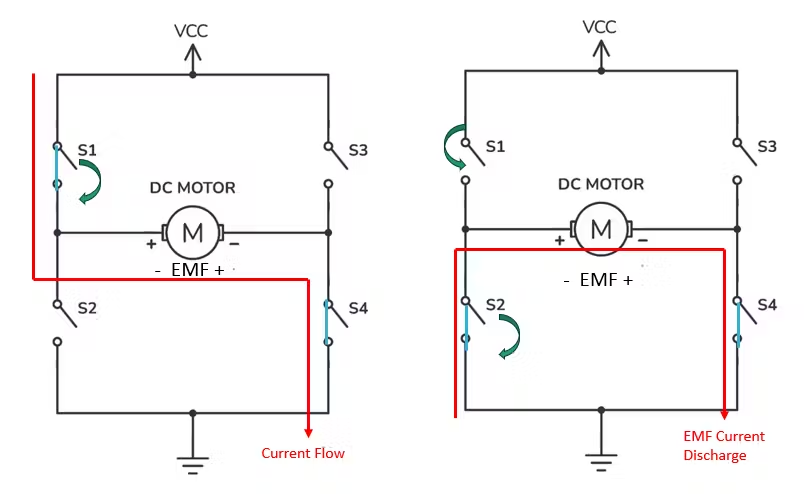

我們為移動機器人選擇的直流電機是專門配備磁編碼器的。這對于此類直流電機來說很常見。對電機控制精度要求更高的直流電機則使用光學編碼器。

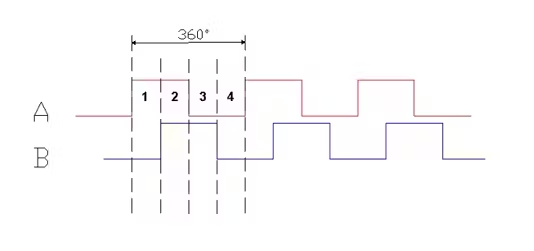

旋轉磁編碼器有兩個霍爾效應傳感器。它們相對于電機軸線呈 90 度角放置。圖 13 展示了這種布置如何產生相位差 90 度的編碼器信號。

圖13:霍爾效應傳感器用于測量轉速和方向[8]。

圖13:霍爾效應傳感器用于測量轉速和方向[8]。 此圖簡化了,因為只使用了兩個磁極。大多數帶有磁編碼器的電機都有數十到數百個這樣的磁極,從而提高了電機旋轉位置的分辨率。此外,有些系統會配備 4 個霍爾傳感器,以進一步提高精度。

上面顯示的霍爾效應傳感器產生的兩個信號被指定為通道 A 和 B。這些通道具有以下特點:

它們的相位差為 90 度(見圖 14)。

如果 A 領先于 B,那么電機就只能朝一個可能的方向轉動。

如果 B 領先于 A,那么電動機的轉動方向與前一個子彈的轉動方向相反。

方波的頻率與齒輪的旋轉速度成正比。

圖14:編碼器通道A和B 波形。

圖14:編碼器通道A和B 波形。 通過計算電機單次旋轉產生的脈沖數,可以推導出由所用物理極數獲得的分辨率。該信息可用于估算機器人的里程,方法是使用累積計數(我喜歡稱之為“tics”)來計數/旋轉,并使用車輪的直徑(或半徑)來計算其周長。

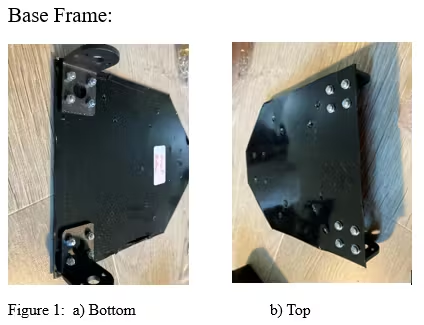

FPGA電機控制器設計細節

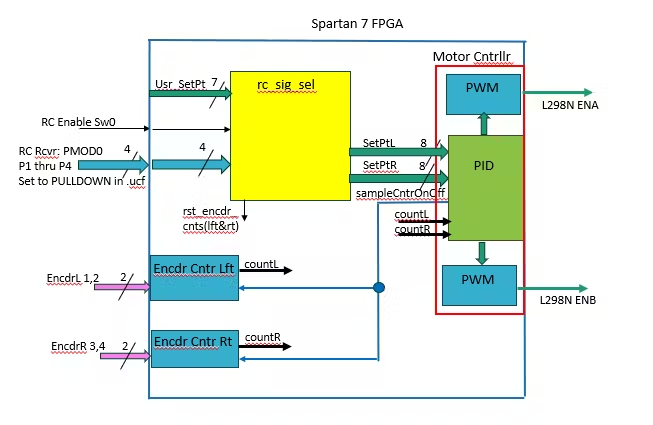

本節將詳細介紹移動機器人電機驅動系統的關鍵 Verilog 代碼。為了方便起見,該代碼將與圖 2a 所示的系統框圖關聯起來,并在下面的圖 15 中復制。此外,我推導的 PID 算法可用作超前-跟隨電機速度比較系統,并將進行詳細解釋。

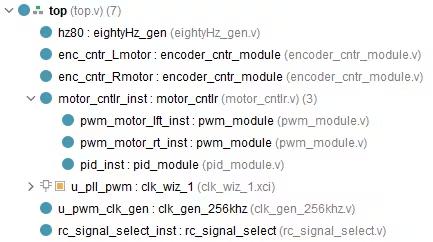

Verilog 源層次結構

從圖 15 所示的初始頂層設計中,派生出 Verilog 模塊層次結構,然后在 AMD Vivado 中創建(圖 16)。

圖15:電機控制系統的初始和最終框圖

圖15:電機控制系統的初始和最終框圖  圖16:AMDVivado中的Verilog模塊層次結構

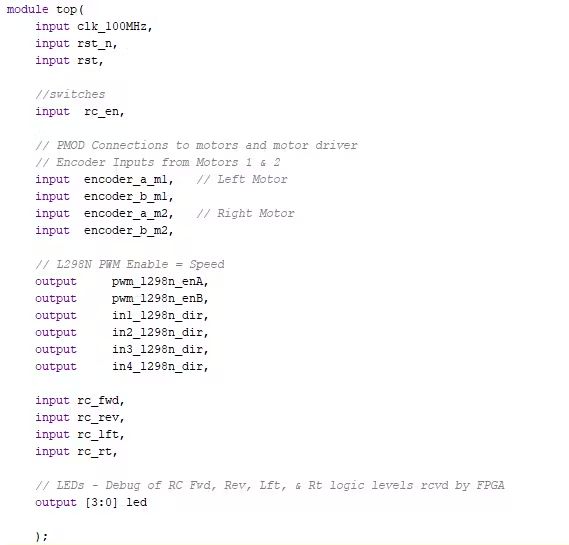

圖16:AMDVivado中的Verilog模塊層次結構 外部引腳聲明

接下來是用于 FPGA 與外部接口的輸入和輸出信號聲明的 Verilog 代碼(圖 17)。在本例中,它用于 L298N、兩個 12V 直流編碼器電機(圖 1)以及 RC 接收器單元(未顯示)。

圖17:Verilog-頂層模塊I/O定義至外部引引腳

圖17:Verilog-頂層模塊I/O定義至外部引引腳 編碼器計數器模塊

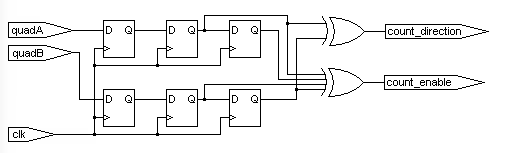

編碼器計數器模塊所用的代碼源自fpga4fun.com [9](http://fpga4fun.com/)。在那里,可以找到詳細的解釋以及描述所用邏輯的波形圖。本質上,只需使用系統時鐘進行過采樣、幾個邏輯門和 D 觸發器(為跨時鐘域添加了幾個額外的觸發器)即可確定自旋的計數和方向。圖 18 展示了代碼的實現。

圖18:編碼器計數器邏輯[9]。

圖18:編碼器計數器邏輯[9]。 我還添加了僅創建正計數的邏輯。這對于我們稍后介紹的PID是必需的。

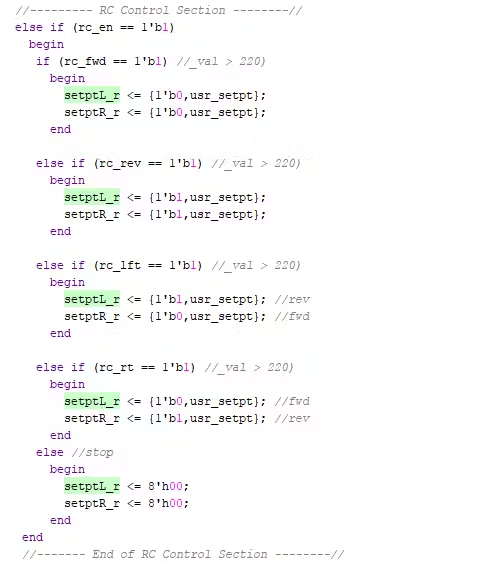

RC信號選擇模塊

此模塊的名稱有點用詞不當。最初,該模塊僅用于接收來自 RC 模塊的方向信號,并將每個信號轉換為兩位值(圖 19)。一位指示左輪應該前進還是后退,另一位指示右輪。每位都位于每個設定值(左輪和右輪)的最高有效位 (MSB)。目前,來自此模塊并進入 PID 模塊的左右電機設定值是相同的值(位 [6:0])。可以在頂部模塊中更改用戶設定值,方法是將 curr_setpt1 和 2 初始化為新值,然后運行 Vivado 進行綜合、實現并生成比特流。此過程最多需要兩分鐘左右。

圖19:rc_signal_selectv 的 RC 啟用代碼部分

圖19:rc_signal_selectv 的 RC 啟用代碼部分  圖 20:添加到rc_signal_select.y的非 RC 模式的附加多路復用邏輯。

圖 20:添加到rc_signal_select.y的非 RC 模式的附加多路復用邏輯。 PWM模塊

如上所述,用戶設定值(頂層名為 curr_setpt1 & 2)存儲在 8 位寄存器的低 7 位中。因此,設定值取值范圍為 0 至 127。該值表示饋入 L298N 的 PWM 的占空比。PWM 如何將設定值轉換為占空比時間寬度?這是通過 PWM 模塊中的 7 位計數器實現的。PWM 的輸出最初為邏輯高電平(計數器 = 0)。當以 256 kHz 時鐘頻率計數的計數器計數到設定值時,PWM 輸出邏輯低電平,直到計數器達到 127。結果是一個 2kHz 方波 PWM,占空比為設定值/127。

使用 Vivado 時鐘向導從 100 MHz 系統時鐘生成了一個 8.192 MHz 時鐘。這樣,256 kHz 模塊中計數器的一位只需要與邏輯“1”進行比較。最終的 PWM 頻率為 2 kHz,接近 1.5 kHz 的示例 [2],并且運行良好。

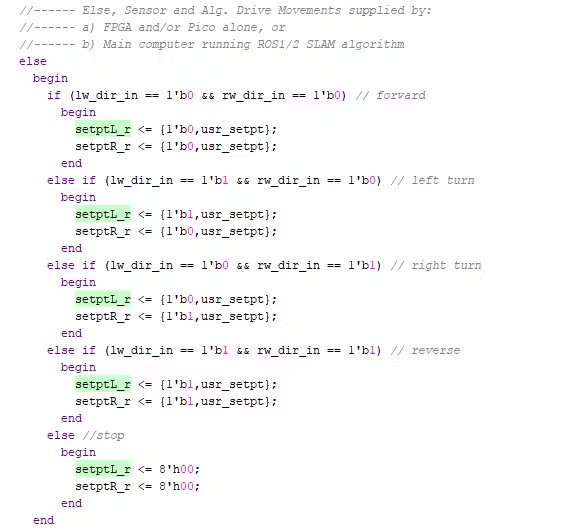

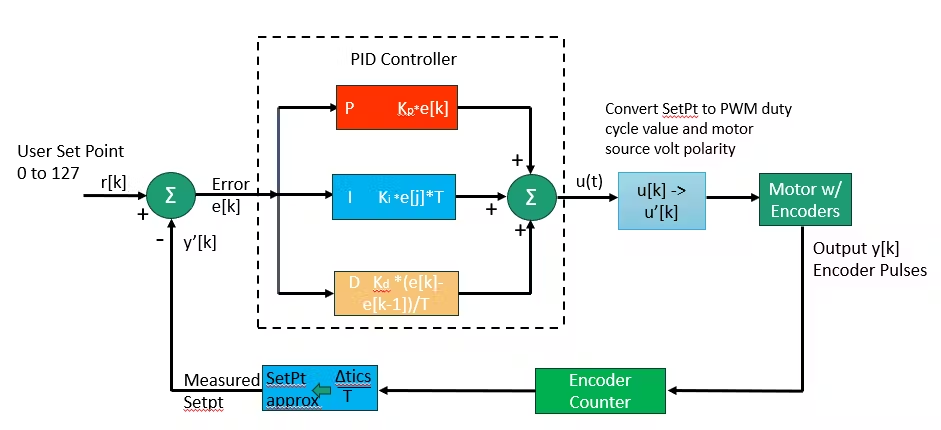

PID

PID 控制器模塊的設計并不像我想象的那么簡單。問題在于設定值(0 - 127)與每設定采樣周期 T(例如 100 毫秒)讀回的增量計數之間的轉換。圖 21 展示了討論中的 PID 反饋回路框圖。

圖 21:時間采樣PID 控制反饋回路

圖 21:時間采樣PID 控制反饋回路 對我來說,這里的問題是我沒有看到(也沒有產生)從 delta tics(計數)/T 回到設定值的低錯誤轉換。

因此,決定使用設定點輸入 r[k] 作為基準值,并添加一個基于兩個電機先前計數和當前計數差異的修改值(誤差值),從而包括每個電機每個周期 T(速度)總計數差異的離散時間分析/比較。

根據使用這些小型直流編碼器電機的經驗,注意到,在相同的PWM占空比設置下,一個電機的扭矩往往大于另一個電機。因此,在PID控制算法中,可以快速確定響應速度更快的電機,并將其用作主電機,以匹配速度和行駛距離。這樣,速度修改只會針對速度較慢的電機的設定值輸入r[k]進行。否則,電機的轉速會非常快地上升。

讓我們看一下所提出的領先-跟隨方程,然后看一下這個離散領先-跟隨電機反饋控制回路的偽代碼。

e[k] = Feedback_1[k] - Feedback_2[k]; (1)

其中,e[k] 是在采樣周期 k 處計算出的誤差,Feedback_n[k] 是在采樣周期 k 處電機 n(即 n = 1 或 2)的編碼器計數器值。

Δx1[k] = Feedback_1[k] - PrevFeedback_1[k-1] (2)

Δx2[k] = Feedback_2[k] - PrevFeedback_2[k-1] (3)

Δx1x2[k] = Δx1[k] - Δx2[k] (4)

其中,PrevFeedback_n[k-1] 是電機 n 的編碼器計數 Feedback[k-1] 在采樣周期 k-1 保存,Δx1x2[k] 是電機 1 和 2 的轉速差。

與圖21所示的PID控制系統一樣,有一些權重值(常數Ki、Ke和Kv)用于將公式(1)和公式(4)相乘,然后再相加。因此,得到的公式如下(圖22所示的部分代碼):

我們將在下面討論局部放電后誤差方程的總體方程為:

u[k] = setpoint[k] + motorNSpdMod (5)

其中,N 再次表示電機數量 1 或 2。

可能注意到,公式 (5) 缺少積分元素。我將解釋如何在 u[k](公式 5)中添加積分,這是平滑 FPGA 代碼部分中誤差振蕩(反復從正到負)的關鍵,但最初并未考慮到這一點。

在 Vivado 中使用 Verilog 編寫設計代碼后,我創建了一個直流編碼器電機的仿真模型,并在測試臺上進行了兩次實例化。該電機模型從被測單元 (UUT) 采樣 PWM 波輸入,并將計算出的轉速轉換為相應頻率的編碼器 A/B 通道波形。編碼器波形通道被輸入到 UUT 中。此外,我添加了一個“阻力”值,使電機的轉速相對于其他電機有所降低。這使得速度較慢的電機的編碼器數量較少,從而與實際電機和系統響應具有一定的相似性。當然,這是一個非常簡單的模型,因為對一個電機增加的阻力是恒定的。如果在電機模型中至少創建一個簡單的物理慣性響應,將會非常有利。該模型還假設移動機器人使用恒定的平坦水平表面。

不幸的是,我看到機器人落地后的響應與仿真結果不同,而我之前預想的沒有物理模型會是這樣的。

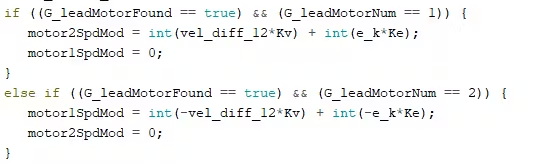

FPGA 中使用的公式經過測試,并根據需要進行了修改(例如,縮短 T 值、調整 Ke 和 Kv 值等),最初使用 Arduino Mega MCU 和 FPGAbot(不含 FPGA)在 C/C++ 中進行了驗證。這縮短了驗證和修改的周期。以下代碼片段來自 Mega 測試(函數 PD_Alg(args)),代表了領先跟隨算法(圖 22)。

圖 22:C/C++代碼中的領先-跟隨PD算法。

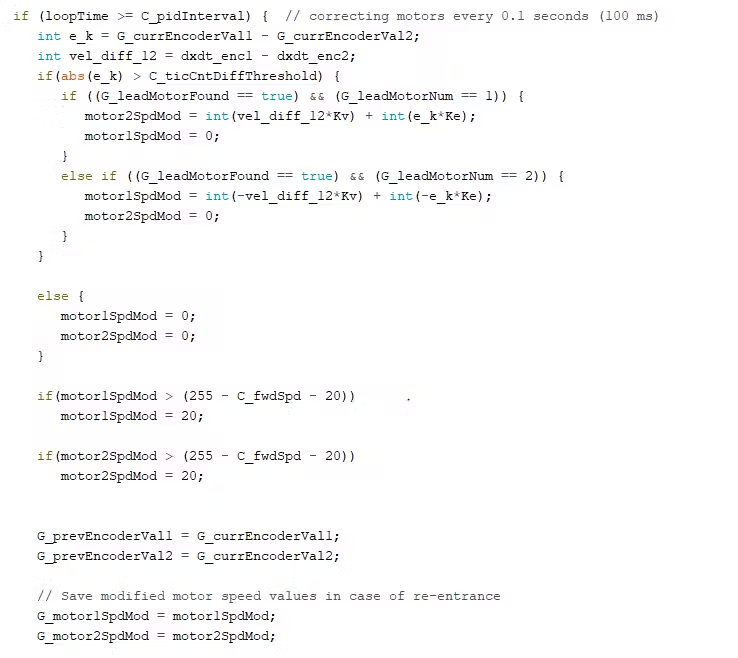

圖 22:C/C++代碼中的領先-跟隨PD算法。 代碼的下半部分,motorNSpdMod 會根據最大設定值 (255 - C_fwdSpd - 20) 進行檢查,以防止值過高。255 是最大占空比值(0 到 255),C_fwdSpd 實際上是兩個電機的設定值(相同值),而 20 只是一個任意值,在 Arduino IDE 控制臺上查看 Serial.print() 滾動顯示的數據時,這個值似乎是合理的,如圖 23 所示。

圖 23:FPGAbot在地毯上運行的Serial.print()調試數據

圖 23:FPGAbot在地毯上運行的Serial.print()調試數據 從打印出來的數據來看,顯然可以通過稍微調整 Ke 和 Kv,甚至在混合中添加一個積分元素來實現更好的響應。

FPGA 變體的領先-跟隨 PID 方程實現

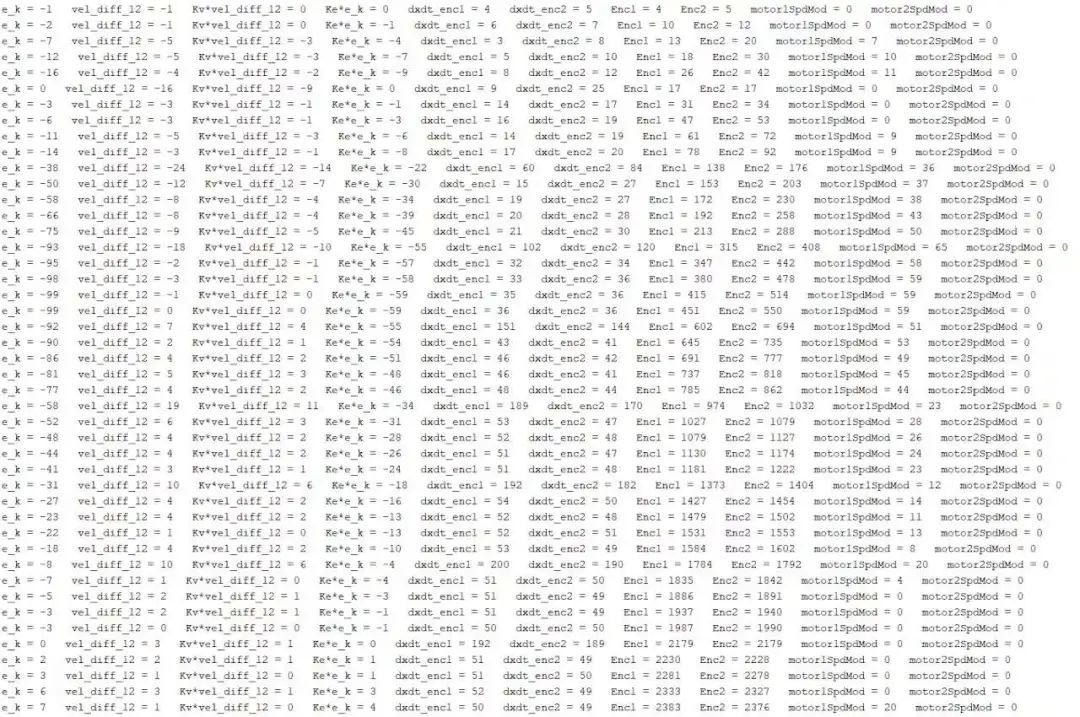

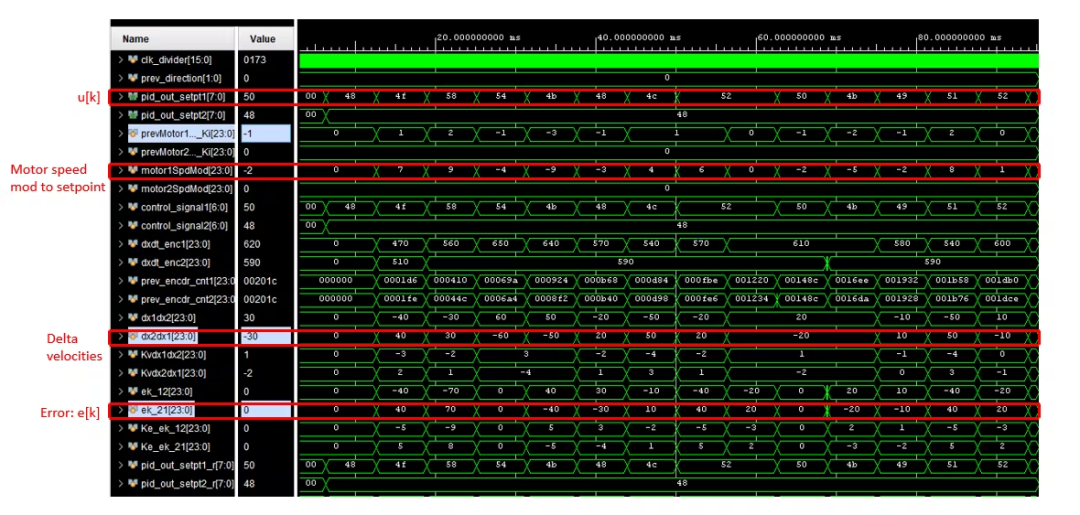

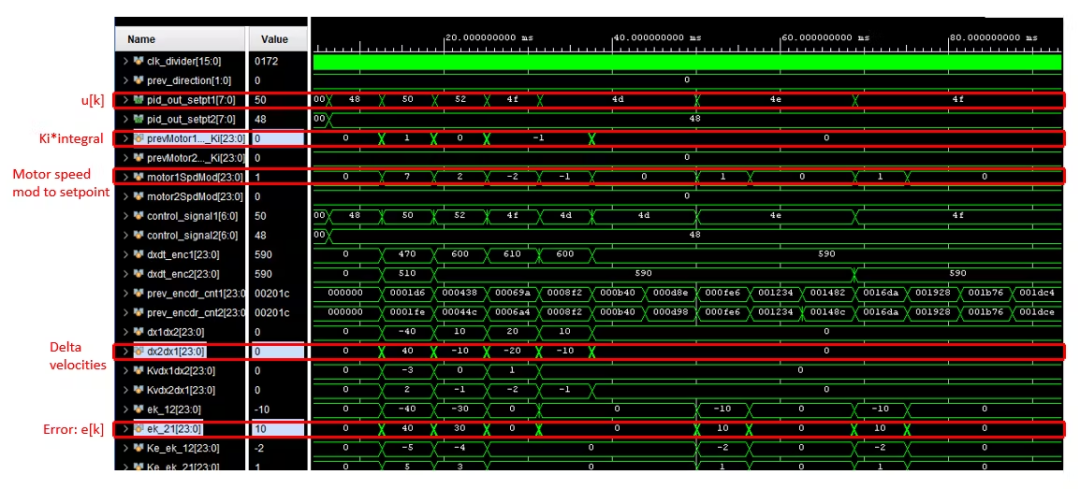

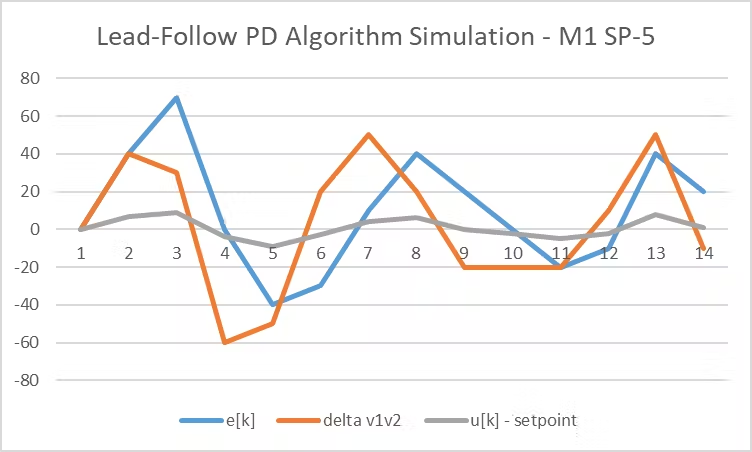

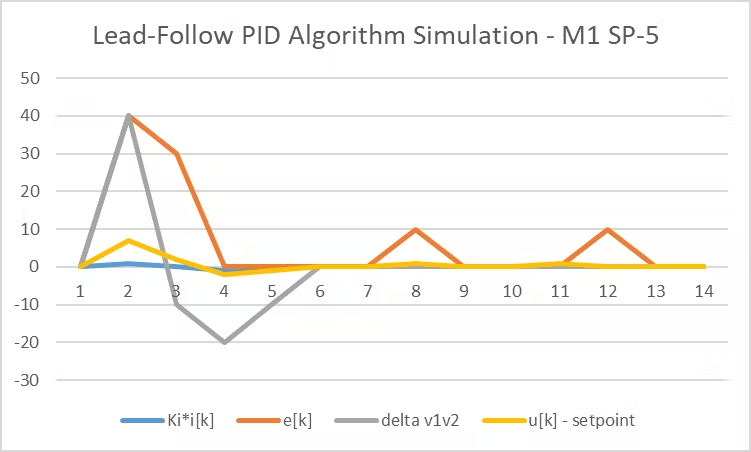

圖 23a 和 b 分別給出了在領先-跟隨方程 (5) 中添加積分之前和之后的仿真結果。

圖 24a:領先-跟隨PID Verilog 實現仿真。

圖 24a:領先-跟隨PID Verilog 實現仿真。  圖 24b:領先-跟隨PID Verilog 實現仿真。

圖 24b:領先-跟隨PID Verilog 實現仿真。 下圖(圖 25a 和 b)分別表示 e[k](誤差)、dx1dx2(電機速度變化量)和 u[k](電機調制值)。圖 25b 還添加了 Ki*integral[k](調制值之和乘以分數)的數據,這些數據列于公式 (6) 中。

u[k] = setpoint[k] + motorNSpdMod + Ki ΣmotorNSpdMod (6)

圖 25a:領先-跟隨控制算法的Verilog 實現中沒有積分部分。

圖 25a:領先-跟隨控制算法的Verilog 實現中沒有積分部分。  圖 25b:添加了積分的領先跟隨控制算法的Verilog實現。

圖 25b:添加了積分的領先跟隨控制算法的Verilog實現。 從這兩幅圖中不難看出,本例中積分非常迅速地抑制了誤差和速度增量的振蕩。這使得 u[k] 的調整非常平緩,與原始設定值吻合。

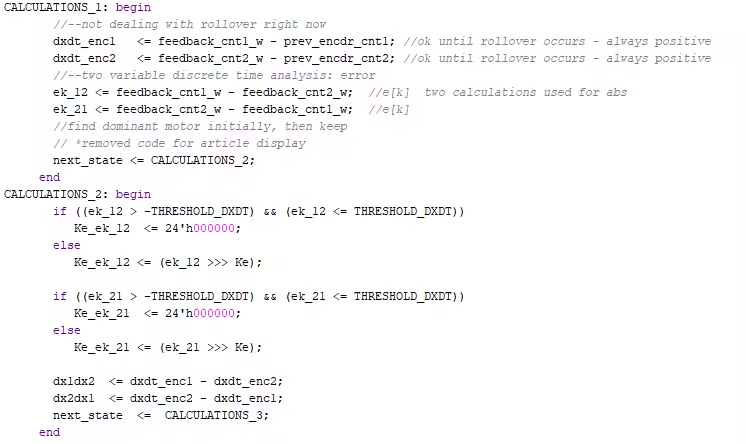

領先-跟隨FB控制算法Verilog代碼

圖 22 所示的 C/C++ 代碼在 MCU 上按順序運行。這就是它們的工作原理。為了在 Verilog 中復制順序計算,使用了一個狀態機,每 10 ns(100 MHz 系統時鐘)從一個計算狀態切換到另一個計算狀態。該算法的計算分布在 7 個狀態中,計算時間為 70 ns。并不擔心將計算時間縮短幾十納秒,并犧牲代碼的可讀性。與采樣周期 T 相比,節省的時間在持續時間上要小三個數量級。為了使其更具可讀性,將計算拆分成多個簡潔的階段會創建數據依賴關系,從而需要額外的時鐘周期。

為了避免使用浮點數表示 Ki、Ke 和 Kv,從而節省大量 FPGA 邏輯資源,通過將誤差、速度增量和積分右移(除以 2^n)來近似這些小數值。然而,在 Verilog 中使用有符號和無符號變量(寄存器)時需要謹慎。我發現,如果使用邏輯移位“>>”,負數右移最終會得到一個很大的正數。為了避免這種情況,需要使用算術右移表示“>>>”。

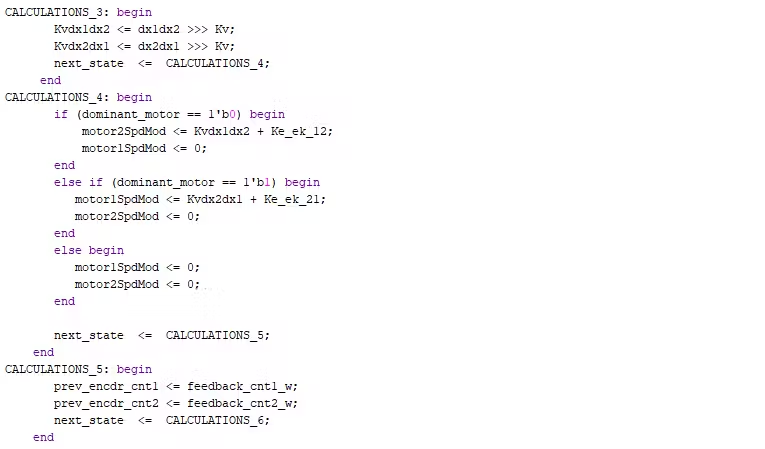

圖 26a、b 和 c 中的代碼演示了目前為止在 Verilog 中實現 PID 領先-跟隨反饋 (FB) 控制算法所涵蓋的概念,并在 Vivado 中進行了仿真(圖 24a 和 b)。

圖 26a:Verilog 領先-跟隨算法 e[k] 和 dx1dx2 計算。

圖 26a:Verilog 領先-跟隨算法 e[k] 和 dx1dx2 計算。  圖 26b:使用ke*e[K] 和Kv*dx1dx2計算motorNSpdMod

圖 26b:使用ke*e[K] 和Kv*dx1dx2計算motorNSpdMod  圖 26c:Verilog 領先-跟隨算法 u[k] 計算

圖 26c:Verilog 領先-跟隨算法 u[k] 計算 其他

一些其他的細節,可以看一組圖片吧~

項目地址

完整的項目可以在Github上找到。

https://github.com/ZenoRobotics/FPGAbot-HacksterIO

參考

[1] 意法半導體 L298 IC 數據表。

https://www.st.com/en/motor-drivers/l298.html

[2] BYU(楊百翰大學)發布的 L298N 電機驅動器及 PWM 詳情 PDF。

https://brightspotcdn.byu.edu/cd/87/bbf866d84c06a0c52fa995396f30/l298n-motor-driver-quick-start-v6.pdf

[3] 意法半導體 L297 步進電機控制器數據表。

https://www.st.com/content/ccc/resource/technical/document/datasheet/f9/35/6e/3f/48/18/48/51/CD00000063.pdf/files/CD00000063.pdf/_jcr_content/translations/en.CD00000063.pdf

[4] “什么是H橋”。

https://www.build-electronic-circuits.com/h-bridge/

[5]“NPN晶體管”。

https ://www.electronics-tutorials.ws/transistor/tran_2.html

[6]“PWM基礎知識”。

https ://docs.arduino.cc/learn/microcontrollers/analog-output/

[7] Rechtenwald,G.“基本直流電機電路”。

https ://cdn.sparkfun.com/assets/resources/4/4/DC_motor_circuits_slides.pdf

[8] “理解光學和磁性編碼器的分辨率”。

https ://www.electronicdesign.com/technologies/components/article/21798142/understanding-resolution-in-optical-and-magnetic-encoders

[9]“FPGA項目:正交解碼器”。

https ://www.fpga4fun.com/QuadratureDecoder.html

)

圖像像素的讀寫操作和算術運算)