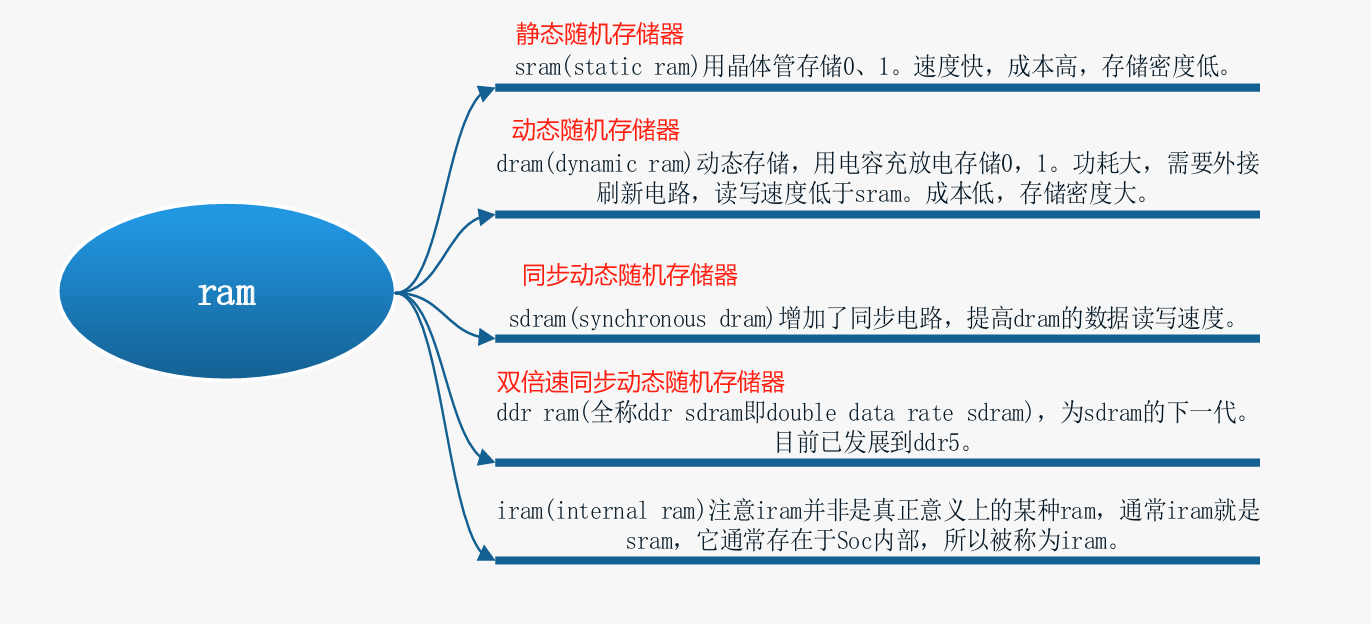

一、RAM 分類

SRAM (Static RAM)

用 觸發器/晶體管 存儲 0/1。

特點:速度快、功耗低(靜態保持),但成本高、容量小。

應用:片上緩存、寄存器文件、單片機內存。

DRAM (Dynamic RAM)

用 電容充放電 存儲 0/1。

特點:存儲密度高、成本低,但需要刷新電路,速度低于 SRAM。

應用:PC 內存、大容量存儲。

SDRAM (Synchronous DRAM)

在 DRAM 上增加時鐘同步,提高讀寫速度。

DDR RAM (Double Data Rate SDRAM)

SDRAM 的升級版,在時鐘上升沿和下降沿均可傳輸數據。

發展分支:DDR → DDR2 → DDR3 → DDR4 → DDR5。

IRAM (Internal RAM)

本質上是 片上 SRAM,直接集成在 SoC 內部,速度快、可直接被內核訪問。

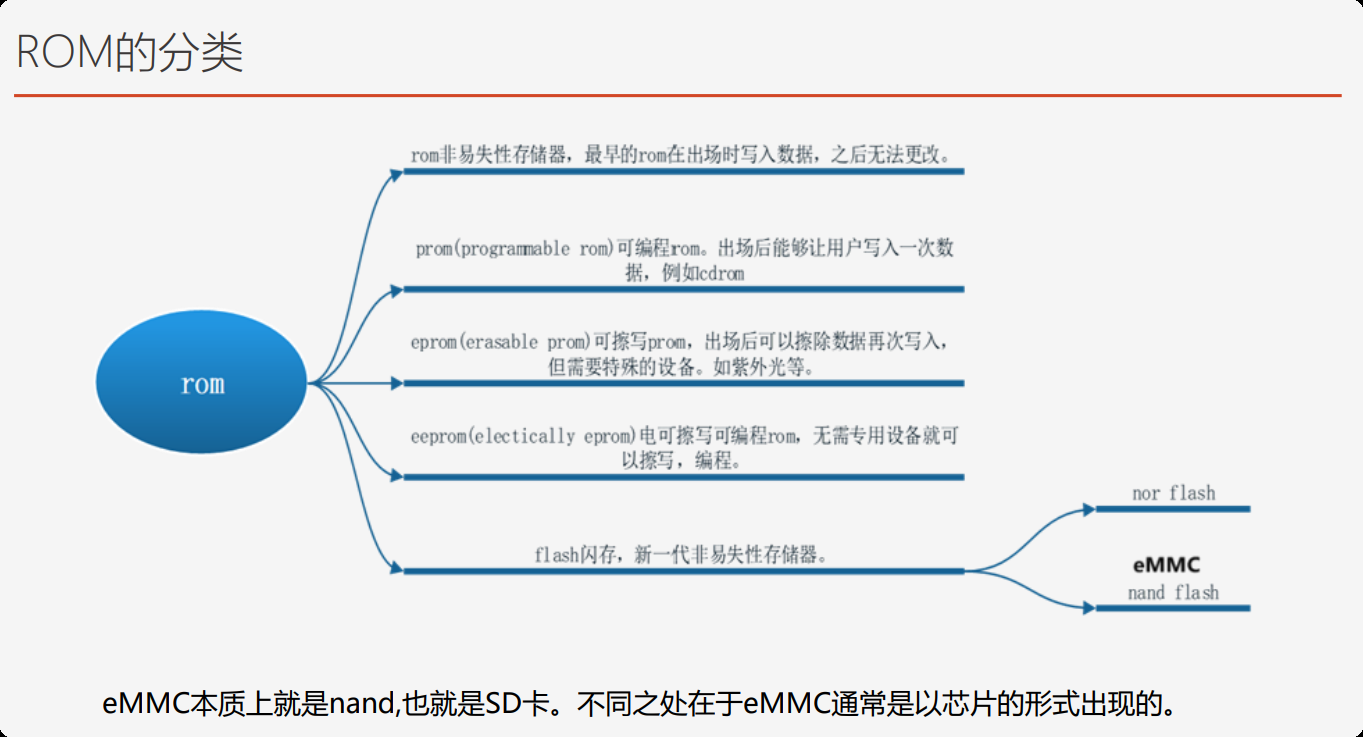

二、ROM 分類

ROM (Read Only Memory)

出廠時數據固定,不可更改。

PROM (Programmable ROM)

用戶可寫入一次數據。

EPROM (Erasable PROM)

可通過紫外線擦除后重新寫入。

EEPROM (Electrically Erasable PROM)

電擦寫方式,速度較慢,但方便修改少量數據(如配置參數)。

Flash 閃存

NOR Flash:字節尋址,可直接執行(XIP, Execute In Place)。

NAND Flash:頁尋址,容量大、壽命長,需控制器管理。

eMMC:嵌入式 NAND,帶控制器,簡化接口。

UFS(Universal Flash Storage):新一代高速存儲接口。

?

三、ARM 內核結構(Cortex-A7 為例)

基本信息

32 位架構,數據寬度 4 字節。

RISC(精簡指令集)設計,流水線執行。

功能單元

ALU:算術邏輯運算。

通用寄存器 R0-R12:主要運算與數據存儲。

專用寄存器:

PC (R15):程序計數器。

LR (R14):連接寄存器,保存返回地址。

SP (R13):棧指針寄存器。

CPSR:當前程序狀態寄存器。

SPSR:保存的 CPSR(用于異常返回)。

存儲與控制

MMU (Memory Management Unit):虛擬地址 → 物理地址映射。

Cache:

I-Cache(指令緩存)

D-Cache(數據緩存)

總線:

AHB:高性能總線(CPU ? 內存)。

APB:外設總線(低速外設)。

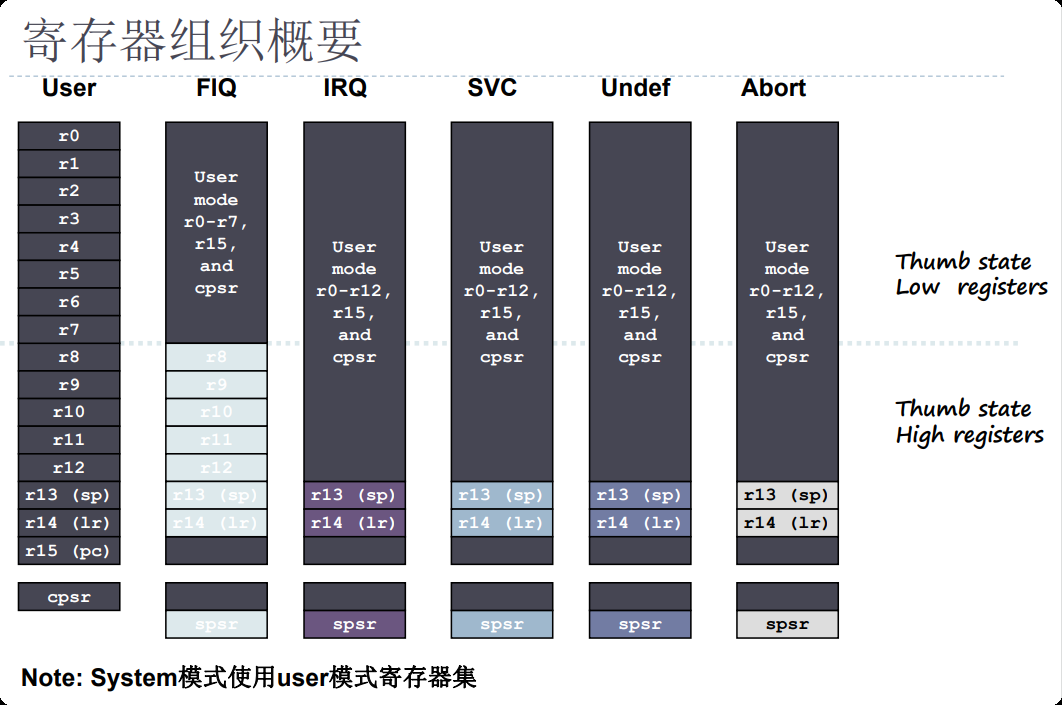

四、ARM 工作模式

Cortex-A7 有 9 種模式:

User:非特權模式,普通應用運行。

FIQ:快速中斷模式,高優先級,專用寄存器多,適合實時處理。

IRQ:普通中斷模式。

Supervisor (SVC):上電復位或軟中斷進入。

上電默認進入 SVC 模式,由啟動代碼切換到 User 模式。

Abort:存取異常模式。

Undef:未定義指令模式。

System:與 User 共用寄存器,但具備特權。

Monitor:安全監控模式(TrustZone)。

Cortex-A 特有模式(部分擴展架構支持)。

說明:

每種模式都有 獨立 SP、LR,保證中斷/異常隔離。

ARM 將 中斷統一視為異常。

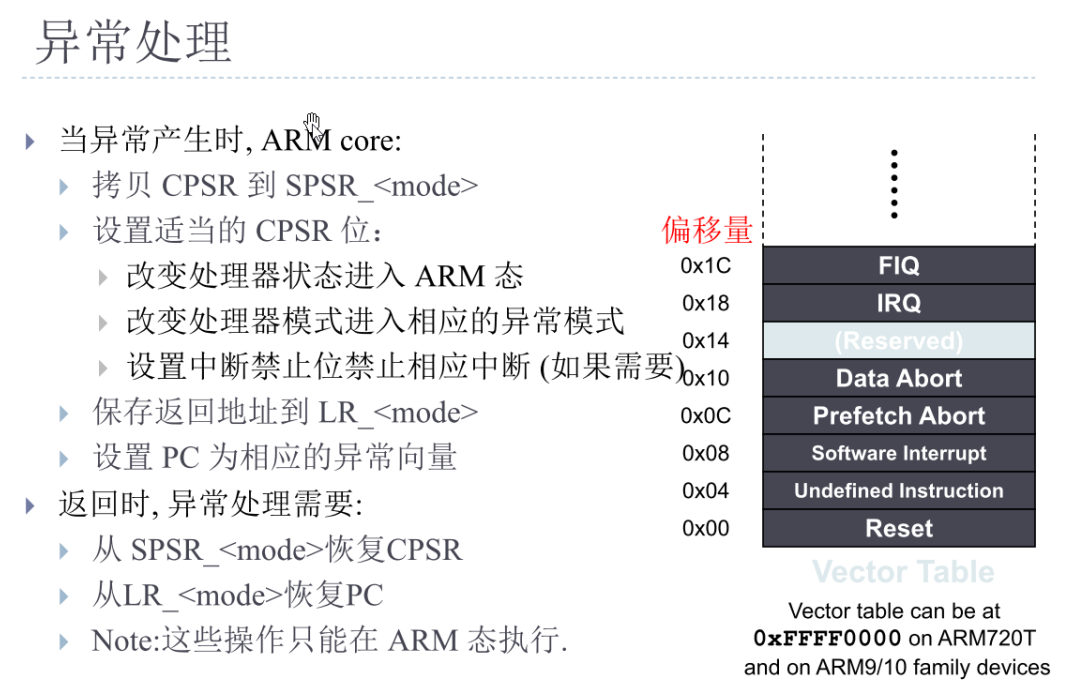

五、異常處理

異常類型

Reset(復位)

Undefined Instruction(未定義指令)

SWI(軟中斷)

Prefetch Abort(指令取指異常)

Data Abort(數據訪問異常)

IRQ(普通中斷)

FIQ(快速中斷)

異常向量表

固定地址存放不同異常入口。

例如:復位向量通常在

0x00000000或0xFFFF0000。

底層流程

保存 CPSR → 切換模式 → 修改 PC → 跳轉異常向量表地址。

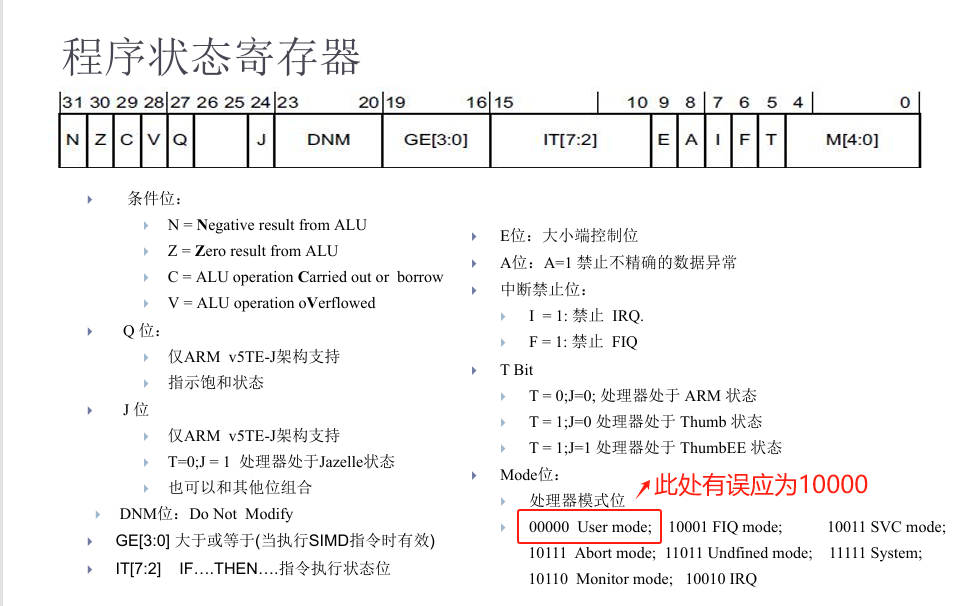

六、CPSR 程序狀態寄存器

Mode 位:工作模式選擇。

條件標志位:

N(Negative):結果為負數 → 1。

Z(Zero):結果為 0 → 1。

C(Carry):無符號運算進位/借位。

V(Overflow):有符號數溢出。

E 位:大小端標志(0 = 小端,1 = 大端)。

IRQ/FIQ 屏蔽位:控制中斷響應。

七、ARM 指令

數據傳送

MOV Rd, #const:立即數賦值。MOV Rd, Rm:寄存器傳值。MVN Rd, #const:立即數取反。

算術運算

ADD Rd, Rn, #constSUB Rd, Rn, #constMUL Rd, Rn, Rm

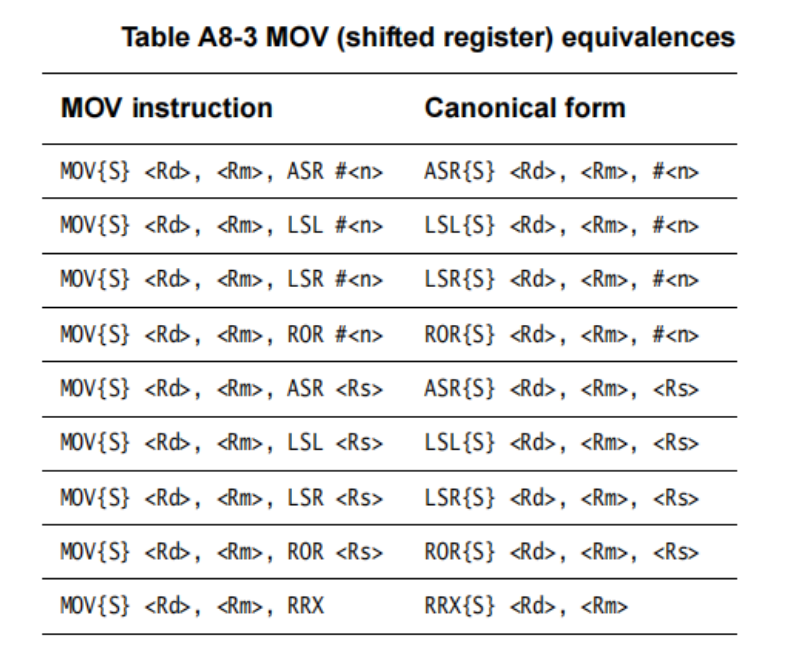

移位操作

LSL:邏輯左移。

LSR:邏輯右移。

ASL:算術左移(等價于 LSL)。

ASR:算術右移(符號位保持)。

ROR:循環右移。

立即數規則

ARM 立即數 = 8-bit 常數 + 4-bit 旋轉。

可通過右旋實現更多常數表示。

)

)

)

)