目錄

1AT89C52原理圖及結構框圖

1.1 原理圖

1.2 AT89C52 結構框圖

1.2.1 8 位 CPU

1.2.2 存儲器

1.2.3 I/O 端口

1.2.4 定時器 / 計數器

1.2.5 串行通信接口?

1.2.6 中斷系統

1.2.7 時鐘與復位

1.2.8 總線結構?

1.2.9 特殊功能寄存器區?

2 AT89C52引腳介紹(PDIP)

3AT89C52使用要點

4AT89C52的存儲結構

4.1程序存儲器(ROM/Flash)——放代碼

4.2數據存儲器(RAM)—— 放變量/堆棧

4.3特殊功能寄存器(SFR)—— 控外設

4.4地址映射總覽

4.5使用小貼士

5定時器 / 計數器

5.1 共性部分

5.2 T0、T1 的 4 種工作模式(M1:M0 決定)

5.3 T2 的專用特性(8052 獨有)

5.4 小結

6 中斷系統

6.1 中斷源一覽

6.2 控制寄存器

6.3 優先級與嵌套規則?

6.4 外部中斷細節

6.5定時器中斷?

6.6串行口中斷

6.7 中斷響應流程(精簡記憶版)?

6.8 使用技巧?

概述:文章摘要:AT89C52是一款基于8051內核的8位單片機,包含8KB Flash程序存儲器、256B RAM、3個定時器/計數器、全雙工串口和8個中斷源。其40引腳PDIP封裝提供32個可編程I/O口,支持多種外設控制。存儲結構分為程序存儲器(8KB片內Flash)、數據存儲器(128B通用RAM+128B SFR)和可擴展64KB片外RAM。定時器/計數器包含T0/T1的4種工作模式和T2的增強功能(捕獲/自動重裝)。中斷系統支持6個中斷向量和2級優先級管理。使用需注意P0口上拉電阻、晶振選型和存儲空間分配等要點。

1AT89C52原理圖及結構框圖

1.1 原理圖

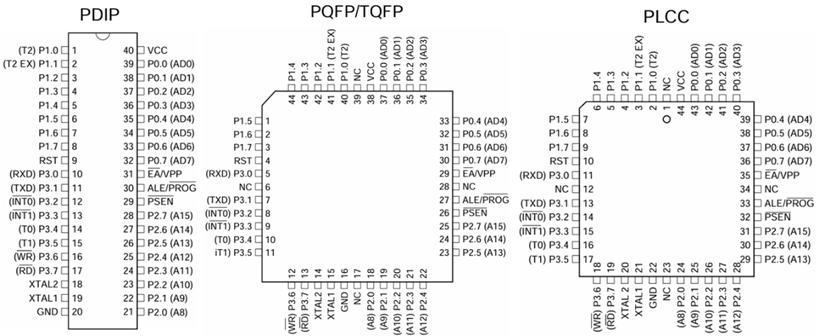

如上圖所示,AT89C52 單片機有 PDIP(雙列直插式封裝)、PQFP/TQFP(塑料四方扁平封裝)和 PLCC(塑料有引線芯片載體封裝)三種封裝形式,以適應不同產品的需求。PDIP 封裝便于手工焊接與調試,適用于實驗開發與小批量生產;PQFP/TQFP 封裝具有引腳間距小、集成度高的特點,適合對體積要求嚴格的產品;PLCC 封裝則在電氣性能與散熱方面表現出色,常用于對性能要求較高的工業級產品。

1.2 AT89C52 結構框圖

1.2.1 8 位 CPU

?? ALU、累加器 A、程序計數器 PC、堆棧指針 SP、指令寄存器 IR 等

1.2.2 存儲器

?? 8 KB Flash ROM(程序存儲器)?

?? 256 B RAM(128 B 通用 + 128 B 可位尋址)

1.2.3 I/O 端口

?? 32 條可編程 I/O 線:P0~P3 四個 8 位端口

1.2.4 定時器 / 計數器

??? 3 個 16 位可編程定時/計數器 T0、T1、T2

1.2.5 串行通信接口?

?? 全雙工 UART(串口)

1.2.6 中斷系統

??? 8 個中斷源、6 個中斷向量、2 級優先級

1.2.7 時鐘與復位

?? 片內振蕩器及時鐘電路(XTAL1、XTAL2)?

?? 上電/手動復位邏輯(RST)

1.2.8 總線結構?

??? 內部 8-bit 數據總線?

?? 16-bit 地址總線(P0、P2 復用)?

?? PSEN、ALE、EA 等控制總線

1.2.9 特殊功能寄存器區?

?? 控制/狀態寄存器:TCON、TMOD、SCON、PCON、IE、IP 等

以上模塊通過內部數據總線和地址總線互連,構成典型的 8051 內核微控制器。

2 AT89C52引腳介紹(PDIP)

AT89C52(40引腳PDIP封裝)各引腳功能一覽表

| 引腳號 | 引腳名 | 功能說明(第一功能 / 第二功能) |

| 1 | P1.0 | 口線 P1.0;T2(定時器 2 外部計數輸入) |

| 2 | P1.1 | 口線 P1.1;T2EX(定時器 2 捕獲/重裝觸發) |

| 3 | P1.2 | 口線 P1.2;普通 I/O |

| 4 | P1.3 | 口線 P1.3;普通 I/O |

| 5 | P1.4 | 口線 P1.4;普通 I/O |

| 6 | P1.5 | 口線 P1.5;普通 I/O |

| 7 | P1.6 | 口線 P1.6;普通 I/O |

| 8 | P1.7 | 口線 P1.7;普通 I/O |

| 9 | RST | 復位輸入;高電平 ≥2 個機器周期復位 MCU |

| 10 | P3.0 | 口線 P3.0;RXD(串口數據輸入) |

| 11 | P3.1 | 口線 P3.1;TXD(串口數據輸出) |

| 12 | P3.2 | 口線 P3.2;/INT0(外部中斷 0) |

| 13 | P3.3 | 口線 P3.3;/INT1(外部中斷 1) |

| 14 | P3.4 | 口線 P3.4;T0(定時器 0 外部計數輸入) |

| 15 | P3.5 | 口線 P3.5;T1(定時器 1 外部計數輸入) |

| 16 | P3.6 | 口線 P3.6;/WR(外部 RAM 寫選通) |

| 17 | P3.7 | 口線 P3.7;/RD(外部 RAM 讀選通) |

| 18 | XTAL2 | 晶振輸出端(接晶振一端或外部時鐘輸入反相端) |

| 19 | XTAL1 | 晶振輸入端(接晶振另一端) |

| 20 | GND | 地 |

| 21 | P2.0 | 口線 P2.0;A8(高 8 位地址總線位 8) |

| 22 | P2.1 | 口線 P2.1;A9 |

| 23 | P2.2 | 口線 P2.2;A10 |

| 24 | P2.3 | 口線 P2.3;A11 |

| 25 | P2.4 | 口線 P2.4;A12 |

| 26 | P2.5 | 口線 P2.5;A13 |

| 27 | P2.6 | 口線 P2.6;A14 |

| 28 | P2.7 | 口線 P2.7;A15 |

| 29 | /PSEN | 程序存儲器讀選通(外部取指時為低電平) |

| 30 | ALE | 地址鎖存允許;平時輸出 fosc/6 脈沖,可關閉 |

| 31 | /EA | 外部訪問使能;低電平時強制訪問外部程序存儲器;高電平時訪問內部 Flash |

| 32 | P0.7 | 口線 P0.7;AD7(地址/數據總線位 7,需外加上拉電阻) |

| 33 | P0.6 | 口線 P0.6;AD6 |

| 34 | P0.5 | 口線 P0.5;AD5 |

| 35 | P0.4 | 口線 P0.4;AD4 |

| 36 | P0.3 | 口線 P0.3;AD3 |

| 37 | P0.2 | 口線 P0.2;AD2 |

| 38 | P0.1 | 口線 P0.1;AD1 |

| 39 | P0.0 | 口線 P0.0;AD0 |

| 40 | VCC | +5 V 電源 |

3AT89C52使用要點

1 P0 口做普通 I/O 時需外加上拉電阻(≈10 kΩ)。

2 ALE、/PSEN、/EA 在僅使用片內 Flash 時可固定接法:

/EA → VCC

ALE、/PSEN 可懸空或保留測試點。

3晶振典型值 11.0592 MHz(便于串口波特率整除),兩引腳加 30 pF 負載電容到地。

4AT89C52的存儲結構

AT89C52的存儲結構=“三大塊 + 可選擴展”

4.1程序存儲器(ROM/Flash)——放代碼

片內:8 KB(= 8×1024 B)閃存,地址 0000h~1FFFh

掉電不丟失,可重復擦寫>1000 次

由 /EA 引腳決定片內/片外取指:?

/EA = 1——>先片內 8 KB,超過 1FFFh 自動跳到片外?

/EA = 0——>強制全部從片外 0000h 開始取指?

片外:最大可擴到 64 KB(0000h~FFFFh)

通過P0(AD0~AD7)+ P2(A8~A15)+ /PSEN 選通并行總線

4.2數據存儲器(RAM)—— 放變量/堆棧

1.片內 RAM 256 B(地址 00h~FFh)

?? ├─ 低 128 B(00h~7Fh)?

?? │?? ├─ 00h~1Fh:4 組工作寄存器 R0~R7(RS0/RS1 選擇)?

?? │?? ├─ 20h~2Fh:位尋址區(16 B×8 bit = 128 可位尋址位)?

?? │?? └─ 30h~7Fh:通用 RAM(函數局部變量、堆棧默認從此開始)?

?? └─ 高 128 B(80h~FFh)?

?????? └─ 特殊功能寄存器區 SFR(與 RAM 統一編址,但用直接尋址訪問)?

????????? 例:P0=80h, SP=81h, DPL=82h, DPH=83h, TCON=88h ……?

2. 片外數據 RAM(可選)?

?? 獨立 64 KB 空間(0000h~FFFFh)?

?? 通過 P0 + P2 + /RD、/WR 選通,與程序空間并行但物理隔離?

?? C 語言用關鍵字 `xdata` 訪問:`unsigned char xdata buf[512];`

4.3特殊功能寄存器(SFR)—— 控外設

占用了片內 RAM 高 128 B 的地址 80h~FFh;常用的有?

端口:P0~P3?

定時器:TMOD, TCON, TL0/TH0, TL1/TH1, T2CON, RCAP2L/H?

串口:SCON, SBUF, PCON?

中斷:IE, IP?

統:SP, DPL, DPH, AUXR, WDTRST ……

4.4地址映射總覽

| 存儲區域 | 地址范圍 | 說明 |

| 片內 Flash ROM | 0000h~1FFFh | 8 KB 程序代碼(默認) |

| 片外 Flash/EPROM | 2000h~FFFFh | 可選擴展,最多 56 KB |

| 片內 RAM | 00h~7Fh | 128 B 通用/位/寄存器區 |

| SFR | 80h~FFh | 128 B 特殊寄存器 |

| 片外 XRAM | 0000h~FFFFh | 可選擴展,最大 64 KB |

4.5使用小貼士

1. 片內 8 KB Flash 足夠中小項目,無需外擴程序存儲器;?

?? 若 /EA = 1,代碼超過 8 KB 會自動到片外,無需手動切換。?

2. 堆棧默認在片內 RAM 07Fh 向上增長;如用片外 XRAM,需手動改 SP。?

3. 無內部 EEPROM;如需掉電數據保存,外掛 24C02 等 I2C EEPROM 最方便。

5定時器 / 計數器

AT89C52內部共有3個16位可編程定時/計數器:T0、T1 和 T2。它們都以“計數源→16 位加法計數器→溢出標志→中斷/硬件事件”這一基本鏈路工作,但在計數源選擇、工作模式、重裝方式及附加功能上各有差異。下面按“共性-差異”方式概述其工作原理。

5.1 共性部分

1. 核心:16 位 THn+TLn 加法計數器(n = 0,1,2)。?

2. 計數源:?

?? 內部 fOSC/12(定時方式,C/T=0)?

?? 外部 Tn 引腳負跳變(計數方式,C/T=1)?

3. 溢出:FFFFH→0000H 時置位 TFx 標志,可請求中斷。?

4. 啟停:由 TRn 位(TCON 或 T2CON 中)控制。?

5. 讀寫:通過專用寄存器 THn/TLn 訪問,均為 8 位,需分兩次完成。

5.2 T0、T1 的 4 種工作模式(M1:M0 決定)

00? 模式0:13 位(THn 高 8 位 + TLn 低 5 位),已淘汰。?

01? 模式1:16 位,一次計數,溢出后需軟件重裝初值。?

10? 模式2:8 位自動重裝,TLn 計數,THn 存重裝值。?

11? 模式3:T0 分裂為兩個 8 位定時器,T1 停止計數(僅作波特率發生器)。?

5.3 T2 的專用特性(8052 獨有)

1. 計數器:TH2+TL2 仍為 16 位。?

2. 捕獲/自動重裝:?

?? 由 T2CON 中 CP/RL2 位決定。?

CP/RL2=1:捕獲方式。當 T2EX(P1.1)出現負跳變時,把當前 TH2/TL2 鎖存到 RCAP2H/RCAP2L,并置 EXF2 標志。?

CP/RL2=0:自動重裝方式。溢出時將 RCAP2H/RCAP2L 預存值裝入 TH2/TL2,并置 TF2。

3. 計數源擴展:除 fOSC/12、T2(P1.0) 外,還可選“向下計數”模式(由 DCEN 位允許),實現可逆計數。?

4. 時鐘輸出:置 T2OE=1 時,T2 引腳可輸出 fOSC/24/(65536-初值) 的方波。?

5. 中斷:TF2(溢出)和 EXF2(捕獲/外部重載)共用中斷向量 5。?

5.4 小結

T0、T1:經典 8051 定時器,模式簡單,常用來產生延時、波特率或外部事件計數。?

T2:8052 增強定時器,帶捕獲/自動重裝、可選向下計數、時鐘輸出,適合更復雜的定時需求(如脈沖寬度測量、可編程時鐘產生)。

6 中斷系統

AT89C52的中斷系統=“6 組固定中斷向量 + 1 組共用中斷向量 + 2 級優先級管理”

6.1 中斷源一覽

| 編號 | 向量地址 | 標志位 | 源/功能 | 觸發方式 |

| 0 | 0003H | IE0 | 外部中斷 0 (INT0) | 低電平 / 下降沿 |

| 1 | 000BH | TF0 | 定時器 0 溢出 | 內部計數溢出 |

| 2 | 0013H | IE1 | 外部中斷 1 (INT1) | 低電平 / 下降沿 |

| 3 | 001BH | TF1 | 定時器 1 溢出 | 內部計數溢出 |

| 4 | 0023H | RI/TI | 串行口 (UART) | 收完/發完 1 字節 |

| 5 | 002BH | TF2+EXF2 | 定時器 2 | 溢出或捕獲/重載 |

共 8 個“物理”中斷源,但向量只有 6 個(T2 兩個標志共用 002BH)。

6.2 控制寄存器

1. IE(A8H)——總中斷允許?

?? EA? ES? ET2? ES? ET1? EX1? ET0? EX0?

?? 1 = 允許;0 = 屏蔽?

2. IP(B8H)——優先級(1 = 高優先級,0 = 低優先級)?

?? —?? —?? PT2? PS? PT1? PX1? PT0? PX0?

?? 8052 新增 PT2,其余位含義同 8051。?

3. T2CON(C8H)——T2 專用?

?? TF2、EXF2 由軟件清 0。?

6.3 優先級與嵌套規則?

兩級:高優先級可打斷低優先級,同級不嵌套。?

同優先級內部再按自然序號 0→5 排隊。?

6.4 外部中斷細節

IT0/IT1(TCON.0/TCON.2)?

0 = 低電平觸發(需手動撤除低電平才能再次觸發)?

1 = 下降沿觸發(自動鎖存,脈沖寬度 ≥ 1 機器周期即可)?

6.5定時器中斷?

TF0/TF1 在計數器溢出時置 1,CPU 響應后硬件自動清 0。?

TF2/EXF2 共用向量,中斷服務程序需判斷是溢出還是捕獲/重載,再分別清 0。

6.6串行口中斷

RI 和 TI 共用向量,進入服務程序后先讀 SCON 判定是“接收完”還是“發送完”,再清相應標志。

6.7 中斷響應流程(精簡記憶版)?

1. 標志置位 → 2. 總中斷 EA=1 且對應位允許 → 3. 優先級仲裁 → 4. 完成當前指令 → 5. 自動把 PC 壓棧 → 6. 裝入向量地址 → 7. 執行 ISR → 8. RETI 返回。

6.8 使用技巧?

下降沿觸發外部中斷時,ITn=1 可避免“電平保持”誤觸發。?

高優先級 ISR 里可再被更高優先級打斷,但同級或低優先級不能打斷。?

T2 的 TF2/EXF2 必須軟件清 0,否則會不停地進入中斷。

腳本 匯總(二))

)