Q1:直播課經常講到一致性,這個一致性的話一般是指place,CTS和PT的derating time,uncertainty和transition嗎,我大概知道innovus的uncertainty設置要比PT里面高一點,但具體設計時這幾部分的大小應該是一個什么樣的關系或者需要大多少,這個有沒有一些經驗值?

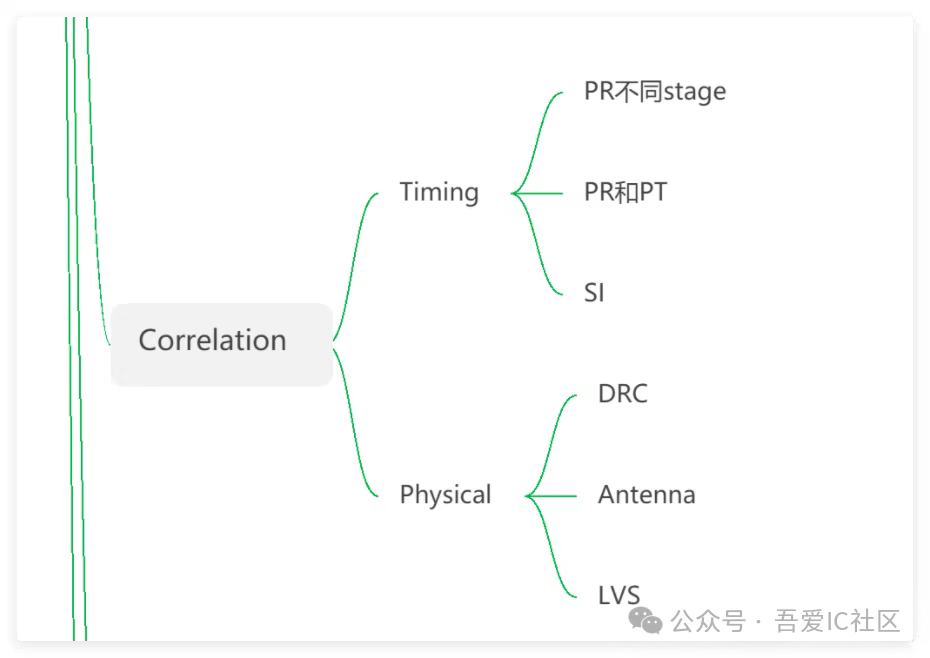

我們一般講的Correlation有Timing Correlation和Physical Correlation。

下面這張圖是我之前分享的一個后端實現全流程思維導圖,其中就把correlation按照Timing和Physical兩個大方向進行劃分(添加微信ic-backend2018免費領取這份思維導圖)。

數字IC后端實現之Setup Violation修復案例(Data&Clock Tree ECO修復手段)

Timing Correlation又分PR實現不同階段之間的時序一致性。

比如Placement做完setup wns是-0.1ns,長clock tree優化時序后setup wns是-0.25ns,這種就是典型的兩個階段之間的timing不一致!

那為何要追求一致性呢?因為長clock tree后的timing比較差,而這個情況在placement階段工具壓根沒看到,那自然就不會做優化,即placement優化不到位。

我們最理解的結果是placement做完,CTS做完clock tree后timing情況就應根據接近于placement后的結果。

這兩個步驟的差別是placement階段clock還是ideal的(時鐘從root到sink的時間為0),而CTS做完各個sink的到達時間是不一致的,所以它們差一個clock skew!

手把手教你如何分析debug Clock Skew高達上ns的案例

那我們是否可以在placement階段提前把后續CTS階段的clock skew考慮進來呢?答案是可以的。

我們在placement階段可以設置一個更大點的clock uncertainty。

這個也就是咱們經常看到的placement clock uncertainty = Clock Jitter +預估clock skew +Timing Margin。

我們應該盡量讓工具在placement階段就把標準單元擺放到最佳的位置上,并把時序一步優化到位。后續其他階段僅僅是針對實際clock skew和實際走線帶來的一些時序變化進行的時序優化。這個優化過程可以比較輕松實現。

這樣實現出來的結果我們可以把PR每個階段的density控制在一個數量級!

PR是基于邏輯連接的物理實現的過程,它里面用的delay計算engine和RC抽取engine肯定和Starrc,PT是不一樣的。所以PR和PT之間的一致性也是我們需要關注的。

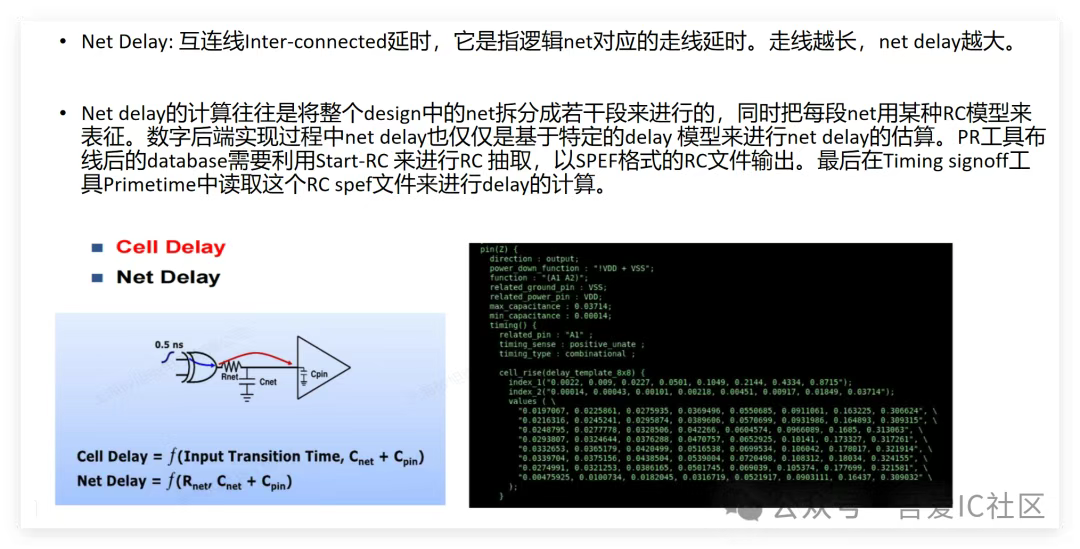

而我們知道delay就分兩種,分別是cell delay和net delay。

所以這兩個階段的timing一致性可以在PR階段通過以下幾個方法來調整(PT中對應值是不能改的)。

1)調整clock uncertainty

2)調整考慮OCV設置的set_timing_derate值

3)調整RC Scale Factor系數

而physical一致性主要指兩邊的routing drc結果是否比較接近。

IC后端項目案例 | Innovus DRC Violation分析及Floorplan合理性分析

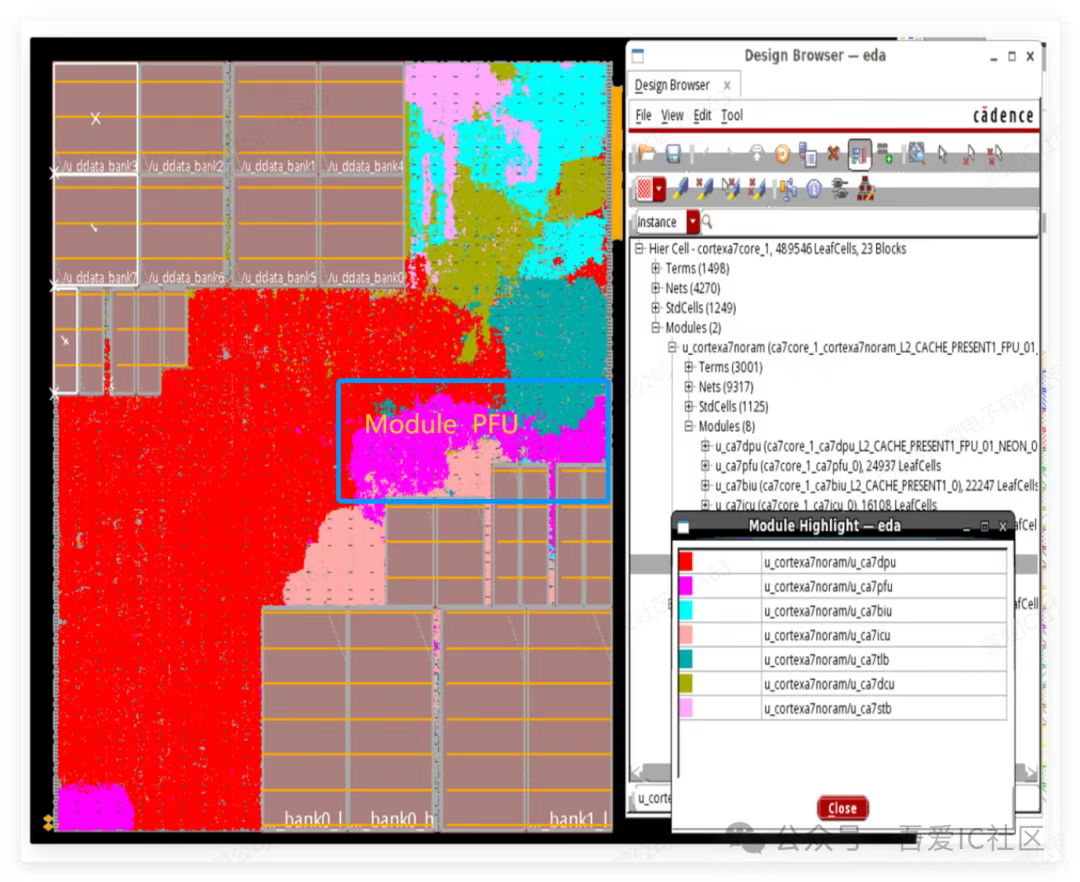

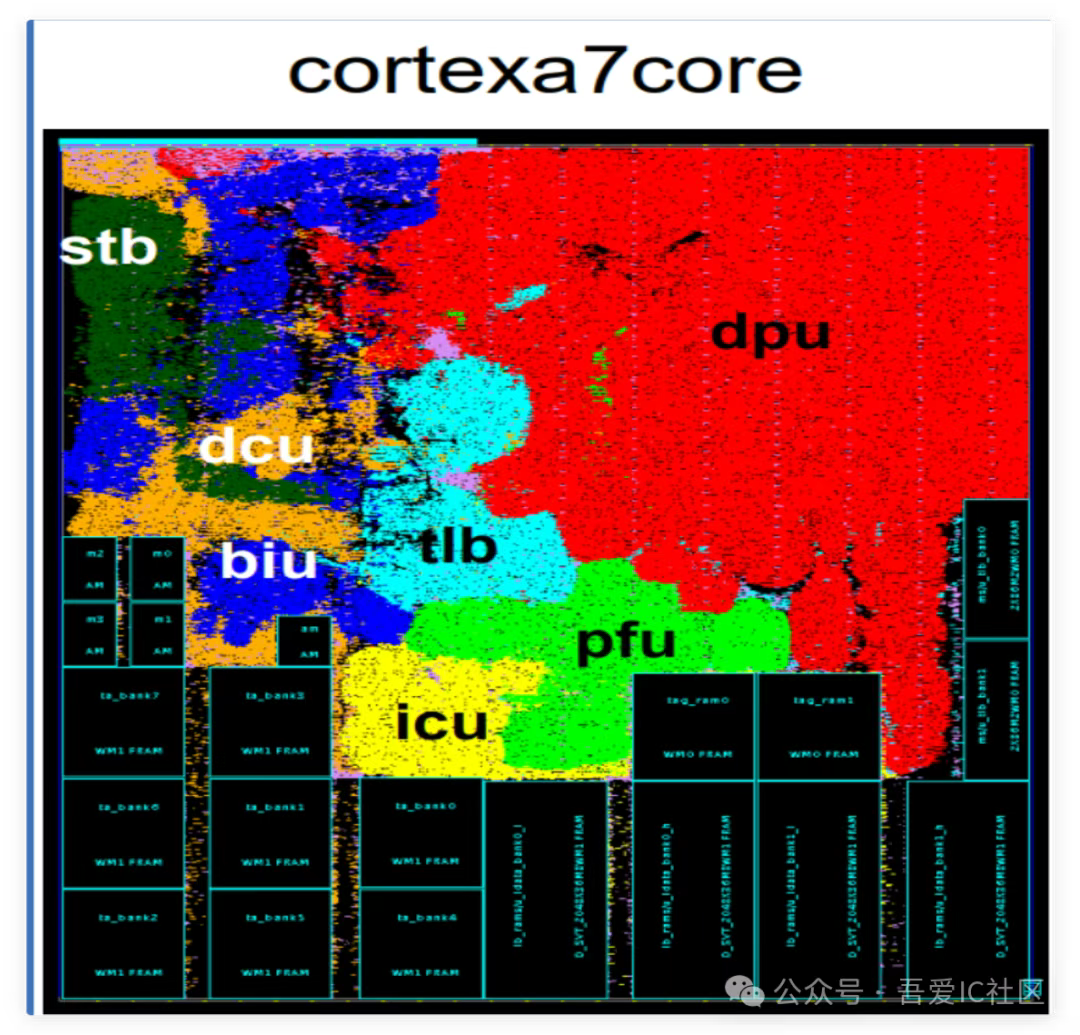

Q2: Place階段有時候出現critical path不在dpu里面需要設置region,想請問這個region是針對什么設置的,我不知道里面應該放什么。因為我想直接在place階段就設置好region,如果這樣可以的話在core的不同部位這個region里面應該擺什么?比如說給一個dpu設一個region它應該放在core的哪一個部位?

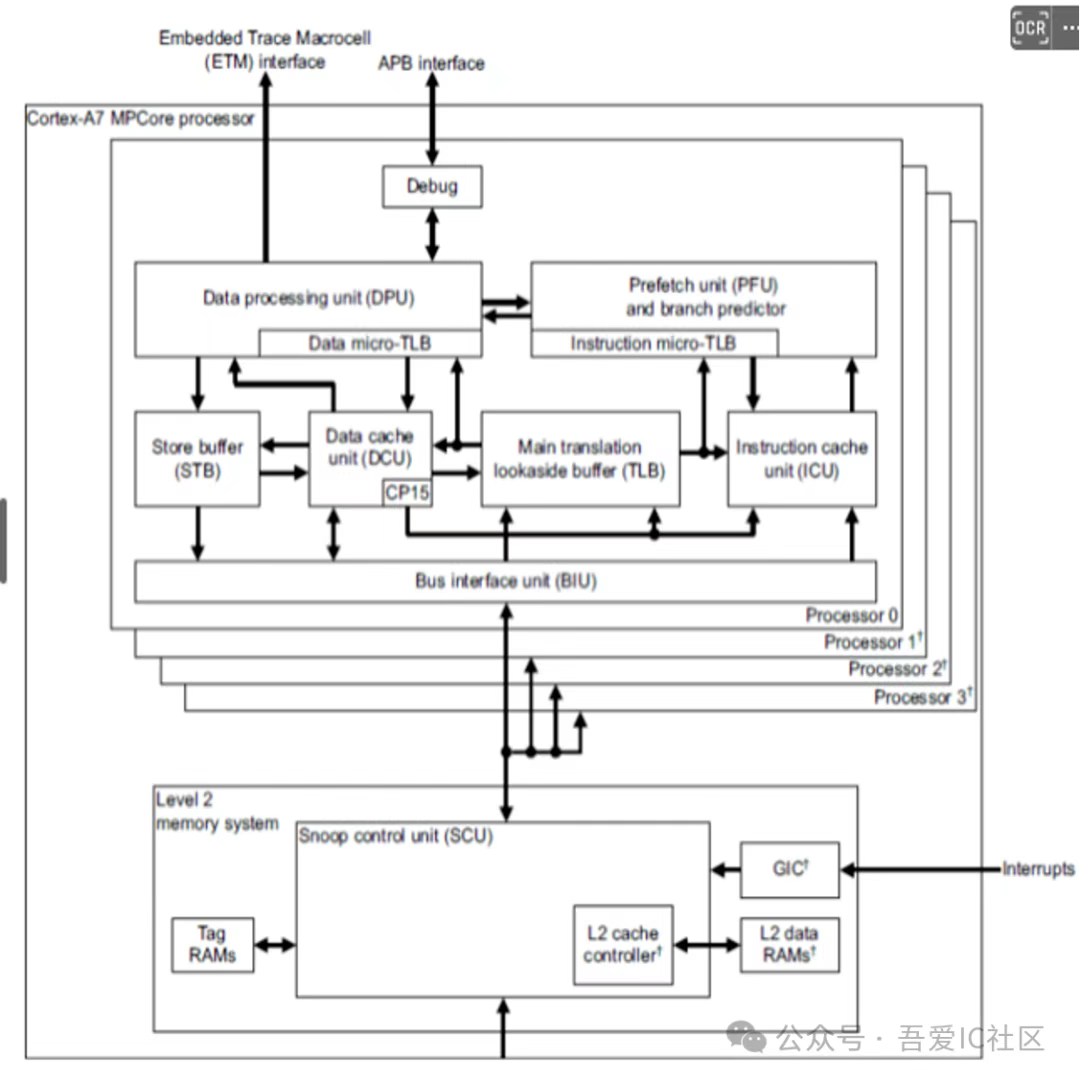

Region一般是針對某個module來設置的。以咱們T28 a7core直播課講的這個案例為例,u_ca7pfu這個module工具自動擺放后被拆成兩部分。這時候我們可以把這個module做成一個region,規劃在中間那個位置。 DPU模塊一般是位于遠離io port那個對角位置,靠近DDATA SRAM。

添加region的的腳本命令如下所示。

set cells [dbGet top.insts.name u_cortexa7noram/u_ca7pfu* -p]

set cells_name [dbGet $cells.name]

createInstGroup PFU

addInstToInstGroup PFU $cells_name

createRegion PFU {300 300 500 600}

我們還可以根據設計的data flow和官方推薦的module分布來精細化規劃每個module的擺放位置。

數字IC設計實現之分段長clock tree典型案例(clock tree synthesis)

)

)

詳細對比)

Java 工廠模式)

進程狀態)