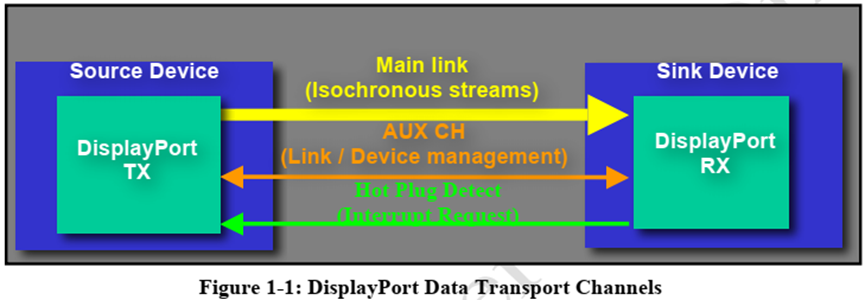

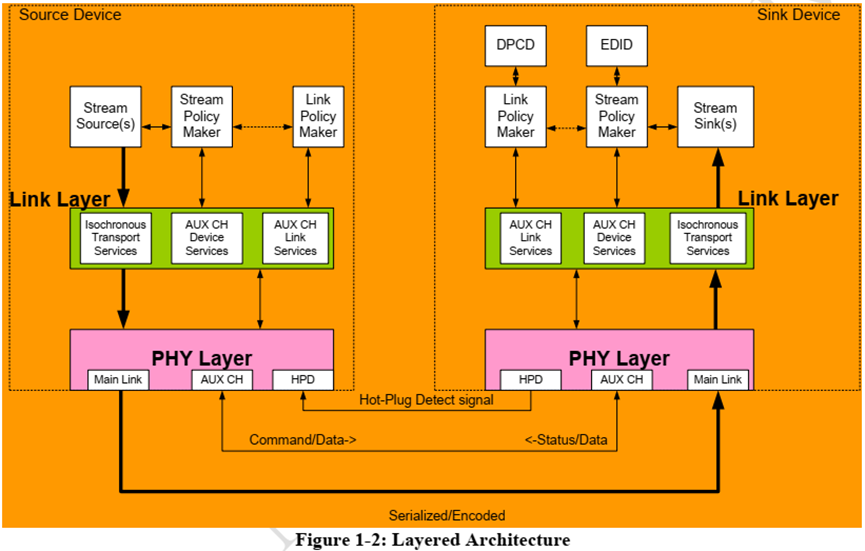

??DisplayPort(簡稱DP)是一個標準化的數字式視頻接口標準,具有三大基本架構包含影音傳輸的主要通道(Main Link)、輔助通道(AUX)、與熱插拔(HPD)。

??Main Link:用來傳輸各種類型的視頻數據和音頻數據,Main Link由1~4對差分線構成,這些數據線是單向的,從source指向sink。Main Link具體需要幾對數據線,取決于屏幕的分辨率和顏色位數。

??AUX:是一條獨立雙向半雙工的傳輸通道,它也是一對差分信號線。其數據傳輸速率1Mbps,用來傳輸配置參數與指令。具體來說它與EDID及DPCD存儲器相連,并通過總線方式讀寫。

??HPD:該項功能是可選的,實現中斷以及鏈路故障通知。

??DisplayPort1.4協議可以從以下地址下載https://download.csdn.net/download/cjie221/90649332。

1.結構框圖

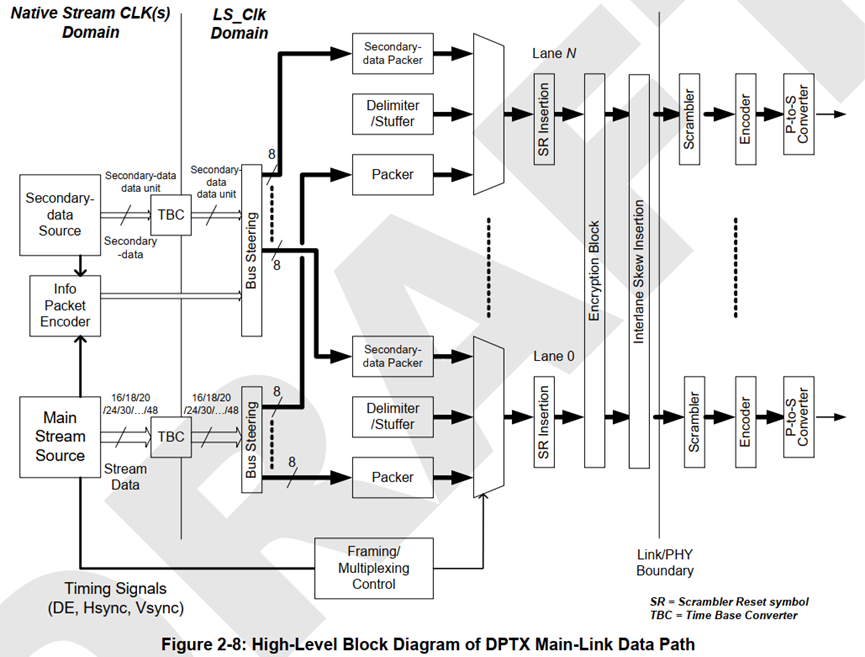

??我們根據DP1.4協議的DPTX框圖進行說明。在Main Link主通道中主要有視頻數據包和第二數據包。視頻數據包就是傳圖像數據,第二數據包用來傳輸音頻數據和其他控制數據,這里我們只介紹視頻數據包。另外DP視頻流傳輸還分為Multi-Stream Transport(MST)多流傳輸模式和Single-Stream Transport(SST)單流傳輸模式。這兩種模式數據格式差別很大。我們先從簡單的開始,這里只介紹SST模式。

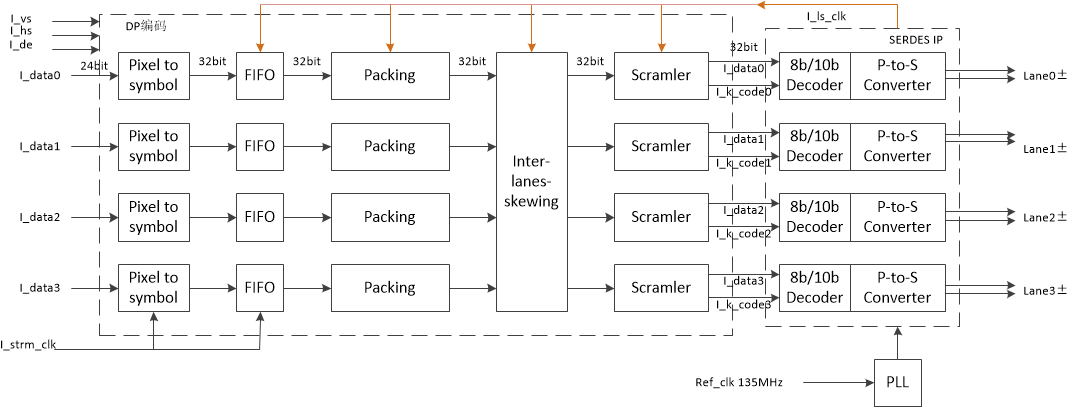

??從以下DPTX框圖中可以看出數據處理分成兩個時鐘域,一個是Stream CLK時鐘域,一個是LS CLK時鐘域。那么這里就涉及時鐘域轉換,一般用FIFO實現,并且還可以完成數據位寬的轉換。Stream CLK時鐘域是像素數據,數據位寬一般是24/30bit,LS CLK時鐘域是字節數據,一般是8bit,但在FPGA中實現時,為了降低時鐘頻率,往往采用數據位寬16/32bit。

??首先在Stream CLK時鐘域一般完成視頻數據接收,以及數據位寬轉換,然后存入FIFO中。

??其次在LS CLK時鐘域分別對每個lane的數據進行封包,然后是SR Insertion模塊。Encryption模塊就是HDCP加密模塊,加密模塊是可選項。之后是Interlane Skew通道偏移模塊,Scrambler擾碼模塊,還有8b/10b Encoder編碼模塊,最后是并串轉換。

2.實現原理

2.1數據排序

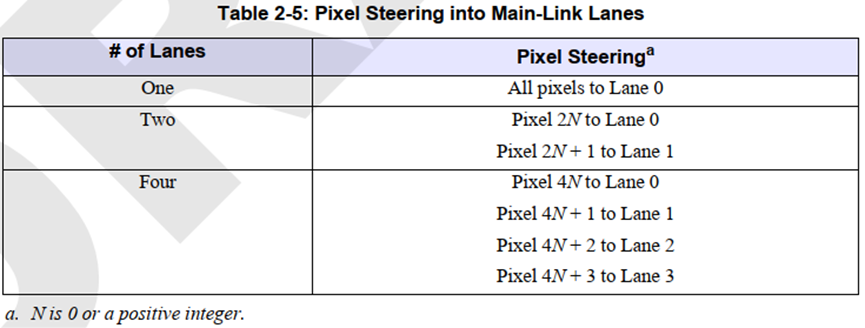

??根據DP協議主鏈路可支持1,2或4 lanes。無論視頻流的顏色空間和像素位深度如何,依照下表進行像素數據的填充。

??上面框圖中的Bus Steering模塊功能是就根據lane數對數據進行分配,可以在LS CLK時鐘域實現,也可以在Stream CLK時鐘域實現。

??甚至輸入視頻源直接根據lane數就按照相應的像素模式輸入,這樣實現更簡單。比如鏈路數為1 lane,視頻輸入數據為單像素模式,即每個像素時鐘傳輸1個像素。鏈路數為2 lanes,視頻輸入數據為雙像素模式,即每個像素時鐘傳輸2個像素。鏈路數為4 lanes,視頻輸入數據為四像素模式,即每個像素時鐘傳輸4個像素。這樣就可以不使用Steering模塊,每個像素直接送到各自的lane,存入相應的FIFO中。

2.2數據封包

??根據DP1.4協議,封包的數據是以符號Symbol為單位,一個Symbol 8bit,可以分為數據符號和控制符號。以下控制符號用于組幀。每個控制符號都是一個特殊的K碼。

? BS: Blanking Start,視頻消隱開始標志

? BE: Blanking End,視頻消隱結束標志,每行第一個有效視頻前插入

? FS: Fill Start,填充數據開始標志

? FE: Fill End,填充數據結束標志

? SS: Secondary-data Start,第二數據填充開始標志

? SE: Secondary-data End,第二數據填充結束標志

? SR: Scrambler Reset,SR symbol用來復位LFSR到初始值

? BF: Blanking Fill,增強幀模式填充標志

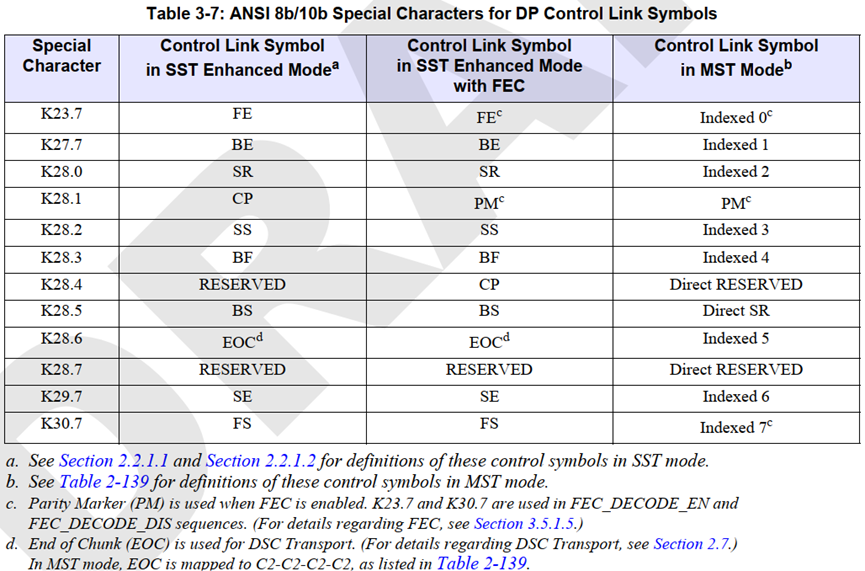

??在ANSI標準中8B/10B特殊K碼與控制符號對應關系如下表。

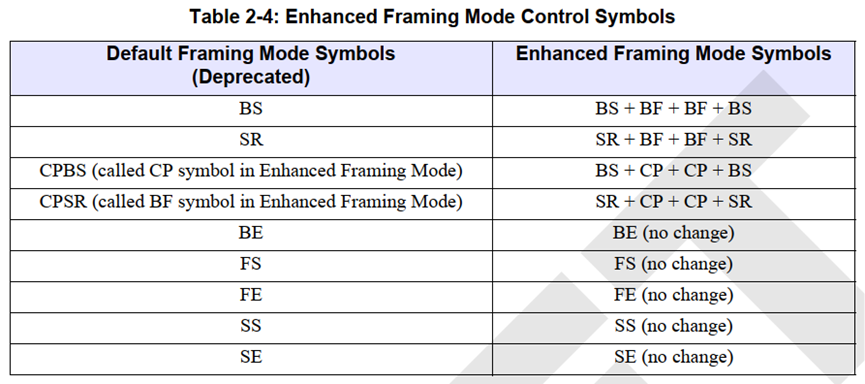

??在DP協議中,還有普通幀模式與增強幀模式區別,普通幀模式所有的控制符號都是1個K碼,增強幀模式部分控制符號是4個K碼的組合,具體控制符號差別如下表。

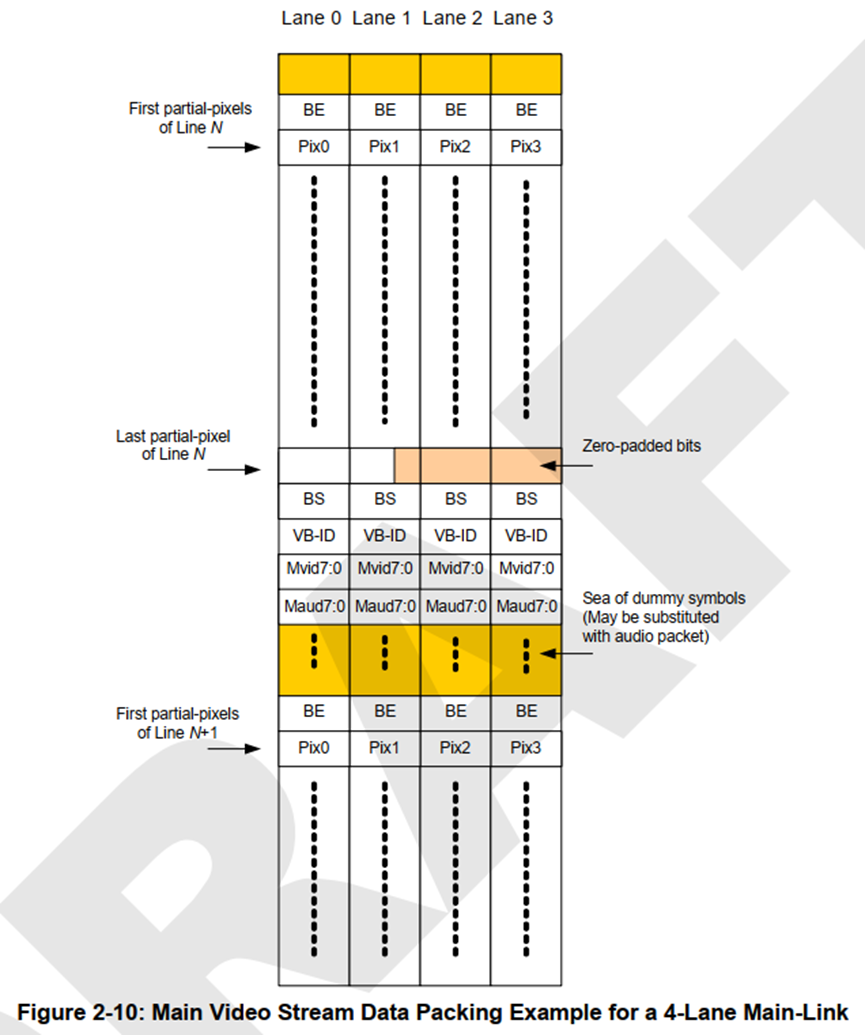

??視頻流數據封包格式如下圖所示。每個lane都從BE(消隱結束)控制符號開始,緊接著是視頻數據,然后是BS(消隱開始)控制符號,每個lane的BS后必須跟隨VB-ID,Mvid7:0和Maud7:0。之后填充數據零。

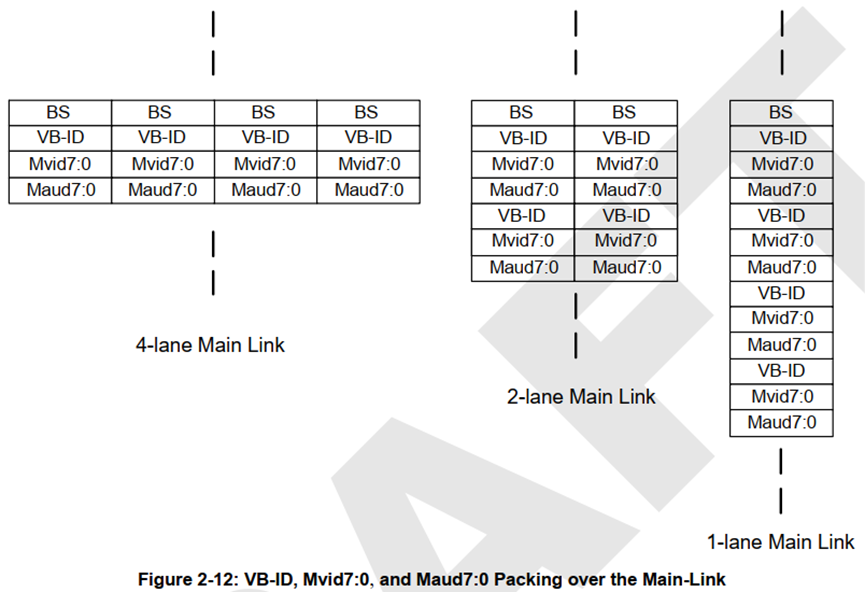

??無論lane數量是多少, VB-ID,Mvid7:0和Maud7:0 必須傳輸4次,如下圖所示。

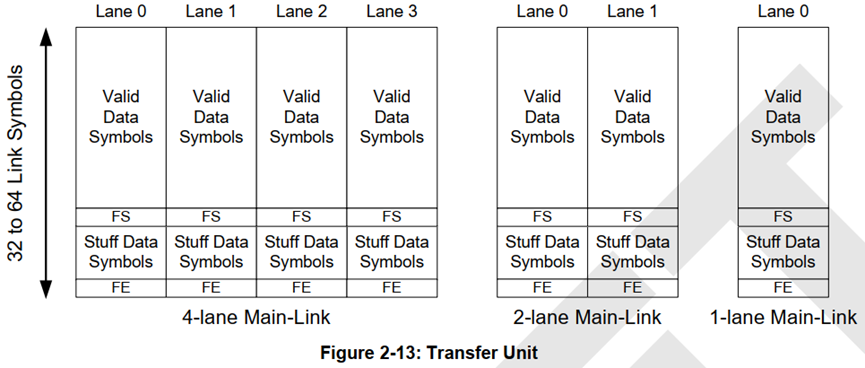

??在BE控制符號和BS控制符號之間的視頻數據采用一種叫Transfer Unit傳輸單元的方式傳輸。每lane的Transfer Unit的大小必須介于32~64個符號。

??因為數據打包速率(packed data rates)必須小于等于鏈路符號速率(link symbols rates)。當打包數據率低于鏈路符號率時,鏈路層必須執行符號填充(Symbols stuffing)。也就是說在TU中除了數據,還需要符號填充。

??符號填充由stuffing frame symbols和dummy data symbols組成。 Stuffing frame symbols 由FS符號和FE符號構成,位于每個TU (Transfer Unit)之內,dummy data symbols在擾碼之前必須是0x00,插在FS和FE之間,如下圖所示。

??注意,每行視頻數據最后一個TU不填充FS和FE,必須全部是視頻數據。

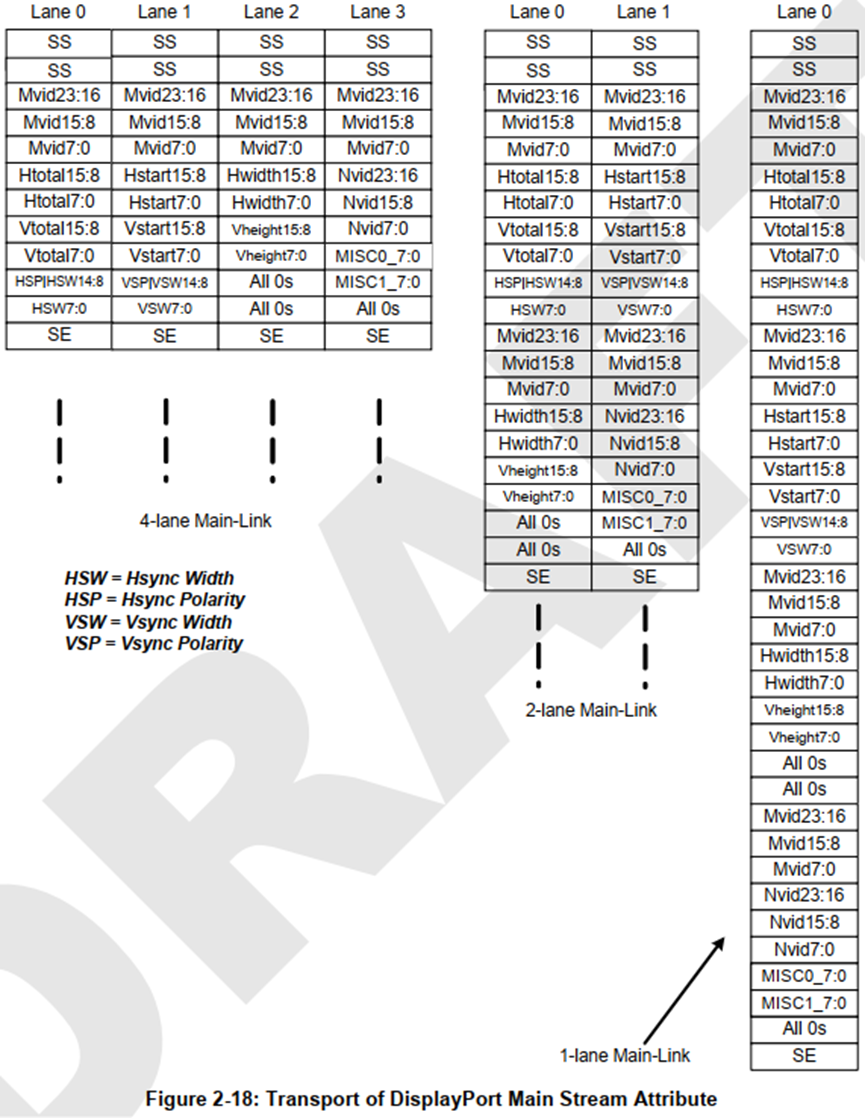

??還有DP傳輸的數據中必須包含視頻流的屬性信息,叫做主視頻流屬性數據Main Stream Attribute(MSA)在主視頻流的垂直消隱期間每幀發送一次。屬性數據包括以下:

(1) 用于視頻流時鐘恢復的M和N值(24bits each)

(2) 水平總點數和垂直總行數(16bits each)

(3) 水平有效開始點數和垂直有效開始行數(16bits each)

(4) 水平和垂直同步信號極性和寬度(1 bit for polarity and 15 bits for width)

(5) 水平有效點數和垂直有效行數(16bits each)

(6) 雜項0(MISC0, 8bits)

(7) 雜項1(MISC1, 8bits)

??通過每lane發送2個連續的SS符號開始,之后就是主流屬性數據,最后用SE結束。如下圖所示。第二數據包也是用SS符號開始,SE結束,只是區別開始時只用1個SS符號。

??根據以上規則,對1lane,2lane,4lane分別處理,在LS CLK時鐘域根據視頻輸入每行的等效長度進行計數,然后分別插入控制符號,以及視頻數據,從而完成數據封包。SR符號的插入也可以在封包時完成。

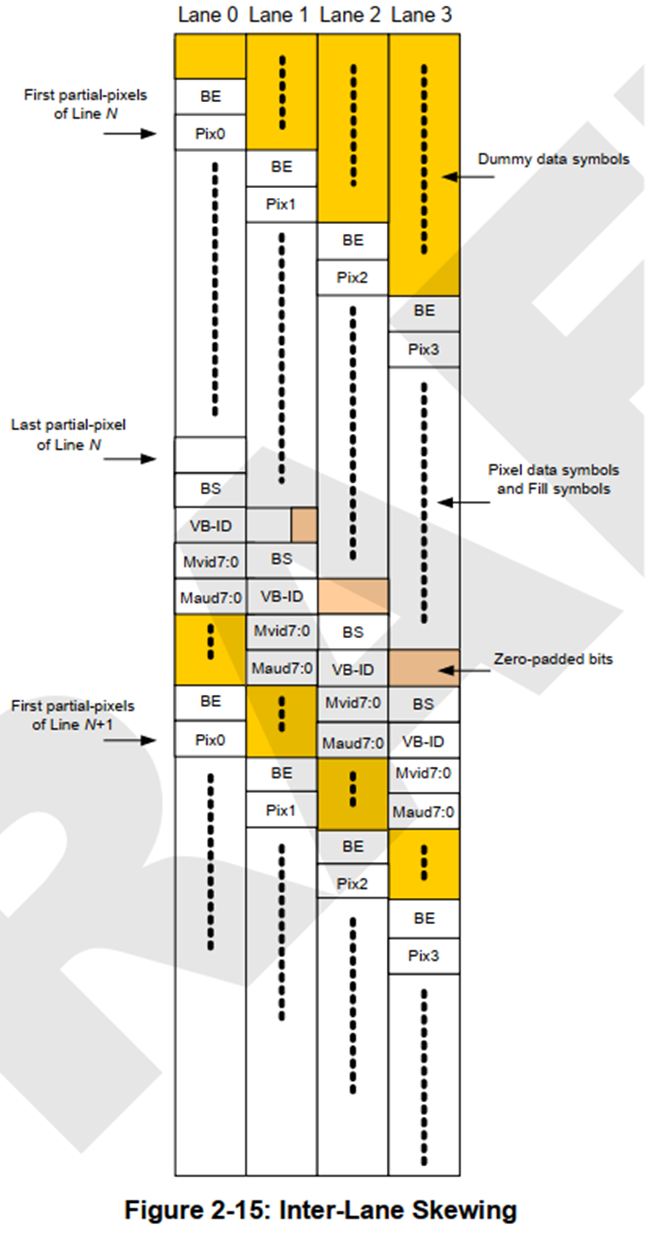

2.3通道間偏移

??相鄰lane必須插入2個鏈路時鐘LS Clk歪斜,目的是提高鏈路對外部噪聲的抗干擾能力,如下圖所示。

2.4擾碼

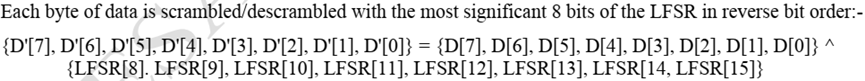

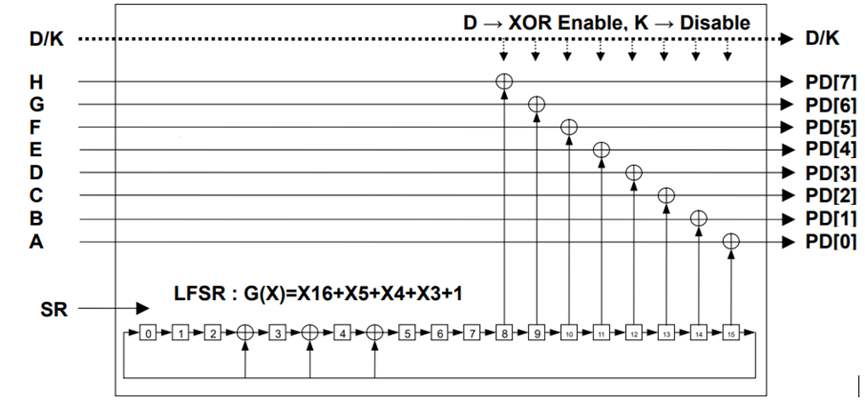

??為了減少EMI,在8B/10B編碼之前,需進行擾碼。16-bit LFSR的多項式為 G(X) = X16 + X5 + X4 + X3 + 1 。數據的每個字節都使用LFSR的最高有效 8 位以相反的位順序進行加擾/解擾。

??SR符號或SR BF BF SR符號序列被用于復位LFSR至初始值FFFFh(或在eDP標準下初始值為FFFEh)。

3.實現框架

??根據上述的分析,我們可以將DPTX對應到如下的框架。首先根據lane數,將輸入視頻數據按對應的像素模式輸入,最多是四像素模式。之后是pixel to symbol模塊,將像素位寬轉成符號位寬。然后存入FIFO。LS CLK時鐘域用32bit目的是為了降低處理時鐘頻率。之后是封包模塊,最復雜的操作就在此模塊,按行等效長度進行計數,在不同的計數位置,插入控制符號,或者從FIFO中讀取視頻數據插入。通道間偏移相對簡單,寄存器打拍移位就可實現。擾碼模塊參考DP協議附錄,按并行模式實現即可。

??因為大多數SERDES IP都集成了8b/10b編解碼,所以可以不用單獨開發8b/10b編碼模塊,直接利用SERDES IP就可以實現。至于SERDES IP為什么用135MHz做參考時鐘,因為DP的常見速率1.62Gbps/lane(RBR),2.7Gbps/lane(HBR),5.4Gbps/lane(HBR2),8.1Gbps/lane(HBR3)與135MHz都有倍數關系,PLL比較容易產生相應時鐘頻率。當然如果非要用其他如100MHz時鐘做參考時鐘,也是可以的,只是有可能PLL輸出時鐘精度不準,有可能會影響到sink端數據解串。

)

/ 字符串分類(字符串哈希) / 城市群數量(dfs))

之條件語句)

:基于多尺度注意力TCN-KAN與小波變換的時間序列預測模型)