作為信息處理的第一步,數據采集的作用越來越重要。目前,數據采集已經在航

空、民用、軍事、醫療等領域得到廣泛應用。隨著相關技術的不斷發展,信號頻率越

來高,帶寬越來越大,使得數據采集技術逐漸向高速大數據的方向發展。在電子對抗

應用中,各種復雜寬帶雷達體制的出現,使得電磁信號在空間中更為復雜。在復雜電

磁空間中識別出特定信號,首先需要高速 ADC 對電磁信號進行采樣,然后經過高速

數據傳輸至處理器進行數據處理和分析,以便獲取電磁信號里面的信息。通常由高速

數據采集卡完成電磁信號的采集和傳輸,而數據處理既可以由采集卡內高性能的處理

器完成,也可以將數據保存,由 PC 機后續完成。

目前處理器主要有 FPGA 、 ARM 、 DSP 、 PowerPC 等,并且大多數處理器提供高

速串行接口,以實現高速數據傳輸。高速串行接口是以多通道的差分對進行傳輸,與

傳統并行總線相比,高速串行接口具有抗干擾能力強,速度高的特點,避免了并行總

線的串擾和同步問題 [1] 。 ARM 和 DSP 等處理器是基于 CPU 的架構的,每一時刻只能

執行一條命令。而 FPGA 是以數字電路為基礎的芯片,各個模塊之間的工作不會受影

響,因此 FPGA 的并行處理性能是 ARM 、 DSP 等處理器無法比擬的 [2] ,然而 FPGA

不適合用來數據處理,通常搭配 ARM 或 DSP 來進行數據處理。

通常采集卡通常使用 FPGA+ARM 或 FPGA+DSP 的處理架構, FPGA 完成信號

的采集和傳輸, ARM 或 DSP 用來對數據進行處理。由于這種架構使得處理器分離,

使這種結構的電路設計更為復雜,并且軟件設計需要不同的開發平臺,因此開發的周

期較長。本設計采用 Zynq7000 系列 SoC 為主控芯片,該芯片內部為 FPGA+ARM 的

架構,封裝至一個芯片內 [3] 。電路設計簡單,而且用一個平臺就可以實現 FPGA 和

ARM 的功能,大大節省了開發時間。采集卡的接口通常采用以太網口或 PCIE 接口,

以太網口的傳輸速度較慢,不適合高速數據的傳輸。而 PCIE 接口可輕松實現幾十

Gbps 的傳輸速率,在高速數據采集卡方面得到廣泛應用。

本課題針對雷達輻射源的高速數據采集需求,設計并實現了一種 PCIE 高速數據

采集卡。使用 Zynq7000 SoC 芯片作為處理芯片,采用 PCIE2.0 協議完成采集卡與雷

達輻射源信號識別平臺之間的數據交互,使用 DDR3 SDRAM 實現數據的緩存功能,

最終實現了最高 40Gbps 的數據傳輸速率。本設計為高速信號采集和傳輸提供了一種

設計思路和實現方法,具有一定的意義和參考價值。

1.2 國內外相關課題研究和發展現狀

1.2.1

高速數據采集卡現狀

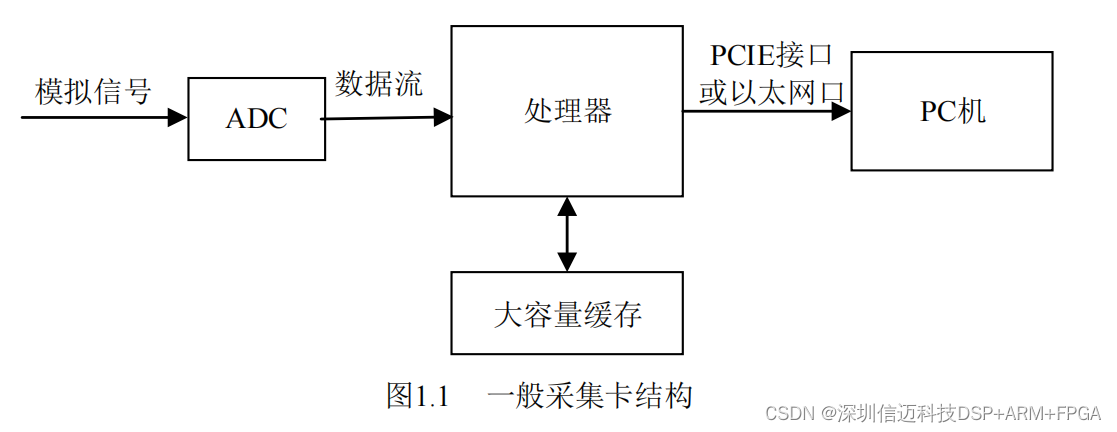

一般的高速數據采集卡采用如圖 1.1 所示的結構,模擬信號經 ADC 采集后進入

處理器,數據經過緩存、處理后可以通過 PCIE 接口或者以太網口接入電腦。處理器

通常采用 FPGA+DSP 或者 FPGA+ARM 的架構。其中, FPGA 用來完成數據采集工

作, DSP 和 ARM 負責完成數據處理工作;大容量緩存一般采用 DDR2 芯片或者 DDR3

芯片,用來暫存數據。采樣的數據也可直接由高速 PCIE 接口之間傳輸至 PC 機,供

下一步處理。高速數據采集依賴于高速 ADC 和高速總線的發展,下面詳細說明一下

ADC 的發展現狀和處理器的架構。

)

)

)