單周期路徑

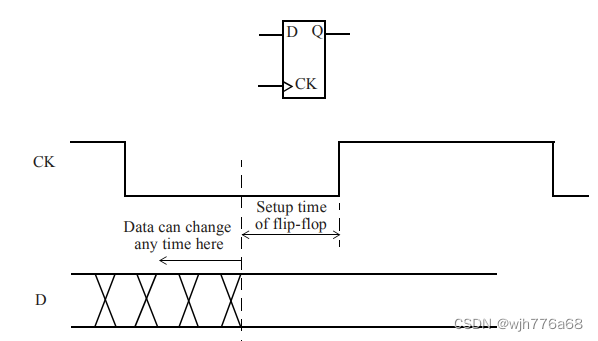

建立時間時序檢查

在時鐘的有效沿到達觸發器之前,數據應在一定時間內保持穩定,這段時間即觸發器的建立

時間。滿足建立時間要求將確保數據可靠地被捕獲到觸發器中。

建立時間檢查是從發起觸發器中時鐘的第一個有效沿到捕獲觸發器中時鐘后面最接近的那個有效沿。

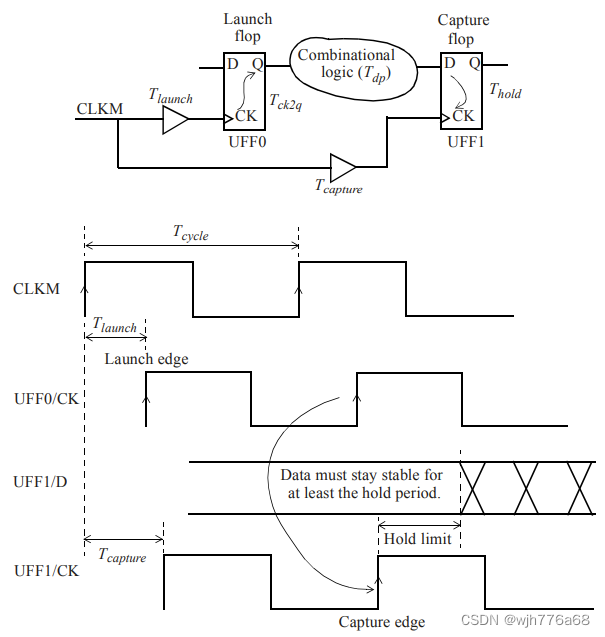

觸發器到觸發器路徑

建立時間檢查可以用數學公式表示:

Tlaunch + Tck2q + Tdp < Tcapture + Tcycle - Tsetup

其中Tlaunch是發起觸發器UFF0的時鐘樹延遲,Tdp是組合邏輯數據路徑的延遲,Tcycle是時鐘周期,Tcapture是捕獲觸發器UFF1的時鐘樹延遲。

觸發器間可能存在多條路徑,每條路徑均需滿足建立時間的要求,這等價于在延時最高的工作條件(PVT)下,觸發器間的最長時序路徑需要滿足建立時間的要求。因此在時序報告中建立時間用-max表示。

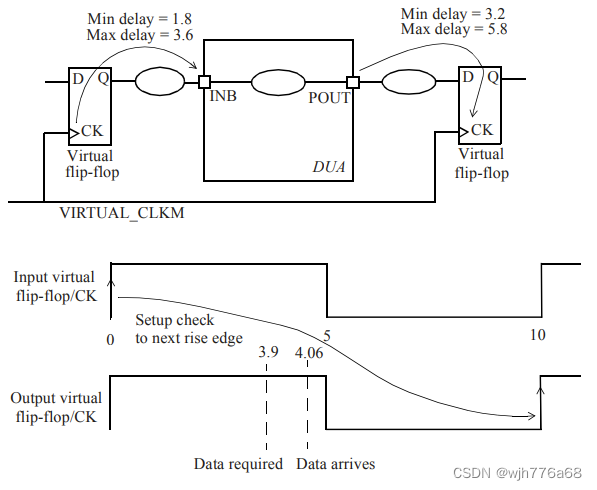

輸入引腳到觸發器路徑

輸入引腳數據采用虛擬時鐘發出

輸入引腳數據采用實際時鐘發出

觸發器到輸出引腳路徑

輸出引腳數據采用虛擬時鐘捕獲

輸入引腳到輸出引腳路徑(組合邏輯路徑)

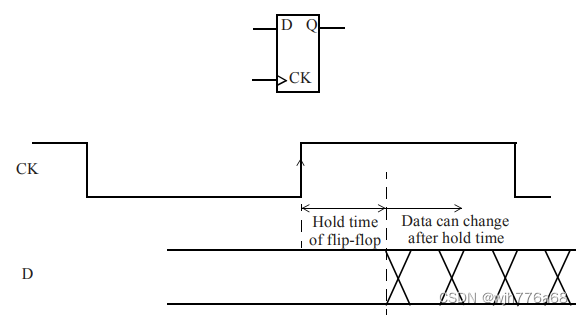

保持時間時序檢查

觸發器的保持時間要求規定在時鐘的有效沿之后的指定時間段內,被鎖存的數據應保持穩定。

保持時間檢查可確保正在變化的觸發器輸出值不會傳遞到捕獲觸發器,并在捕獲觸發器有機會捕獲其原始值之前覆蓋其輸出。

觸發器到觸發器路徑

保持時間檢查可以用數學公式表示為:

Tlaunch + Tck2q + Tdp > Tcapture + Thold

其中Tlaunch是發起觸發器的時鐘樹延遲,Tdp是組合邏輯數據路徑中的延遲,Tcapture是捕獲觸發器的時鐘樹延遲。換句話說,由時鐘邊沿發起的數據到達捕獲觸發器D引腳所需的總時間必須大于時鐘同一邊沿到達捕獲觸發器所需的時間加上保持時間。這樣可以確保UFF1 / D保持穩定狀態,直到觸發器的時鐘引腳UFF1 / CK時鐘上升沿之后的保持時間為止。

觸發器間可能存在多條路徑,每條路徑均需滿足保持時間的要求,這等價于在延時最低的工作條件(PVT)下,觸發器間的最短時序路徑需要滿足保持時間的要求。因此在時序報告中建立時間用-min表示。

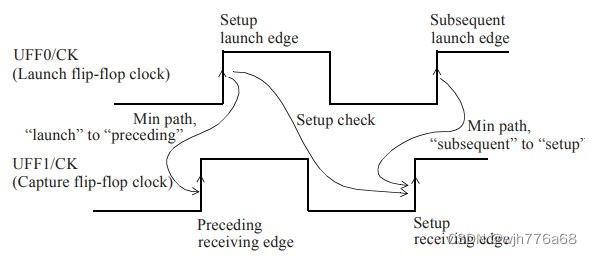

保持時間檢查需要確保:

- 當前數據發起時鐘沿(Setup launch edge)的下一個(subsequent)時鐘沿發起的數據不被當前數據捕獲時鐘沿(Setup receiving edge)所捕獲。

- 當前數據發起時鐘沿發起的數據不被當前數據捕獲時鐘沿的前一個(Preceding)時鐘沿所捕獲。

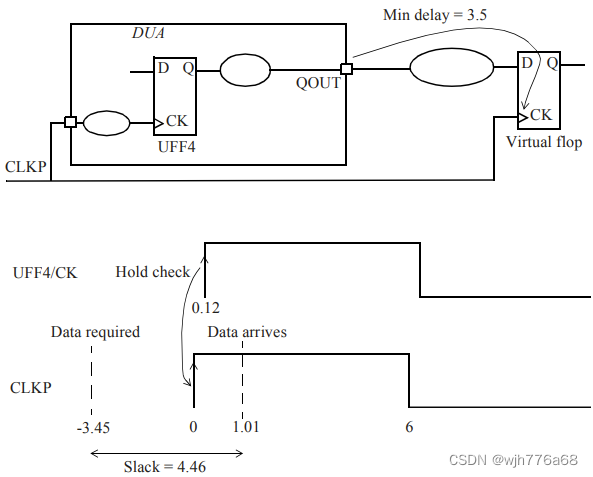

觸發器到輸出引腳路徑

輸出引腳數據采用已知時鐘捕獲

多周期路徑

兩個觸發器之間的數據路徑可能需要一個以上的時鐘周期才能傳播通過邏輯。在這種情況下,這條組合邏輯路徑會被定義為多周期路徑。這意味著設計中后繼觸發器每隔多個周期才會使用一次前級觸發器輸出引腳上的數據,而不是每個周期都使用。

create_clock -name CLKM -period 10 [get_ports CLKM]

set_multicycle_path 3 -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

偽路徑

-

利用已知/可預測時鐘對信號采樣時,盡量用多周期路徑代替偽路徑約束。

-

盡量不用-through復雜性高。

-

若要在兩個時鐘域之間設置偽路徑,使用get_clocks效率更高:

set_false_path -from [get_clocks clockA] -to [get_clocks clockB]

??代替

set_false_path -from [get_pins {regA_ * }/CK] -to [get_pins {regB_ * }/D]

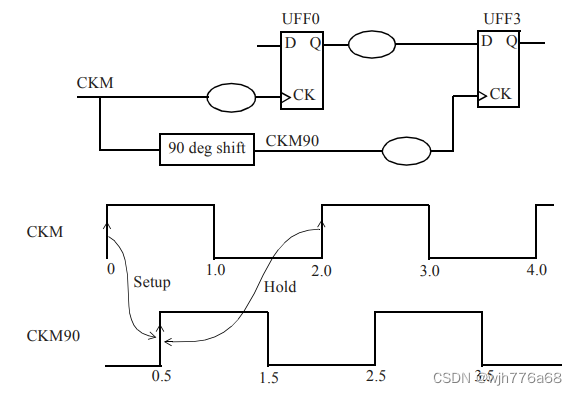

半周期路徑

設計中同時具有負邊沿觸發的觸發器(有效時鐘沿為下降沿)和正邊沿觸發的觸發器(有效時鐘沿為上升沿),則設計中可能存在半周期路徑。

半周期路徑的建立時間、保持時間捕獲時鐘沿與發起時鐘沿偏移均為半個時鐘周期。

撤銷時間檢查

撤銷時間檢查用于確保在有效時鐘沿與釋放異步控制信號之間有足夠的時間。類似于保持時間檢查。

恢復時間檢查

恢復時間檢查用于確保異步信號變為無效狀態的時刻與下一個有效時鐘沿之間的時間間隔大于一個最

小值。類似于建立時間檢查。

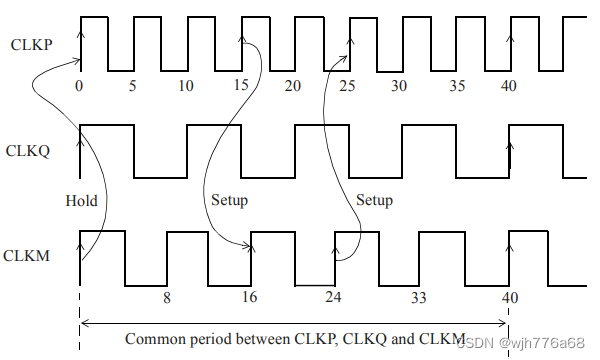

跨時鐘域

當數據發起觸發器和捕獲觸發器的時鐘頻率不同時,STA會首先確定一個公共基本周期(common base period)。快時鐘的時鐘周期會被延拓,以便獲得兩個時鐘的一段公共周期。

慢時鐘到快時鐘

對于nMHz的慢時鐘到4nMHz的快時鐘數據傳輸:

假設該設計的目的是在CLKP的每隔第4個捕獲沿上捕獲數據,且數據發起沿后數據會發生變動,即需要將保持時間檢查一直移回到數據發起沿所在位置,對應波形圖如下:

對應上述波形圖可使用的多周期約束如下。

set_multicycle_path 4 -setup -from [get_clocks CLKM] -to [get_clocks CLKP] -end

set_multicycle_path 3 -hold -from [get_clocks CLKM] -to [get_clocks CLKP] -end

其中-end表示依照捕獲時鐘沿,默認情況下-setup使用-start即發起時鐘沿,-hold使用-end即捕獲時鐘沿。使用-end時會從默認的捕獲時鐘沿開始前移指定倍數周期,使用-start會從默認的發起時鐘沿后移指定倍數周期。

快時鐘到慢時鐘

如果設計能夠支持放寬建立時間檢查要求,為數據路徑提供兩個快時鐘周期,此時波形圖如下:

此時多周期路徑約束如下:

set_multicycle_path 2 -setup -from [get_clocks CLKP] -to [get_clocks CLKM] -start

set_multicycle_path 1 -hold -from [get_clocks CLKP] -to [get_clocks CLKM] -start

多時鐘域

不同頻率

- 整數倍:設計中多個時鐘的頻率是彼此的整數倍。在這種情況下,會通過計算所有相關時鐘之間的公共基本周期,以便所有時鐘同步。

- 非整數倍:對于兩個頻率不是彼此整數倍的時鐘域之間存在數據路徑的情況,時序分析會先計算相關時鐘的公共周期,然后再將時鐘擴展到該公共周期。之后,建立時間檢查在時鐘發起沿和捕獲沿之間的最短時間內進行(根據建立時間不等式,兩沿最短時檢查最嚴格)。保持時間檢查在發起時鐘沿對應捕獲時鐘沿的前一周期與當前發起時鐘沿最小時進行。

不同相位

0.5.000)

)

)