相關閱讀

靜態時序分析![]() https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

目錄

指定值

指定端口/引腳列表

簡單使用

? ? ? ? set_case_analysis命令用于對電路進行特定模式的設定,例如對于一個工作在正常模式下的芯片,其掃描觸發器的測試引腳應該設定為0;對于一個時鐘選擇器的選擇引腳,在特定模式工作時應該為確定值。這個命令很有用,因為它可以幫助減少很多不必要的時序路徑分析。

????????set_case_analysis指令的BNF范式(有關BNF范式,可以參考以往文章)為:

set_case_analysisvalue port_or_pin_list//注:該命令的port_or_pin_list參數一定要放在value參數后? ? ? ? 該命令可以指定端口或引腳處是恒定的1或0,或者端口或引腳處僅允許上升沿或下降沿。

指定值

? ? ? ? 參數value指定了端口或引腳處的確定值或轉換方向。對于確定值,它可以是1、0、one或zero。對于轉換方向,它可以是rising、falling、rise或fall。

指定端口/引腳列表

????????指定一個端口/引腳列表,包含端口對象或引腳對象,如果有多于一個對象,需要使用引號或大括號包圍。

簡單使用

? ? ? ? 首先我們可以解決靜態時序分析:SDC約束命令create_clock詳解一文中出現的時序路徑混亂問題,原文的圖7如本文圖1所示,首先在輸入端口clk_1和clk_2定義兩個時鐘。

create_clock -period 10 [get_port clk_1]

create_clock -period 15 [get_port clk_2]

圖1?有兩個時鐘驅動的電路單元

? ? ? ? 對于上面的電路,本意是b_reg觸發器和c_reg觸發器同時受時鐘clk_1或時鐘clk_2之一觸發,但如果不使用set_case_analysis命令,在使用report_timing命令后會出現時鐘clk_2和時鐘clk_1之間的時序分析報告,如圖2、圖3所示,我們真正需要的是圖4的時序報告。

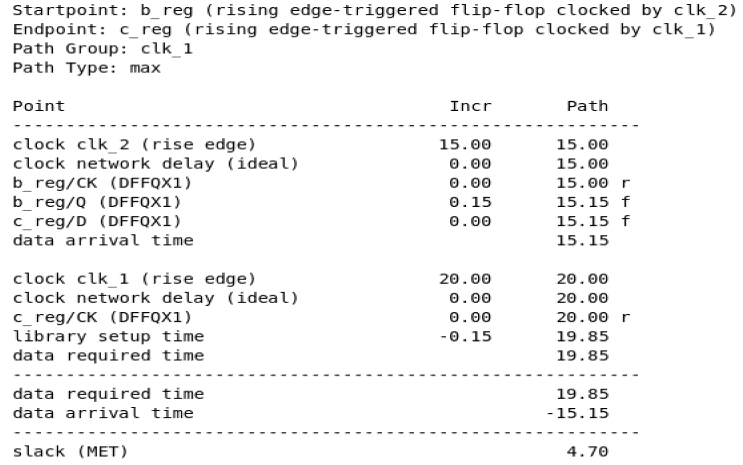

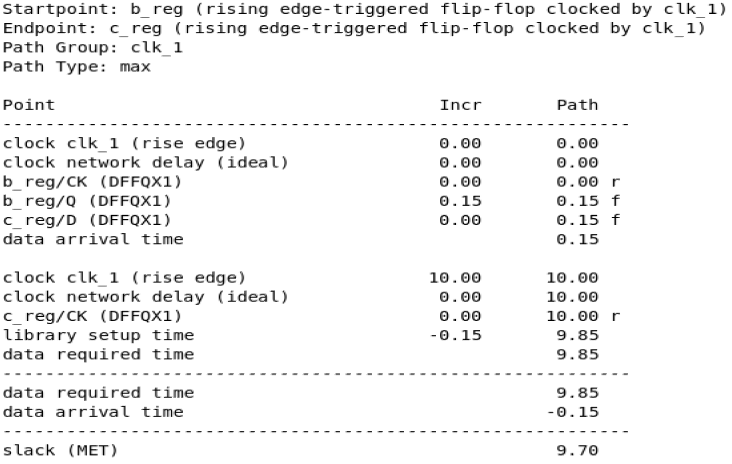

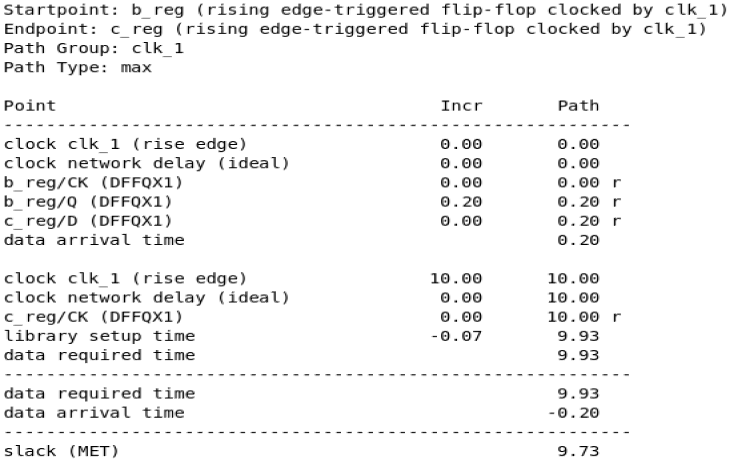

圖2 發射時鐘是clk_2,捕獲時鐘時clk_1

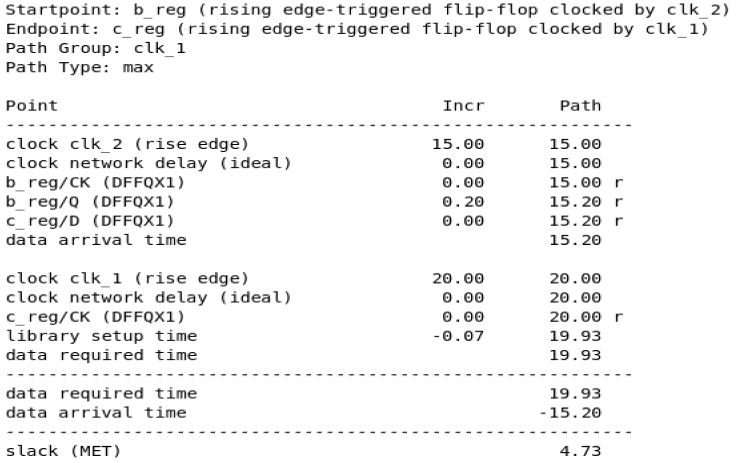

圖3?發射時鐘是clk_2,捕獲時鐘時clk_1

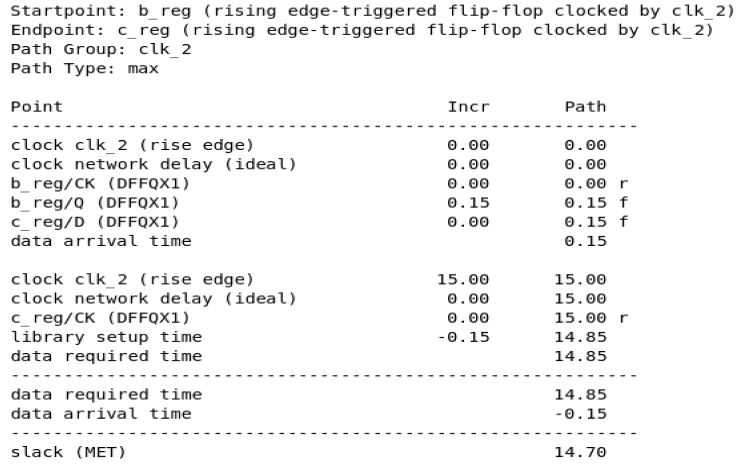

圖4?發射時鐘是clk_2,捕獲時鐘是clk_2

? ? ? ? 下面我們使用set_case_analysis命令,固定選擇端sel的信號為0,時序分析結果如圖5和圖6所示。

set_case_analysis 0 [get_port sel]

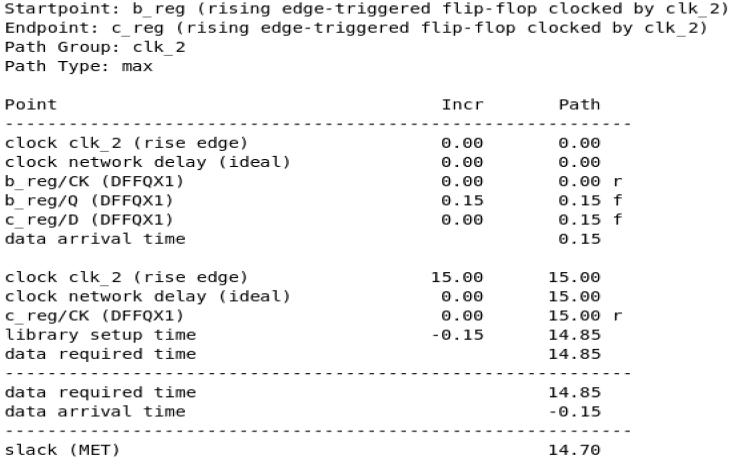

圖5 發射時鐘和捕獲時鐘都是clk_2

圖6?發射時鐘和捕獲時鐘都是clk_2

????????下面我們使用set_case_analysis命令,固定選擇端sel的信號為1,時序分析結果如圖7和圖8所示。?

set_case_analysis 1 [get_port sel]

圖7?發射時鐘和捕獲時鐘都是clk_1

圖8?發射時鐘和捕獲時鐘都是clk_1

? ? ? ? set_case_analysis命令還會導致設定的值沿著時序路徑向后傳播,從而打斷某些時序路徑(使這些路徑不能出現信號翻轉),例如對于圖9所示的電路圖。

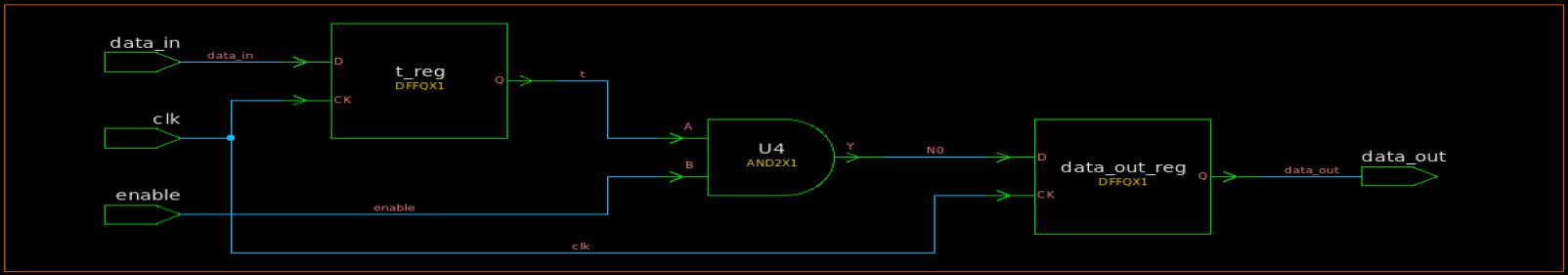

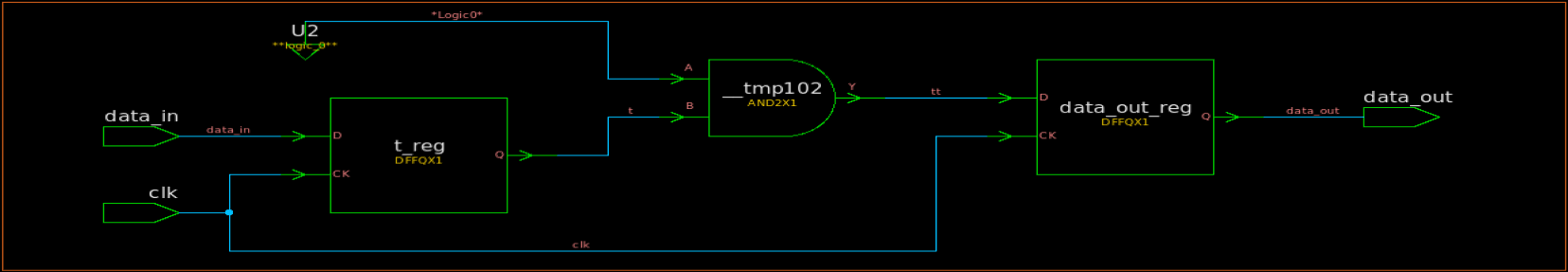

圖9 一個簡單的例子

????????首先在輸入端口clk定義一個時鐘。

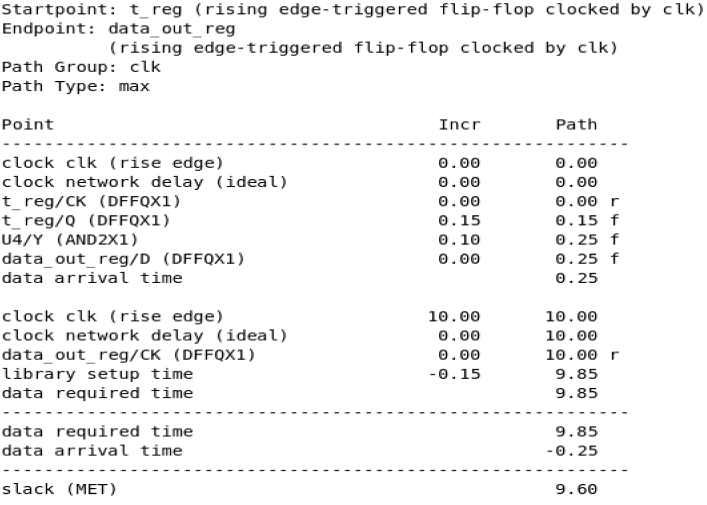

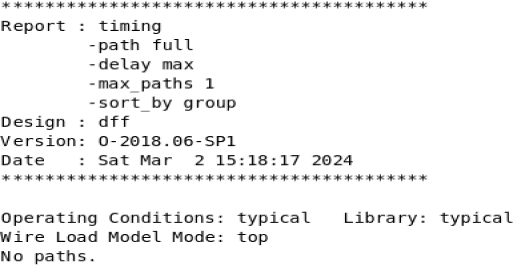

create_clock -period 10 [get_port clk]? ? ? ? ?此時如果直接使用report_timing命令,則t_reg和data_out_reg之間的時序路徑會正常報告,如圖10所示。

圖9 兩個觸發器間的時序報告

? ? ? ? 現在我們使用set_case_analysis命令固定使能信號enable為0,這就使得與門U4的輸出固定為0,無法翻轉,因此t_reg和data_out_reg之間的時序路徑被打斷了,如圖10所示。

圖10?兩個觸發器間的時序路徑被打斷了

? ? ? 這就相當于編寫Verilog代碼時,直接將與門的一個輸出引腳固定為0,這也會打斷時序路徑(假設電路沒有被邏輯優化),如圖11所示的電路圖。

圖11 編寫代碼時指定引腳值為0

? ? ? ? 在圖11中,我們設法使得某些器件不被優化掉,并構造了一個奇怪的電路圖。此時在邏輯上講,與門的輸出是一個固定值0,此時使用report_timing命令無法看到t_reg和data_out_reg之間的時序路徑,如圖12所示。

圖12?兩個觸發器間的時序路徑被打斷了

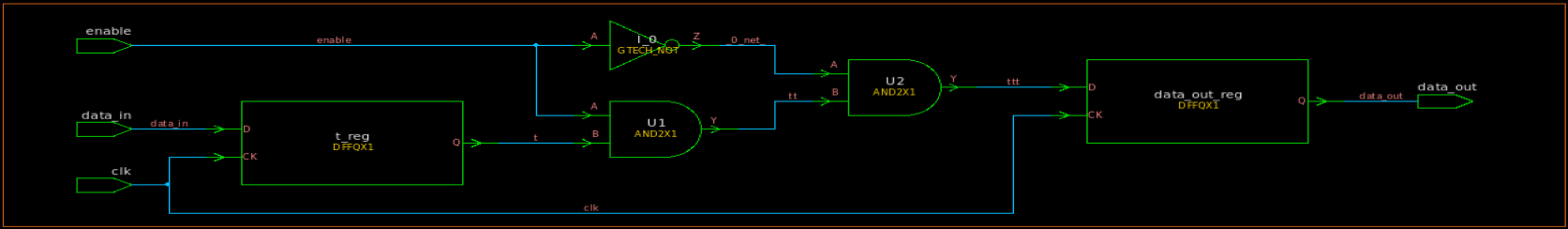

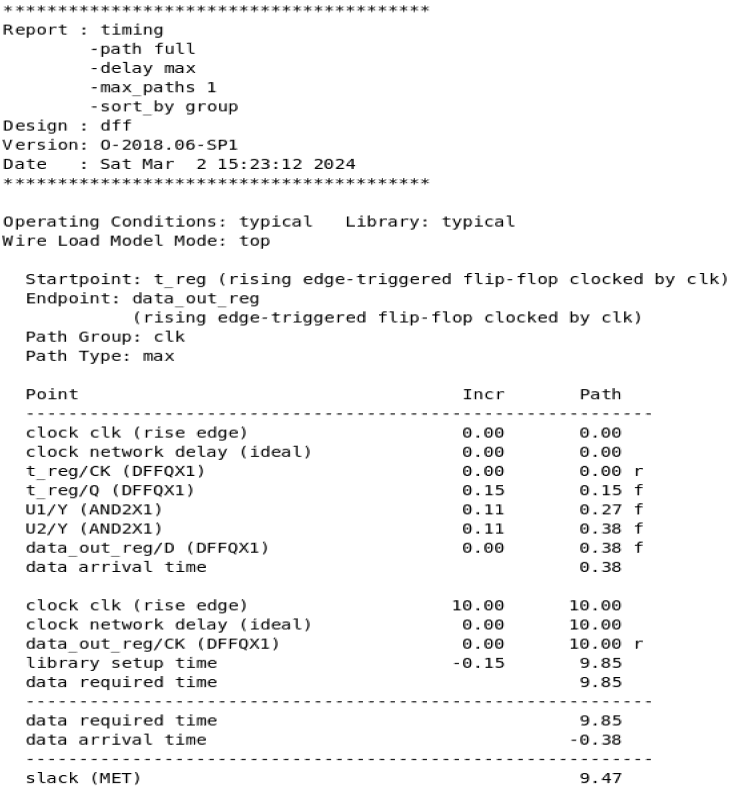

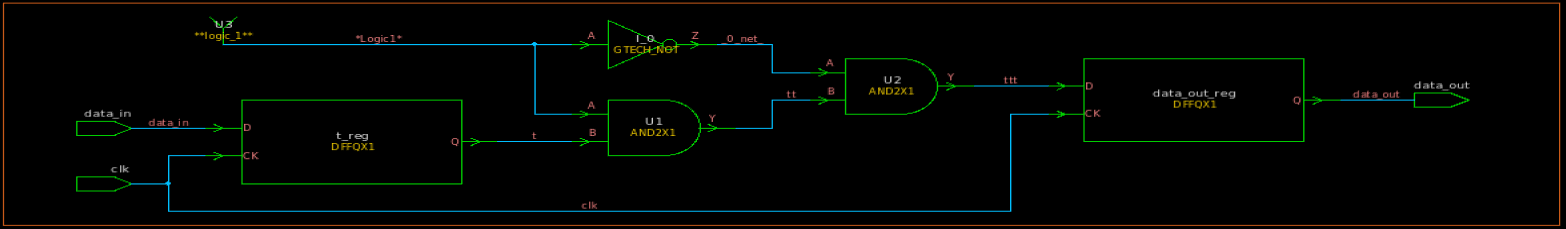

? ? ? ? 但是我們再來看一下圖13所示的電路圖(假設電路沒有被邏輯優化),可以看出與門U2的輸出是一個固定值0,但是此時使用report_timing命令可以看到t_reg和data_out_reg之間的時序路徑,如圖14所示。這代表了,即使DC會考慮某些情況下電路的邏輯情況,但不是所有。

圖13?與門U2的輸出引腳值為0

圖14?兩個觸發器間的時序報告

? ? ? ? 如果此時在編寫Verilog代碼時又將enable信號固定為1(假設電路沒有被邏輯優化),則時序路徑又會被打斷,如圖15所示。

圖15?編寫代碼時指定引腳值為0

? ? ? ? ?這代表著,如果在寫Verilog時固定了某個電路中某個引腳或端口的信號值,則這個確定值也會沿著時序路徑傳播,并可能打斷路徑,但推薦使用set_case_analysis命令來完成這一目標。

? ? ? ? 最后要注意的是,確定值的傳播會在到達時序路徑終點而停止,并不會繼續傳播下去,比如圖15中的data_out_reg到輸出端口的時序路徑并不會因為與門U2的輸出為確定值0而被打斷。

)

)

)

求解23個基準函數)

)