上節中介紹的ALU進行計算后得到的結果需要對其進行存儲,可能還要進行多個連續操作,這就需要用到計算機內存了。計算機使用的是隨機存取存儲器(Random Access Memory, RAM),其只能在有電的情況下存儲東西。另一種存儲稱為持久存儲(Persistent Memory),電源關閉時數據也不會丟失,它用來存其他東西。

這一節中首先構建能夠存儲1位的存儲器,然后對其擴展來得到內存模塊。

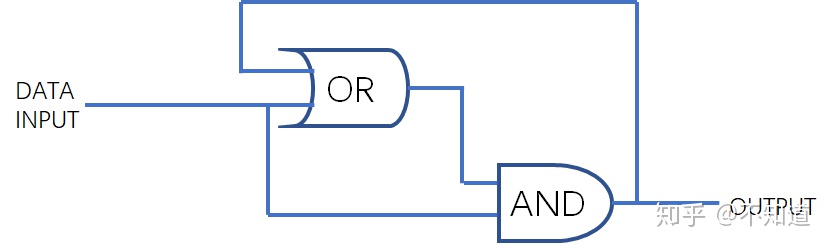

之前構建的都是單向電路,我們同樣可以構建回向電路,把輸出連回輸入。

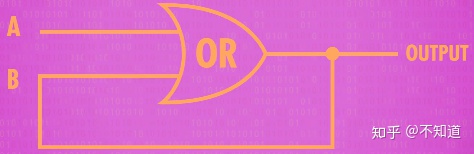

當將OR門構建成回向電路時,可以分析其電路特性

- A和B初始為0時,輸出結果為0

- 將A修改為1時,輸出結果為1,此時B的輸入就變為了1。隨后輸出始終保持為1,不論A如何變化。

所以這個電路能夠永久記錄1,并且無法將1變回0。

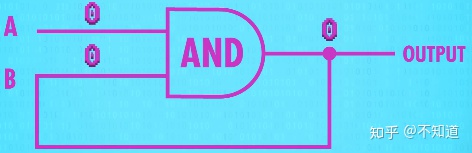

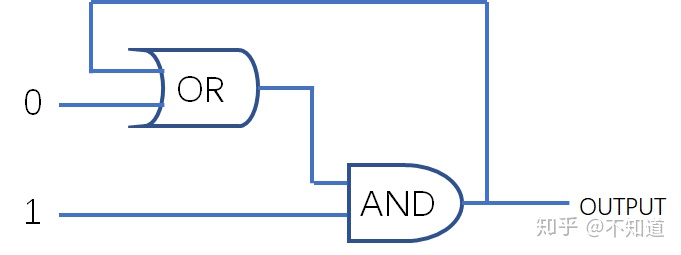

同理可以分析下AND門構建成回向電路時的特點

- A和B初始化為1,則輸出結果為1

- 將A修改為0時,輸出結果為0,此時B的輸入就變成了0。隨后輸入始終保持為0,無論A如何變化。

所以這個電路能夠永久記錄0,并且無法將0變回1。

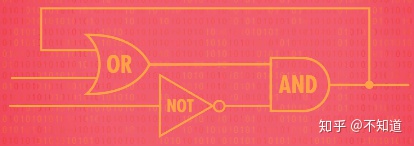

所以我們就得到了能夠存儲1和0的電路,為了得到有用的Memory,需要將兩個電路結合起來,可以得到AND-OR鎖存器(AND-OR Latch),上方的是SET輸入,下方的是RESET輸入,當SET=1、RESET=0,就能將輸出設置為1,當RESET=1,就能將輸出設置為0,當SET=0、RESET=0,則輸出最后放入的內容。由此能夠存儲1位的信息(該信息存儲在OR門上方的輸入電極中)!

技巧:當OR門其中一個輸入為0,或AND門其中一個輸入為1,則相當于另一個輸入直接穿過這個門。當OR門其中一個輸入為1,則直接輸出1;當AND門其中一個門為0,則直接輸出0。

這叫"鎖存", 因為它"鎖定"了一個值,放入數據的動作叫 "寫入" ,拿出數據的動作叫 "讀取"。

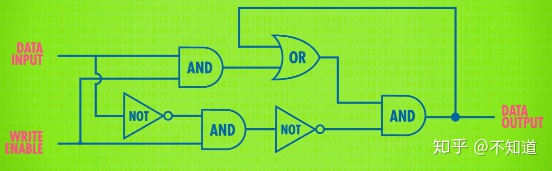

對其進行SET和RESET進行合并,并添加其他門控單元,可以得到一個門鎖(GATE LATCH)

其中DATE INPUT表示數據輸入,WRITE ENABLE表示允許寫入線,用來控制是否保存當前輸入的數據。對這個電路進行分析。

- 當WRITE ENABLE=1時,電路可以化簡為以下形式。當數據輸入為0時,AND門可以忽略OR門的輸出,直接輸出0,并且OR門上方電極也將保存0。當數據輸入為1時,相當于忽略了AND門,OR門的輸出直接和OUTPUT相連,OR門輸出1,并且OR門上方電極也將保存1。所以,當WRITE ENABLE=1時,數據輸入會直接傳到輸出,而且數據輸入會保存在OR門的上方電極,進行數據存儲。

2. 當WRITE ENABLE=0時,電路可化簡為以下形式。此時能夠忽略AND門,直接將OR門的輸出當做OUTPUT,而OR門的輸出其實就是上方電極的數據,由于上方電極就是當前OUTPUT的數據,所以會保持OUTPUT不變。所以,當WRITE ENABLE=0時,會忽略數據輸入,保持OUTPUT不變。

可以將門鎖進行抽象,得到一個能夠存儲一個bit的部件。當允許寫入線為0時,輸出保持不變,當允許寫入線為1時,輸出就是數據輸入,并且能夠將數據輸入進行存儲。

如果我們并排8個鎖存器,就能存儲8位信息。一組這樣的鎖存器稱為寄存器(Register),寄存器能夠存一個數字,這個數字的位數稱為寄存器的位寬(Width)。

寫入寄存器之前,要先啟動里面所有的鎖存器,可以將所有鎖存器的允許寫入線都連接在一起,把它設為1,然后用8條數據線發送數據,然后將允許寫入線設回0,就能將8位數據存儲在寄存器中。

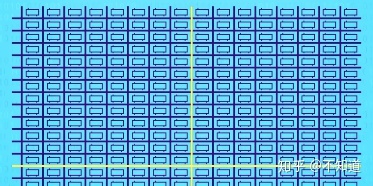

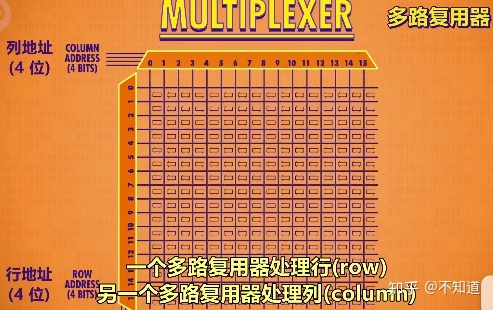

但是通過這種形式排列鎖存器需要太多的線路,64位寄存器需要129條線,256位寄存器需要513條線,可以通過矩陣形式排列來進行化簡。我們可以構建16x16門鎖矩陣(Latch Matrix),其中一共有256個,通過打開相應的行線和列線來啟用某個鎖存器。

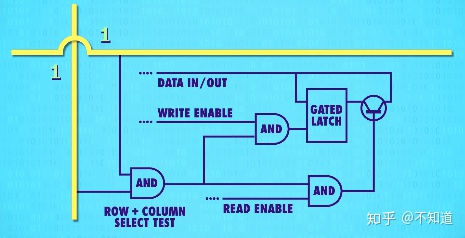

局部更大的細節如下圖所示。首先,只有當行列都為1時,設置WRITE ENABLE和READ ENABLE才有用,否則這兩條線的經過AND門的輸出始終為0。當WRITE ENABLE=1時,輸入數據就會保存在門鎖中。當READ ENABLE=1時,就會連通晶體管,將存儲在門鎖中的數據輸出。這里添加了一個READ ENABLE線來控制讀取,同時將輸入輸入和數據輸出線合并,從3條線減少為2條。并且由于每次能夠控制唯一一個鎖存器,所以所有的數據線可以合并成一條。也就是說,對于256位存儲,只需要一條數據線,一條允許寫入線,一條允許讀取線和16行16列的線用來選擇鎖存器,一共35條線。

由于16x16門鎖矩陣最多16行16列,所以可以分別用4位表示行和列的地址,就能用一共8位來定位一個鎖存器,比如“12行8列”可以表示為11001000。

為了將地址轉換成“行和列”,需要多路復用器(Multiplexer),多路復用器可以有不同的大小。當輸入一個4位數字,它就會將那根線連接到對應的輸出線,比如對列地址輸入0000,它就會選擇第一條線,輸入0001,就會選擇第二條線……有一個多路復用器處理行,一個多路復用器處理列,由此通過輸入行和列的坐標就能定位到對應的鎖存器了。

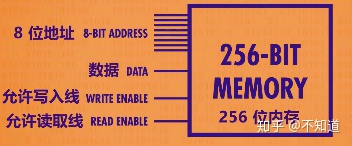

可以對256位寄存器進行封裝,它的輸入是一個8位地址,4位表示行,4位表示列,同時需要允許寫入線和允許讀取線,然后需要一條數據線用于讀寫數據。(注意:每次只能選擇一個鎖存器,所以數據線只能讀寫1bit數據)

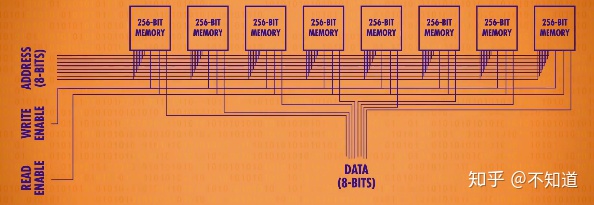

對其再進步一擴展,可以將8個256位內存拼在一起,這樣就能一次讀寫8bit數據,也就是一個字節數據。由于每個256位內存都使用相同的8位數據線,因此8位數據會存在每個256位內存的相同地址中,并且第一個256位內存存放第一位,第二個256位內存存放第二位,以此類推。這個模塊可以在256個地址中存儲256個字節。(由于這種設計,所以計算機中以一個字節為尋址的最小單位)

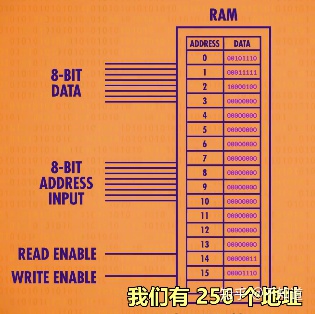

可以對其進行抽象,看成一個整體的可尋址內存,其中有256個地址,每個地址能讀寫一個字節的值。

現代計算機可以在此基礎上將內存擴展到MB和GB級別。我們這里使用8個16x16門鎖矩陣可以得到256字節的內存,然后可以用4位表示行4位表示列來進行尋址,由此可以將門鎖矩陣擴展到更大范圍,但是需要更多位來表示地址。所以對于nxn門鎖矩陣,存儲空間為

內存的一個重要特性是:能夠隨時訪問任何位置。所以稱為隨機存取寄存器(Random Access Memory, RAM)。RAM只記錄當前在做什么。

RAM中存儲的數據是保存在OR門其中一個電極上,所以斷電后就無法保存。

這一節用鎖存器做了一塊靜態隨機存取存儲器(Static Random-Access Memory,SRAM),還有很多其他類型的RAM,比如DRAM、閃存和NVRAM,它們的功能和SRAM相似,但是使用不同的電路存放單個位。但是根本上,這些技術都是矩陣層層嵌套來存儲大量信息。

)

...)

)