邏輯綜合工具Design Compiler使用教程

圖形界面design vision操作示例

邏輯綜合主要是將HDL語言描述的電路轉換為工藝庫器件構成的網表的過程。綜合工具目前比較主流的是synopsys公司Design Compiler,我們在設計實踐過程中采用這一工具。Design compiler有兩種工作模式,一種是tcl模式,另一種為圖形模式。在設計中為增強直觀性,采用圖形界面design vision。TCL命令行模式可在設計過程中摸索熟悉,并使之成為習慣。tcl模式在啟動工具之前,準備工作有四項:設計的HDL源文件、采用的工藝庫文件、設計的約束文件、工具的啟動文件。圖形界面模式最少需要前兩項,這里不作多說明。

1. 啟動工具

登陸Linux之后進入的目錄即是用戶的家目錄,在家目錄下建立dcLab作為本次實驗dc的操作主目錄。在dcLab目錄下,建立設計存放目錄如source、約束文件目錄如constrn、輸出網表文件目錄ntlst、報告輸出目錄rpt、log文件目錄log、dc啟動目錄work,等等。

實驗室中的工作站存放有umc公司和tsmc公司的0.18um標準單元庫的所有文件,存放在目錄:/usr/eda/designKit/下面,設計過程中需要查找的話注意路徑與示例中的圖片上所示路徑稍有不同。

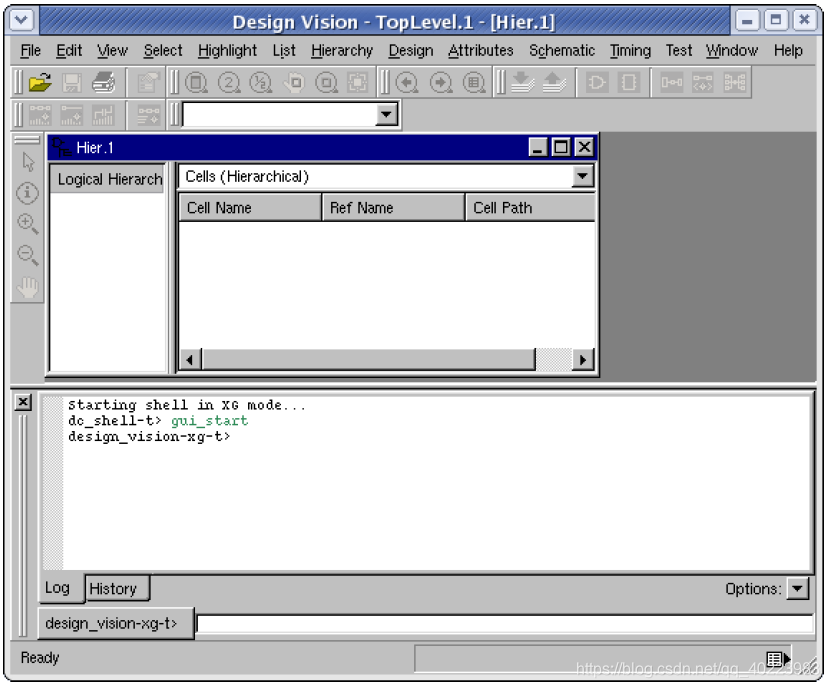

Design compiler工具在工作站中已經安裝完畢,且用戶的環境變量和license也已設置完成,登錄之后直接啟動工具即可。如果打開終端之后無法啟動工具,可能就是license沒有啟動,需要首先采用命令:start_slic啟動license,然后design vision才能正常開啟與工作。建立相關的工程目錄之后,進入本次實驗的工作目錄:~/dcLab/work后,采用啟動命令:design_vision&,啟動工具后相應的界面如下圖1所示。

在該界面中,最上方為菜單項和工具欄,用于設計過程中的各項操作。當窗口中選中不同的對象時,不同的菜單項和工具項會被激活。工具欄下面就是主窗口,用于顯示不同的設計對象、各種報告等。再下方為log/history窗口,log

頁面顯示操作響應,history界面回顯菜單操作相應的tcl命令,操作過程中一定要對照查看,盡快熟悉tcl模式。最下方有design_vision-xg-t提示的就是tcl命令輸入的位置,可以嘗試將history頁面的回顯鍵入,查看響應。

圖1 design vision啟動界面

啟動工具之后就可以工作了,主要可分為四部分內容:對工程進行啟動項設置、對設計進行面積/功耗/時序/環境/drc等約束、對設計進行綜合、查看報告并保存結果。

2. 配置工程啟動文件

工具啟動之后,需要設置相應的工程啟動文件,用于設定搜索路徑、相關庫文件等內容,對應工作目錄下的.synopsys_dc.setup文件(該文件應該位于工具啟動目錄~/dcLab/work下,dc啟動過程中會自動讀取該文件的內容用來配置工程啟動項。

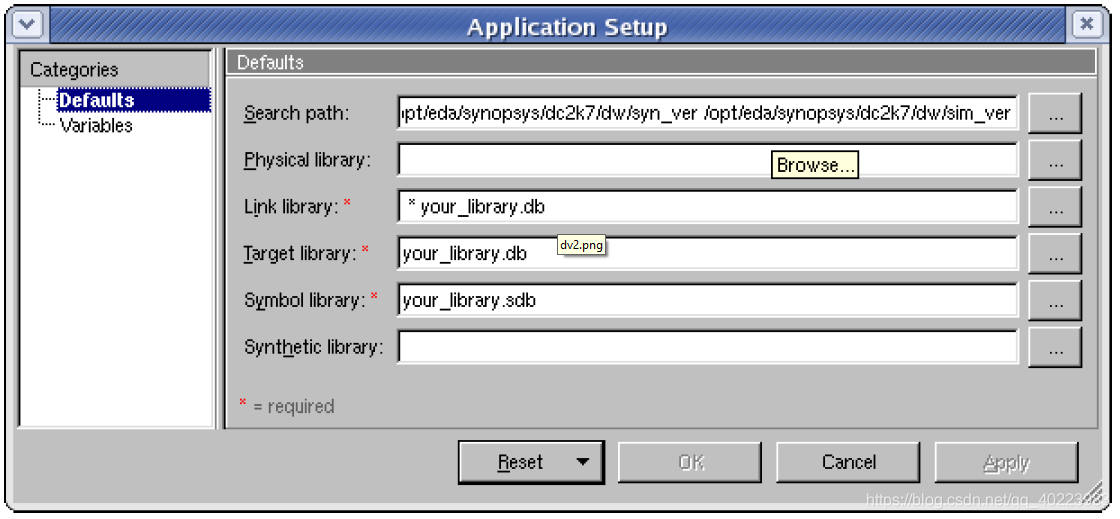

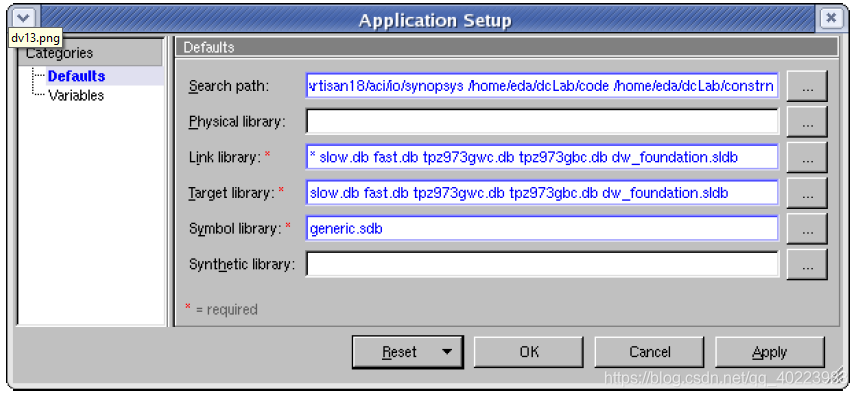

我們此時假設該文件不存在,當設置完成之后,可以將之保存,以后重啟工具就可以不必設置了)。選擇菜單項File—>Setup…,出現Application Setup窗口,如下圖2所示。啟動項相關的內容就在該表項中設置,用戶可以直接填入相關內容,或者點擊各欄右側的查找按鈕(標有…的小框)找到相應路徑或

者文件的位置。

圖2 setup設置窗口

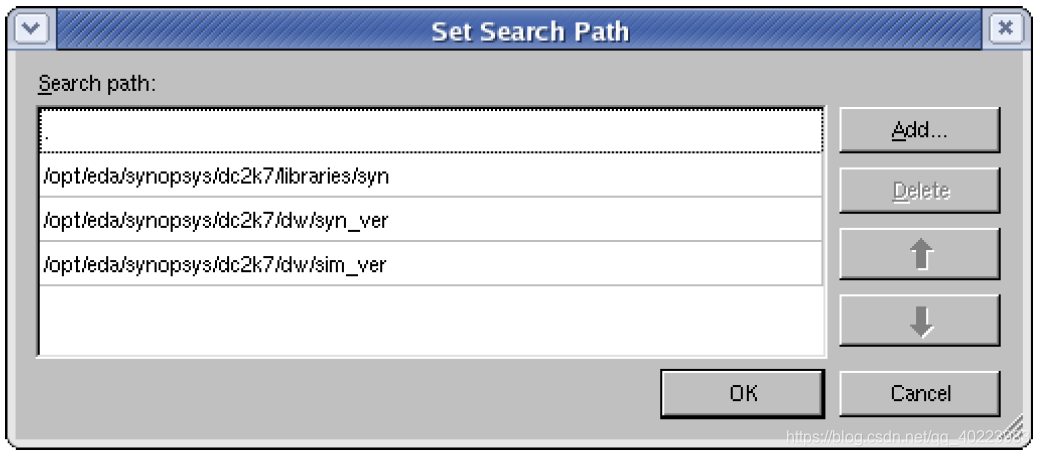

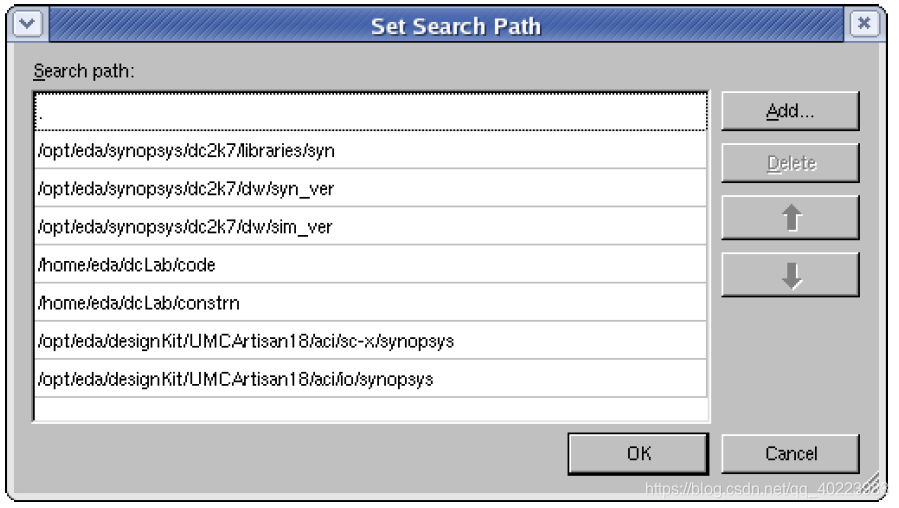

在該窗口中可以看到打有紅星()標號的項目是必須設置的,但是一般填上四項:search path、Link library、Target library*、symbol library*。首先來設置搜索路徑,該項主要用來指明設計中工具所需文件的路徑,應該包括源代碼文件路徑、工藝庫文件(如果源代碼有pad,則也應該包括pad庫文件所在路徑)、工具提供的中間庫文件(gtech、designWare)路徑、以及操作過程中需要讀取的中間文件所在路徑等。點擊search path條目右側的查找按鈕,就會出現set search path 表格窗口,如下圖3所示。

圖3 search path設置窗口

表格窗口已有的幾項保留不動,其中第一項的點符號(.)表示當前工作目錄,其余3項為工具提供的通用(gtech)庫、ip單元庫(design ware)以及符號(symbol)庫和仿真模型庫所在位置。點擊Add…按鈕,添加搜索路徑(注意

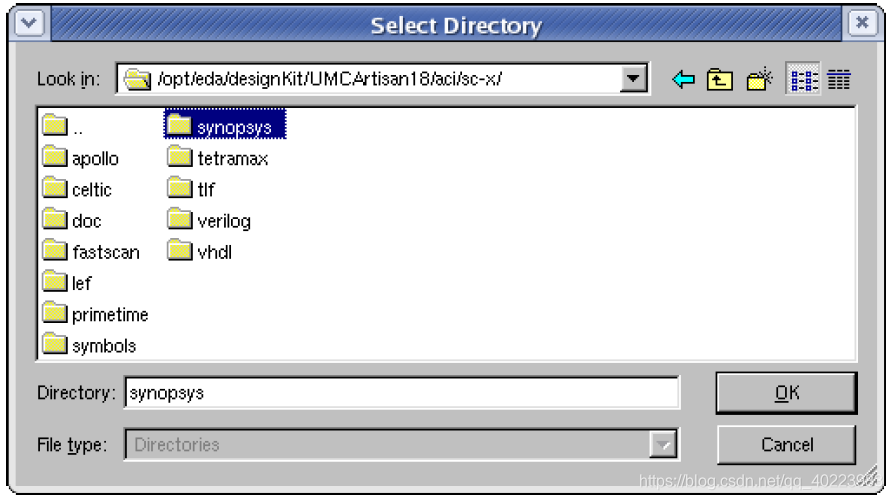

工作站上的軟件工具、庫文件均存放在/usr/eda目錄下,與本例位置/opt/eda/稍有不同),如下圖4所示。

圖4 添加search path窗口

選擇標準單元工藝庫所在的目錄,點擊OK完成一條搜索路徑的設置,回到圖3 界面,此時表格窗口中會多出一項剛剛添加的路徑。同樣,點擊Add…按鈕添加其余的搜索路徑:symbol所在路徑、設計代碼所在路徑、約束文件所在路徑、io工藝庫所在路徑等。完成路徑設置后,圖3 所示的search path設置窗口會變成如下圖5所示。點擊OK按鈕完成set search path工作。

圖5 完成search path的表格窗口

以上工作對應的tcl命令:set search_path “path”,其中path內容就是上

述的路徑(如”…/code …/constrn /usr/eda/designKit/umn18/sc-x/synopsys”)。

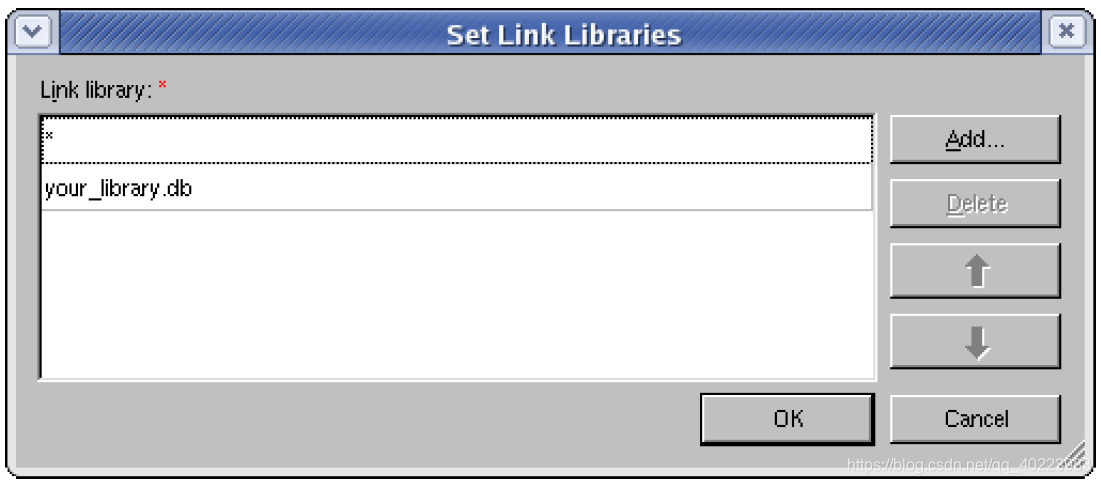

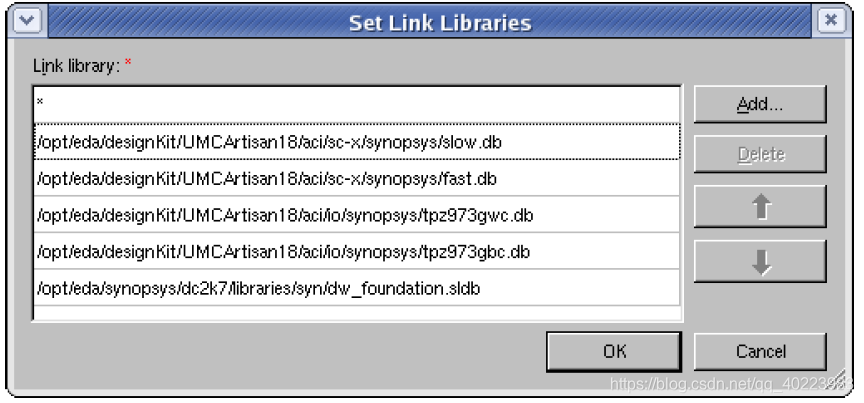

完成搜索路徑的設置后,要進行工藝庫相關的文件配置。其實配置好搜索路徑后可以直接將相應的庫文件寫入對應的表格項,同一項中各文件中間用空格分開即可。這里為了熟悉工具,仍然逐項查找填寫。在圖2界面中,點擊Link library右側的查找按鈕,出現Set Link Libraries的表格窗口,如下圖6所示。

圖6 鏈接庫的表格窗口

在上圖中第一項不要改動,表示的是鏈接對象為當前內存。同上面設置search path一樣,點擊Add…按鈕,查找庫文件(注意工作站上的路徑位置與本例不同),出現的界面如下圖7所示。

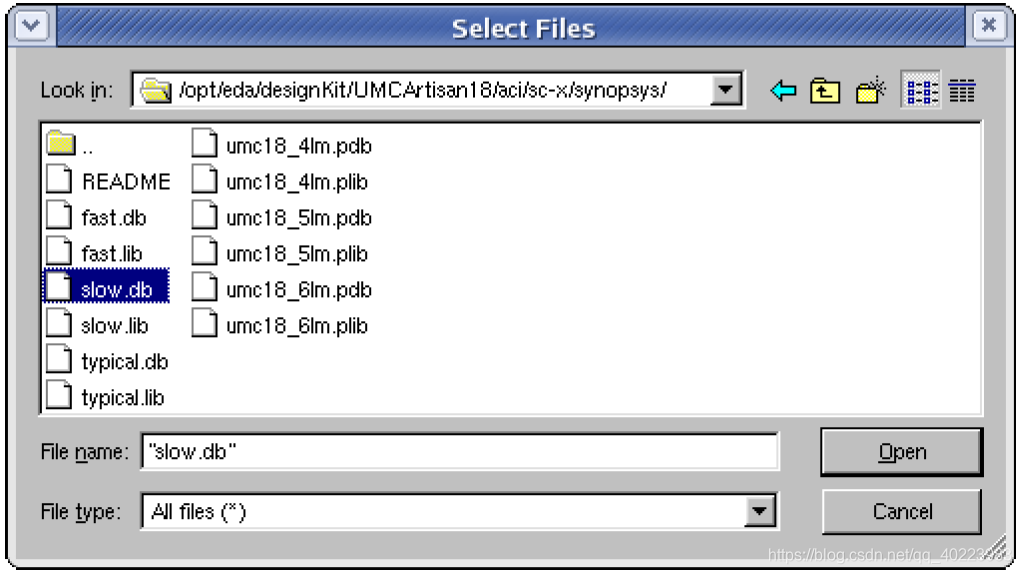

圖7 鏈接庫的查找與選擇

選中庫文件后(注意link library和后面的target library采用的是synopsys的數據庫文件格式db或者ddc,該文件是二進制格式;欲了解其內容可以察看

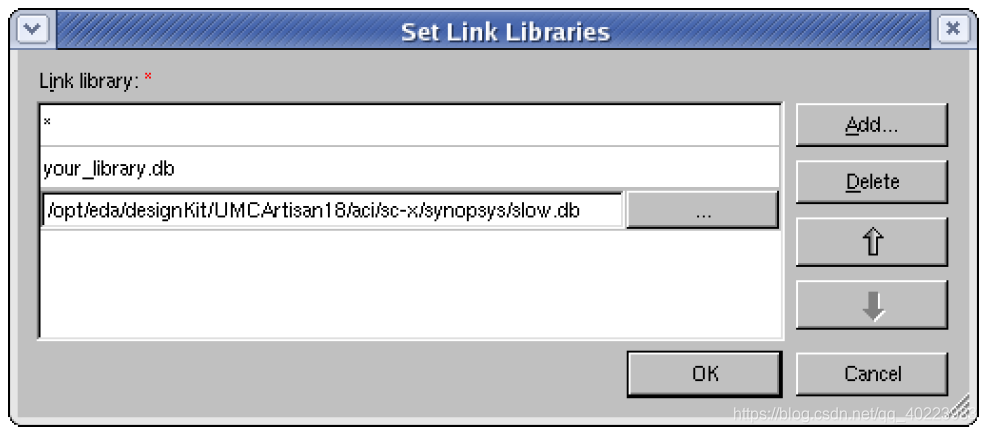

相對應的lib文本文件,試著讀一下會了解更多),點擊open按鈕,回到圖6的界面,其中增加了一項剛剛選擇的庫文件,如下圖8所示的界面,至此完成一個庫文件的設定。

圖8 選定slow.db鏈接庫

在標準單元庫中選定slow.db和fast.db兩個庫文件,io單元庫中也一樣。一般在邏輯綜合中最大延時是最重要的約束,因此也可以直接采用slow或者worst case庫,而不標明fast或者best case庫。本例中將其加上,主要用于對照時序報告察看二者的區別。

設置完成鏈接庫之后,形成如下圖9所示的表格圖窗,其中最后一項為工具自帶的design ware IP庫,用于復雜功能邏輯優化(?)。

圖9 鏈接庫文件選定圖窗

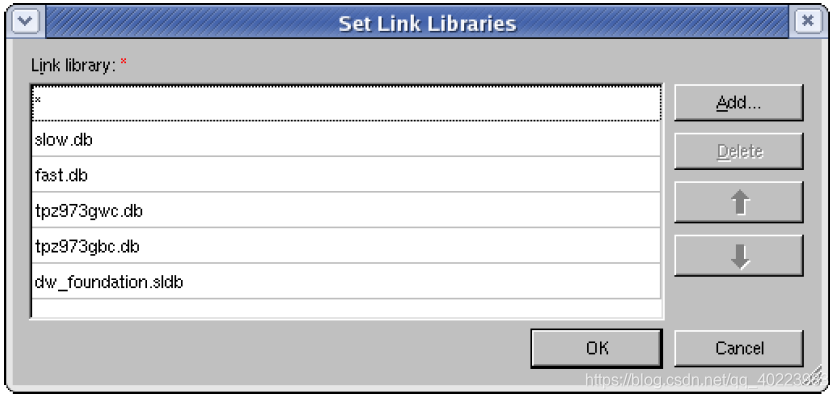

因為在前面設置了search path,其中包括了上述工藝相關庫的路徑,因此在設置link library和后面的target library的時候,可以直接寫上庫的文件名稱而略

去路徑,工具可以自動完成相應文件的搜索,去除路徑之后的鏈接庫文件如下圖10所示。

圖10 無路徑的鏈接庫文件選定圖窗

在上圖10或者圖9中,點擊OK按鈕完成連接庫的設定。設置鏈接庫的操作可以直接采用tcl命令set link_library ”library” 來完成,其中引號中的就是剛才設定的幾個庫文件,用空格分開,簡單吧。

目標庫的設定(target library)同link library操作一樣,而且除了沒有表示內存的星號(*)之外,內容也是完全一樣的。選定或者填寫結果如下圖11所示。

圖11 目標庫的設定圖窗

目標庫設置采用的tcl命令為:set target_library “lib”,其中lib的內容即為剛才設置的幾個庫文件(例“fast.db slow.db”)。

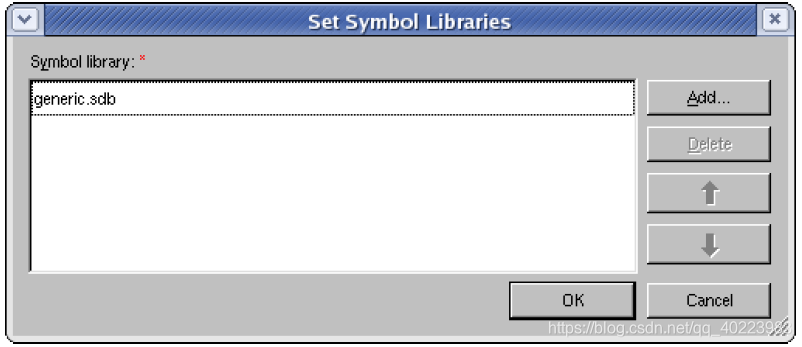

然后再進行符號(symbol)庫的設定,符號庫主要是用來在gui窗口中查看電路時使用的,表示基本單元器件的視圖。同target library一樣,也可以直接寫

入庫名,忽略路徑。因該umc庫中沒有symbol文件,故采用工具中自帶的symbol庫文件。選擇窗口、庫名稱見下圖12。

圖12 目標庫的設定圖窗

符號庫設置的tcl命令為:set symbol_library “lib”。在圖12中點擊ok按鈕,完成設置symbol庫。

至此setup內容已經完成設置,結果如下圖13所示。

圖13 setup設定窗口

在圖13中,點擊OK按鈕,完成啟動項內容的設置。隨后該設置可以在菜單命令中導出:File—>Save info—>Design Setup,將該文件保存為設計啟動配置文件.synopsy_dc.setup,直接放在work目錄下。下次再在該目錄下啟動工具的時候就不必重新配置,點擊File—>Setup…,就可以看到表格中的各項已經配置完成了。

3.設計讀入

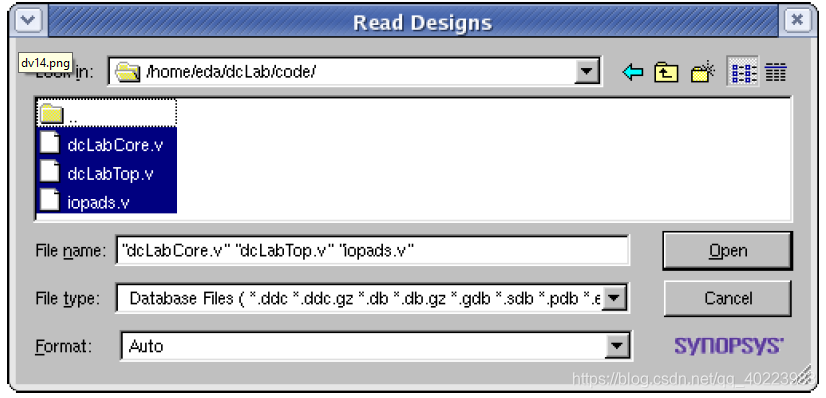

完成啟動項配置后就要將設計倒入工具,選擇菜單命令:File—>Read…,出現Read Design窗口。查找設計代碼所在路徑,選中所有需要的設計代碼,如下圖14所示。點擊Open按鈕,完成代碼讀入。

圖14 setup設定窗口

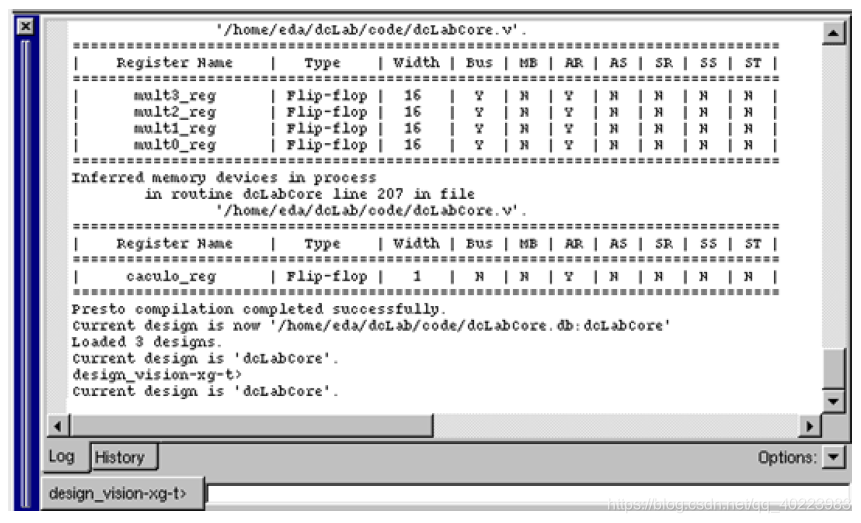

在讀入代碼的過程中,注意dv下方的log窗口回顯與報告,如下圖15。同時點選history鍵,查看相應的tcl命令:read(或者read_verilog)。

圖15 讀入設計時的窗口

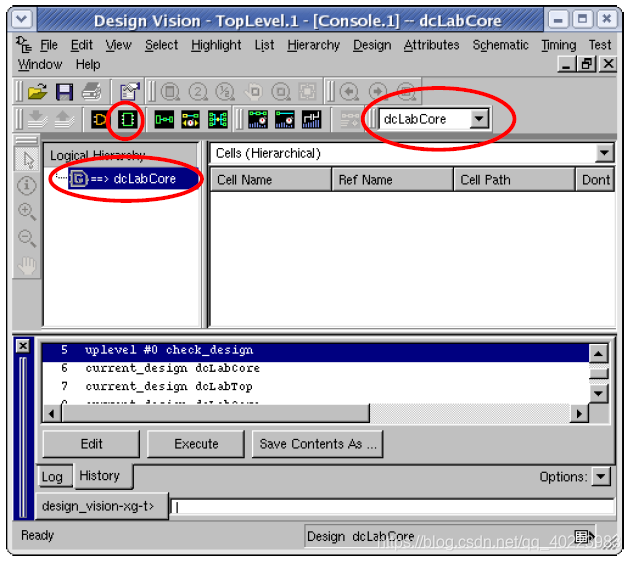

讀入設計之后,當前的設計會是讀如過程中最后一個代碼文件對應的設計,

要將頂層設計設為當前設計。在dv主界面的工具欄下方的工具條下下拉選項選中、設置當前設計,我們這里是dcLabCore。同樣注意history欄中的tcl命令:set current_design dcLabCore,記住對應的操作。

圖16 當前設計設定

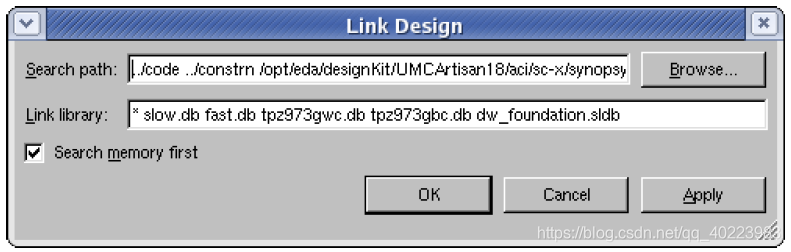

完成當前設計的設定后,以后的操作就是針對該設計進行的。下面要做的就是將設計與庫鏈接起來。選擇菜單命令:File—>Link Design。出現Link Design窗口,如下圖所示。注意Search path與Link library兩項與前述啟動項中的設置是否一致。

圖17 Link Design窗口

點擊OK按鈕完成設計與庫的鏈接。此時要注意log窗口的鏈接過程的操作回顯,及時修改錯誤與告警。

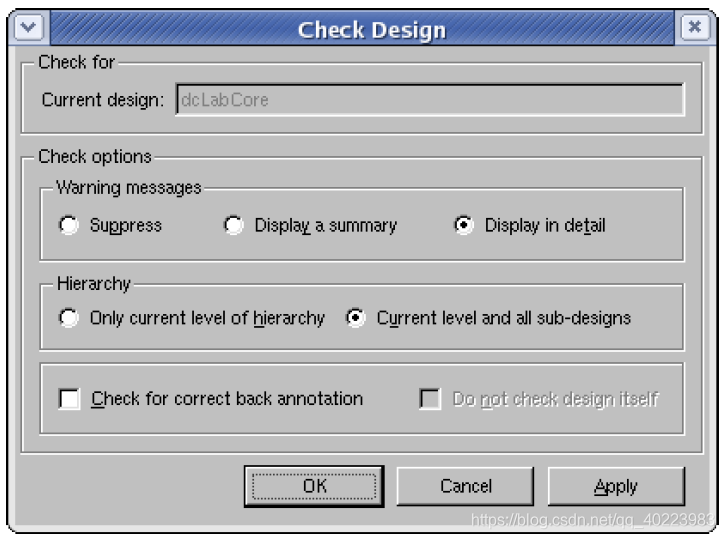

完成鏈接后要對設計進行檢查。選擇菜單命令:Design—>Check Design,出現如下窗口,點擊OK按鈕,對設計進行檢查。注意log欄中的報告。

圖18 Check Design窗口

至此,讀入設計的工作完成。在這過程中,源代碼中的各種與綜合相關的問題都會被檢查出來,注意隨時查看報告并修改直到被綜合器接受。下面就要對設計進行約束了。

4.設計約束與編譯

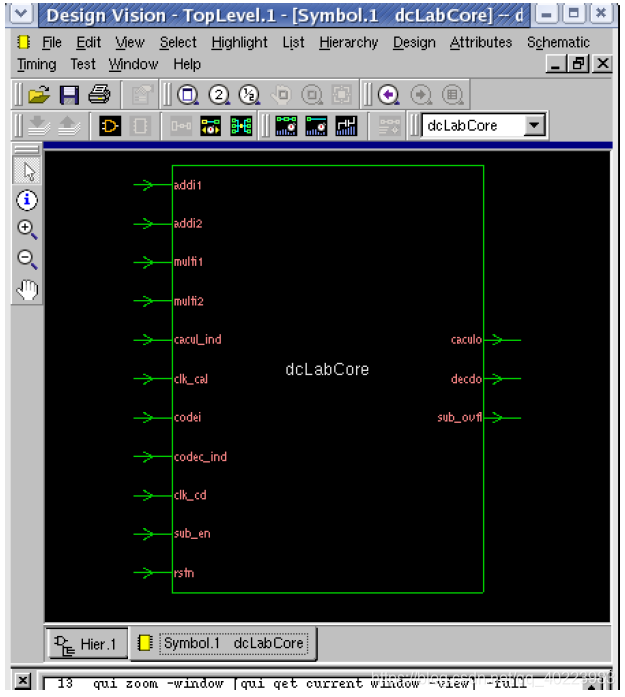

在dv的主界面中,因為已經讀入設計,此時很多菜單和工具欄已經激活。在圖16中,先選中Logical Hierarchy中的dcLabCore項,點擊工具欄中的Create Symbol View(或者菜單項Schematic—>New Symbol View 選項),出現當前設計的symbol,我們的約束就要在當前設計中添加。

這里之所以先創建一個symbol,因為很多設計的約束,比如創建時鐘(create clock)、輸入輸出延時(set input_delay/output_delay)、驅動與負載(set drive/load)、時鐘無關路徑(set false_path)等等,都是針對設計的端口的(port),圖形化的

界面操作起來容易些。得到的symbol如下圖19所示。

圖19 創建當前設計的symbol

首先創建時鐘,在symbol中選中clk_cal端口,然后選擇菜單項Attributes—> Specify Clock…,注意灰色的Port name項應該為clk_cal;如果不是,不要關閉Specify Clock窗口,再在symbol上選中該端口,就會發現port name相應改變。

時鐘的約束這里設定主要有四項,一項是時鐘的名稱,要方便易記、意義明確就好;二項是時鐘的周期,由頻率決定,這里clk_cal為50M,故周期20ns(時間單位在庫中定義);三項是時鐘的波形,定義一個時鐘周期內高電平所處的時間區間;四項是將時鐘網絡設定為don’t touch,也就是在綜合的過程中,時鐘線上不要添加包括驅動buffer在內的任何器件。時鐘信號clk_cal的選擇與填寫過

程如下圖20所示。

圖20 創建時鐘clk_cal

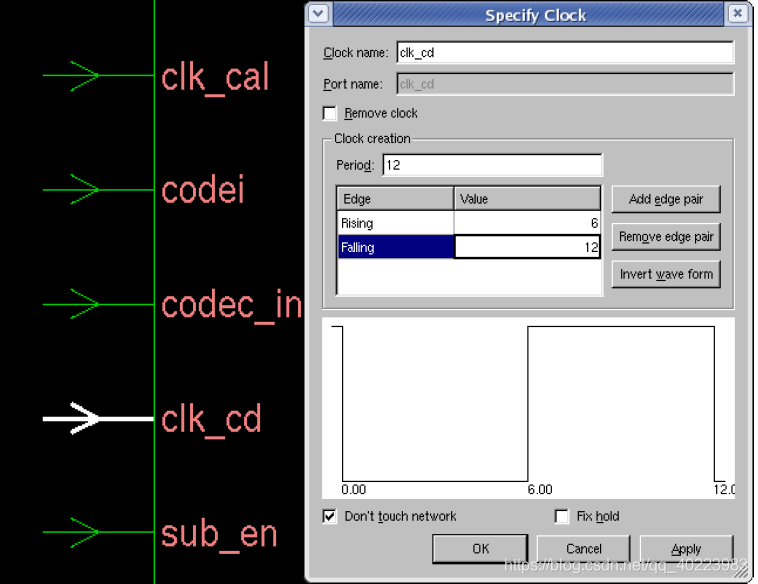

注意在Don’t touch network選項前打勾。點擊OK按鈕完成時鐘clk_cal的創建。時鐘的參數這里就不解釋了。同樣的方法創建時鐘clk_cd,如下圖。

圖21 創建時鐘clk_cd

時鐘信號clk_cd頻率80M,故此周期12ns,同clk_cal一樣,將上升沿設定在波形中間。以上操作對應tcl命令:create_clock。

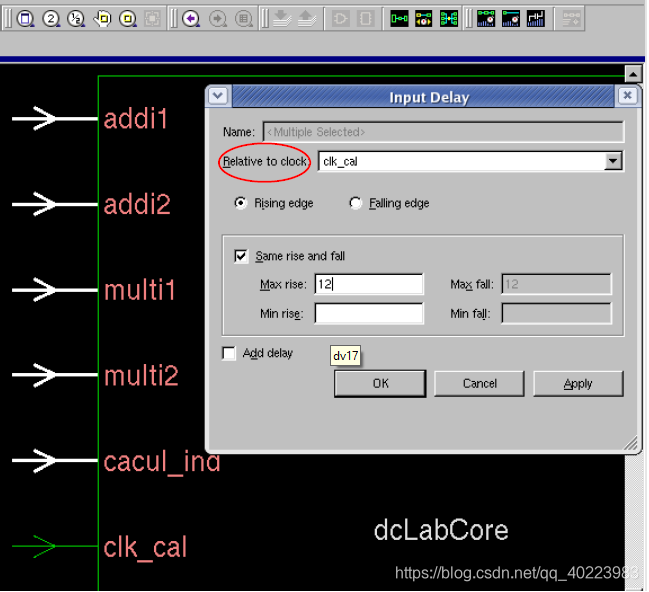

創建完成時鐘之后,就要進行輸入(set input_delay)和輸出延時(output_delay)的約束,因為該約束是相對于時鐘信號的。在symbol界面中,按住鍵盤ctr鍵,用鼠標選擇addi1/addi2/multi1/multi2/cacul_ind端口(因為這些端口是和同一時鐘clk_cal綁定的,設計中輸入由時鐘clk_cal驅動的觸發器中),選擇Attributes—> Operating Environment —>Input Delay菜單項,填寫、選中相應的項目。如下圖所示。

圖21 創建相對時鐘clk_cal的輸入延時

通常輸入延時計算為時鐘周期的60%,也就是說留出60%的外部裕量。注意圖中Relative to clock項的時鐘選擇要與設計中的定義一致。

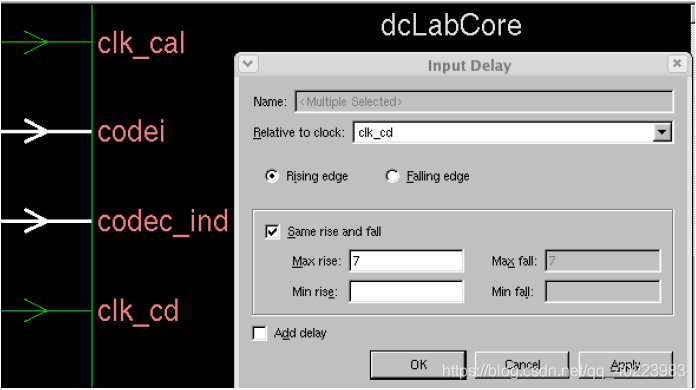

同樣完成相對于時鐘信號clk_cd的端口codei、codec_ind的輸入延時,選擇、填寫后的界面如下圖21所示。上述操作對應的tcl命令為:set input_delay “port”,

其中port即為相應于時鐘的端口。

圖21 創建相對時鐘clk_cd的輸入延時

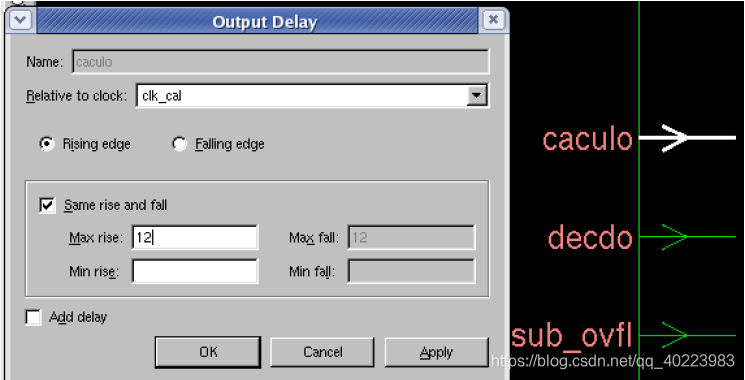

完成輸入延時之后進行輸出延時的設定(output_delay)。選中symbol中的端口caculo(它是由時鐘信號clk_cal驅動輸出),選擇菜單項Attributes —> Operating Environment —>Output Delay,填寫、選擇如下圖的內容,點擊Apply按鈕完成設置。

圖21 創建相對時鐘clk_cal的輸出延時

同樣完成輸出信號decdo的輸出延時的設定,注意該信號是和時鐘clk_cd綁定的。以上操作定應tcl命令:set output_delay。

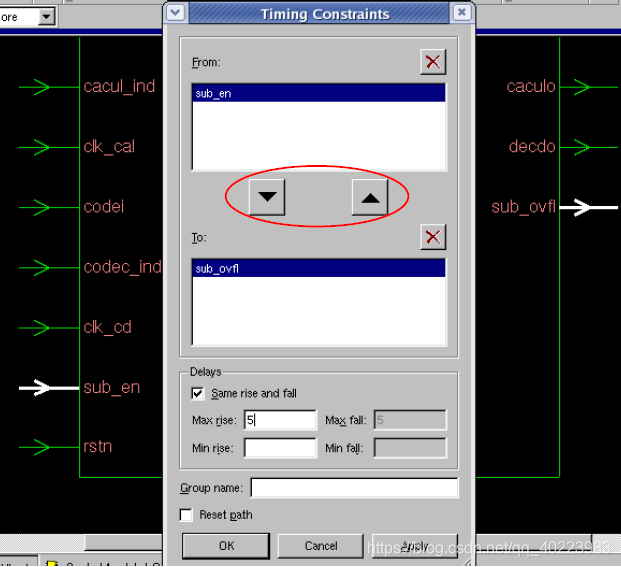

現在除了輸入信號sub_en和輸出信號sub_ovfl以外,所有的信號(除rstn)都進行了約束。現在來進行余下這兩個端口信號的約束。在symbol中選中這兩個端口,選擇菜單項Attributes—>Optimization Constraints—>Timing Constraints,出現Timing Constraints窗口,如下圖所示選擇填寫,完成約束。對應的tcl命令為:set max_delay。

圖22 約束輸入與輸出間的最大延時

這里采用set max_delay的方法是因為輸入端口信號sub_en到輸出信號端口sub_ovfl之間沒有時序邏輯,只有組合邏輯,因此要約束輸入端口到輸出端口之間的最大延時(最小延時除非有需要,否則可以不加以約束)。

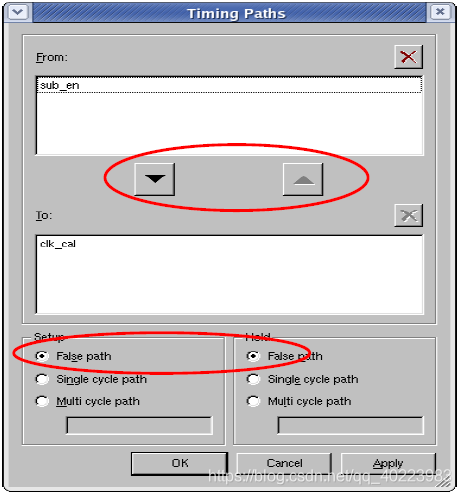

時序約束中還需要將無關路徑區分開來,采用set_false_path的方法。所謂無關路徑,就是告訴綜合器某兩條或者多條路徑之間沒有時序關系,可以不必理會、優化這些路徑間的電路。設計中。sub_en端口的信號送入純組合邏輯,而且與時鐘clk_cal和clk_cd不存在相位依賴關系,故此這里設置為false path。在symbol界面中選定sub_en端口和clk_cal、clk_cd端口,選擇菜單項:Attributes

—>Optimization Directive—>Timing Paths,出現如下窗口,From欄中留有sub_en項,To欄中留有clk_cal和clk_cd兩項,選中False path項。

圖23 無關路徑設置

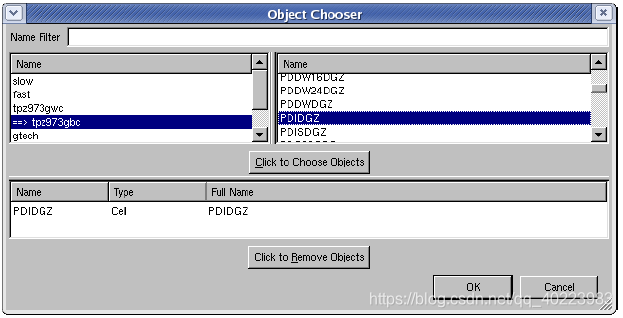

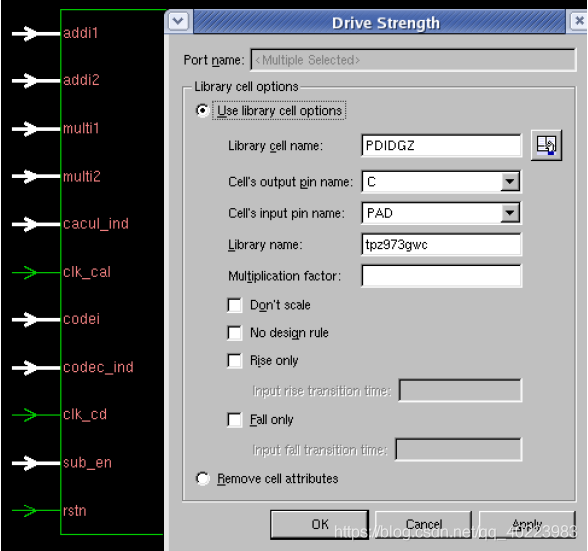

下面來設置驅動與負載(drive/load)。首先選中symbol中的輸入信號端口,如下圖所示。選擇菜單項Attributes—> Operating Environment—>Drive Strength,出現Drive Strength窗口。按照下圖填寫、選擇相應的內容,完成驅動設置。

圖24-a 配置輸入驅動

圖24-b 配置輸入驅動

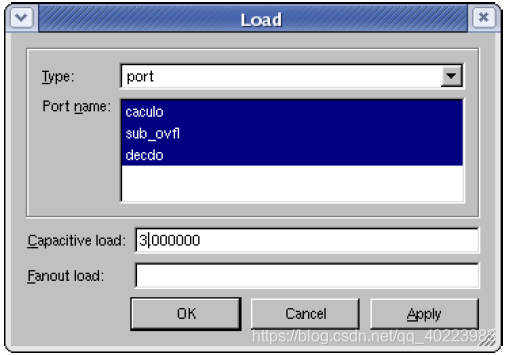

在symbol界面選中三個輸出端口,選擇菜單項Attributes—> Operating Environment—>Load,出現Load窗口。注意選中三個輸出信號端口。在Capacitive load欄中填容性負載數值。

圖25 輸出負載約束

以上操作對應tcl命令:set drive/load。

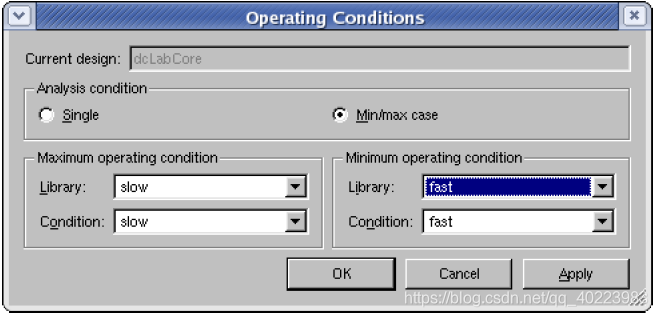

現在來設置操作環境(Operating Conditions)的設置。選擇菜單項Attributes—> Operating Environment—> Operating Conditions,出現如下窗口。

圖26 操作環境的設置

按照圖示選擇相應的內容,按按鈕OK完成操作環境的設置。對應的tcl命令為:set operating_conditions。

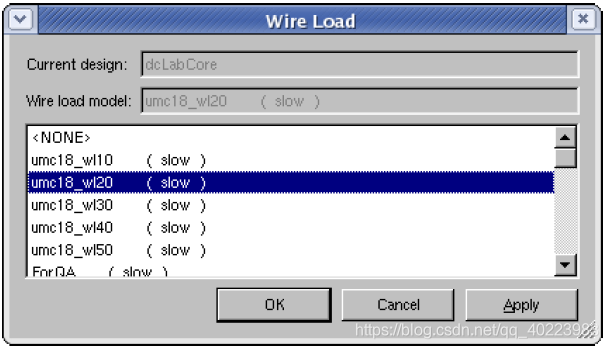

同樣的,完成wire Load的設置:選擇Attributes—> Operating Environment—> Wire Load菜單項,選擇umc18_wl20模型。對應的tcl命令:set wire_load。

圖27 線載模型的設置

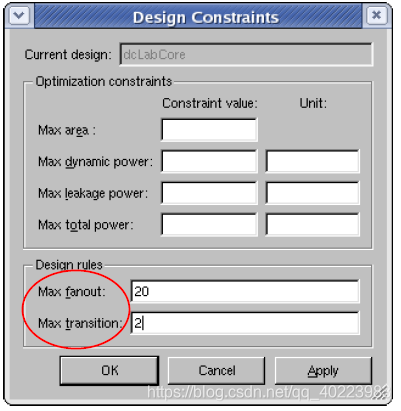

下面進行design rule的設定,主要是fanout和transition。選擇菜單項Attributes—> Optimization Constraints—> Design Constraints,出現下圖所示界面,只填寫圖示的兩項即可。對應的tcl命令:set max_fanout/transition。

圖28 fanout與transition的設置

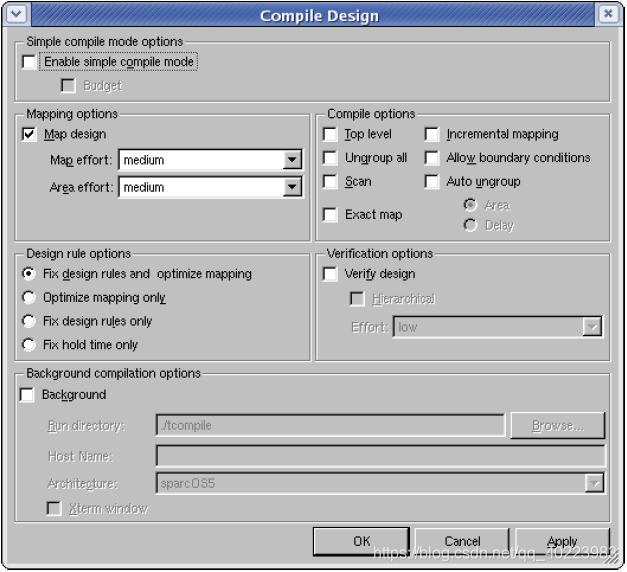

至此,設計相關約束設置完成,可以對設計進行綜合了。選擇菜單項Design—> Compile Design,出現設計編譯窗口,如圖選擇,點擊OK按鈕編譯設計。

圖29 設計編譯界面

編譯的過程會隨著設計的復雜變慢,編譯的過程中注意log窗口的輸出。完成編譯后,需要查看各種報告。

5.查看報告與設計輸出

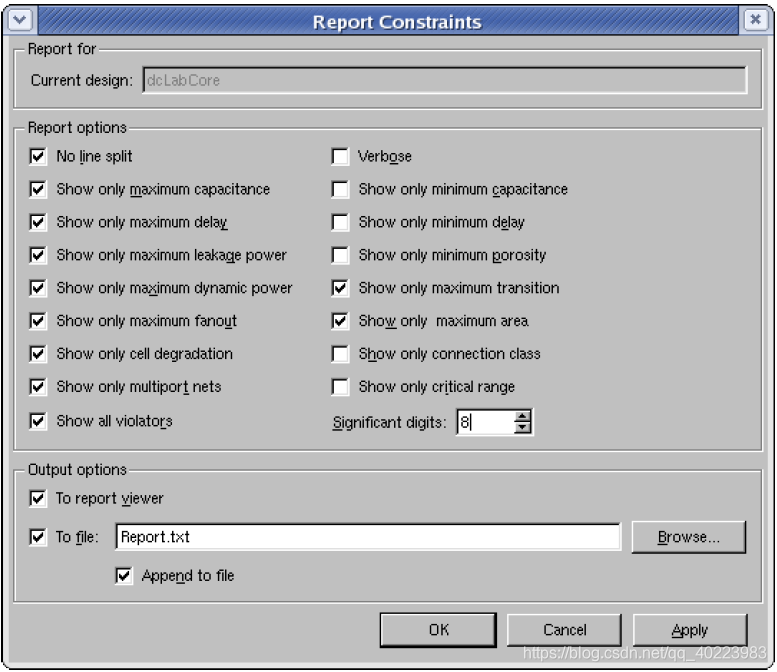

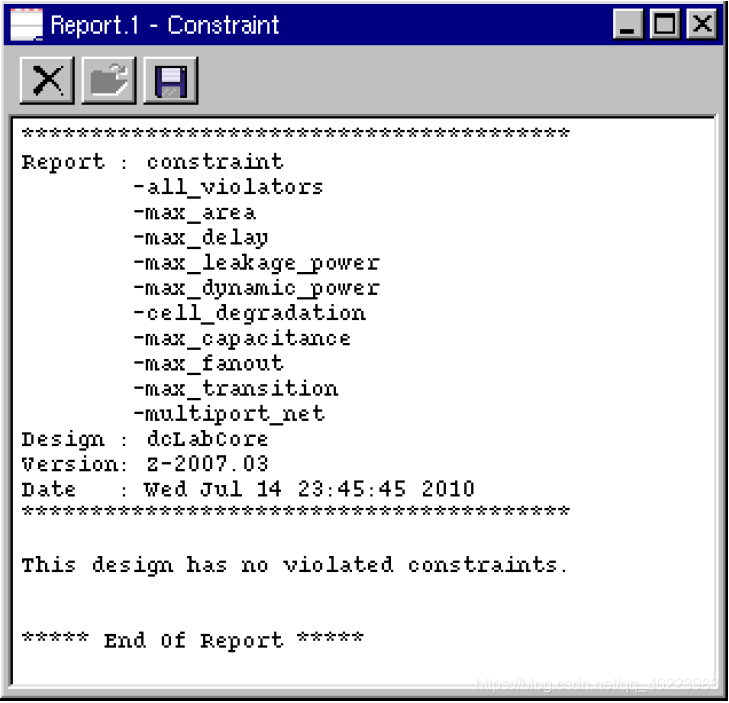

很多時候綜合并不是一次就通過的,在這過程中有可能時序不滿足約束要求,或者約束設置的不合理,或者設計本身有問題等,需要查看報告、調試。這里最重要的一個報告是約束報告。選擇菜單項Design—>Report Constraints,出現如下圖30所示的界面。

圖30 約束報告選擇界面

勾選想要查看的內容,點擊OK按鈕,可以看到與約束相關的報告。簡單的一個報告如下圖31所示。

查看報告的選項大多位于菜單Design和Timing之下。在完成綜合之后,如果Report Constraints沒有發現錯誤和不期望的告警,可以嘗試將這些報告項輸出,具體查看一下,非常有助于了解設計、熟悉工具。同時可以對照庫中的.lib

文件查看一些參數。

圖31 約束報告結果

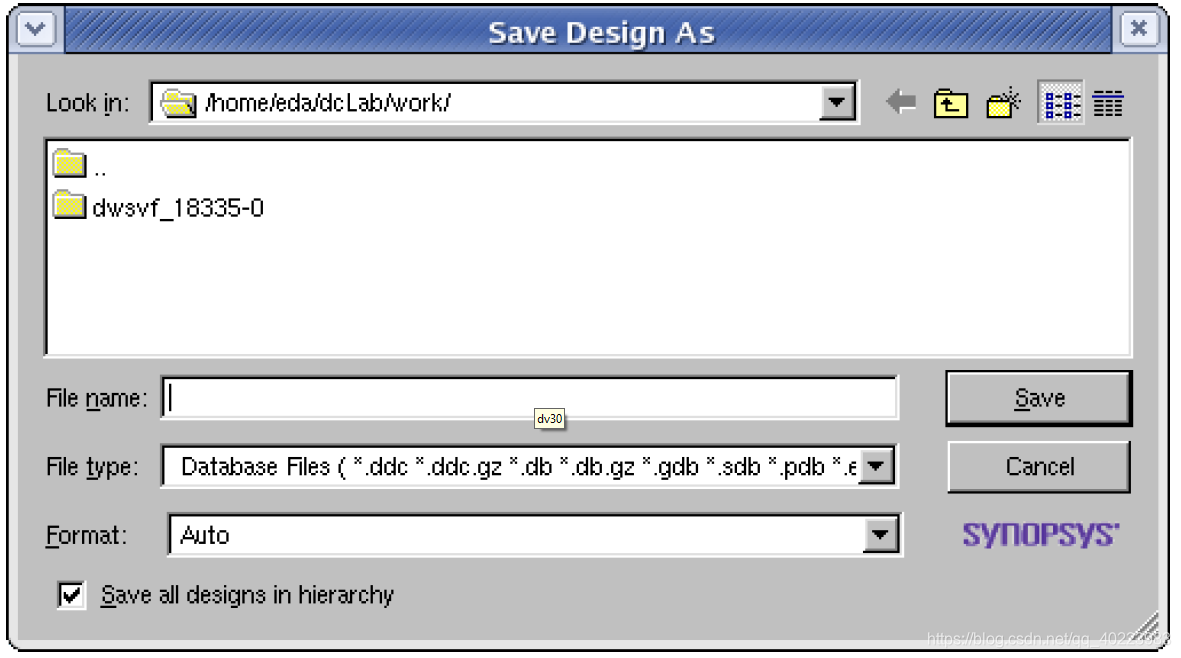

如果沒有報告錯誤,就可以將設計保存下來。選擇菜單項File—>Save as,可以將設計保存為各種格式。

圖32 保存設計界面

同樣可以保存啟動項文件和約束文件:選擇菜單項File—>Save info—> Constraints/Design setup,保存相應文件。

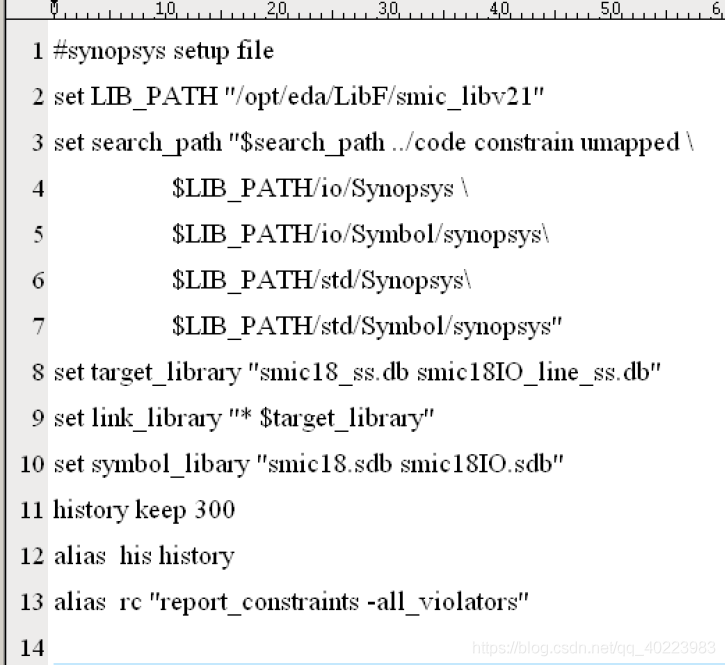

6..synopsys_dc.setup文件與dcLab.con文件

a. 啟動項文件

文件.synopsys_dc.setup應位于當前的工作目錄中,Linux/Unix下為隱含文件。這里先給出一典型的.synopsys_dc.setup文件,如下所示。

文件.synopsys_dc.setup第一項內容設定工具工作過程中需要搜索的路徑位置(search_path),一般包括源代碼的目錄、庫文件(工藝庫模型文件、symbol文件)的目錄、約束/運行腳本的目錄、某些中間文件的目錄以及在工具的安裝目錄配置的啟動搜索目錄,包括gtech庫等目錄。

文件.synopsys_dc.setup第二項內容一般用來設定目標庫(target_library),也就是工藝庫的名稱,綜合過程中工具會自動在搜索目錄中尋找,來完成綜合工作。第三項內容一般用來設定鏈接庫(link_library),用于解析設計電路中的最小顆粒單元,其中,*,用來表示內存。

文件.synopsys_dc.setup第四項內容用來設定symbol庫,也就是design vision

可以看到的網表圖形。其余的內容還可以包括命名規則、別名定義等,可以任意設定,示例中沒有一一給出。

b.設計的約束文件

約束文件主要用于優化設計電路的,主要內容有:讀入/分析源文件、設定設計的工作條件/環境/設計規則、時序條件、面積約束、綜合策略等。

首先是讀入源代碼,也就是HDL文本描述的設計文件,此處不用制定目錄,design compiler會在搜索目錄($search_path)中搜索。tcl語句如下:

read_verilog {dcLabCore.v dcLabTop.v iopads.v}

讀入設計原文件后,一般設定當前設計,這樣約束條件才可有針對性施加:

current_design dcLabCore

設定當前設計后,要完成鏈接,也就是將設計與庫鏈接起來,用于映射過程中搜尋相應的單元,完成綜合。tcl語句: link

檢查設計,主要是檢查完成轉換(translate)的設計: check_design。然后設定輸出網表的格式規則,輸出未優化的設計:

set verilogout_no_tri true

change_names -rule verilog -hier

write -f ddc -hier –out ../output/dcLabCore.ddc

然后對設計設定時序約束,這是最重要的一項約束,用于設定設計的工作速度的。針對不同的設計部分,有不同的約束方法。這里假設設計為全同步設計,單時鐘工作,復雜情況參考design compiler的手冊即可。以下語句設定時鐘及屬性、輸入信號的時間裕量:

create_clock –name clk_cal -period 20 [get_ports clk_cal]

#名稱clk_cal,對應端口clk_cal,50M工作頻率

set_clock_uncertainty -setup 0.2 [get_clocks clk_cal] #時鐘的不確定時間

set_clock_latency -source -max 0.3 [get_clocks clk_cal]#時鐘輸入延時

set_clock_latency -max 0.1 [get_clocks clk_cal]#時鐘延時

set_clock_transition -max 0.2 [get_clocks clk_cal]#時鐘上升/下降時間

set_dont_touch_network [get_ports "clk* rstn"]

#不對時鐘復位信號優化

set_ideal_network [get_ports "clk* rstn"] #延時分析時認為時鐘復位無延時

set_input_delay -max 12 -clock clk_cal [get_ports "add* mult*"]#輸入信號裕量

set_output_delay -max 12 -clock clk_cal [get_ports "caculo"] #輸出時間裕量

完成時序約束后,要對設計的工作環境、設計規則等進行約束,如下約束語句:

set_wire_load_mode top

#設定線載模型的模式

set_wire_load_model -library slow -name umc_wl20 -max

#線載模型,要粗略綜合一下估出面積,再設定

以下是設計規則的約束:

set_driving_cell -lib_cell FFEDQHD4X -pin Q [get_ports all_inputs]

#驅動能力的約束

set max_cap [expr [load_of slow/AND2HD4XSPG/A] * 5]

set_load [expr 3 * $max_cap] [all_outputs] #設計負載設定

set_fanout_load 10 [all_outputs] #扇出負載

然后是綜合的策略,簡單的設計比較容易,這里不展開:

compile -map_effort medium -incremental_mapping

輸出綜合報告、輸出綜合網表、綜合數據以及標準延時文件:

rc > log/rc.log #時序報告

write -f verilog -hier -out output/dcLabTop.sv #輸出網表

write -f ddc -hier -out output/dcLabTop.ddc#綜合數據文件

write_sdf -version 2.1 mapped/light_controller.sdf #標準延時文件

上述內容為約束文件主要內容,同學們可以講示例中的約束保存下來自己細看一下。

——結構體變量)

)

![[hadoop] kettle spoon 基礎使用 (txt 內容抽取到excel中)](http://pic.xiahunao.cn/[hadoop] kettle spoon 基礎使用 (txt 內容抽取到excel中))

![【BZOJ 4103】 [Thu Summer Camp 2015]異或運算 可持久化01Trie](http://pic.xiahunao.cn/【BZOJ 4103】 [Thu Summer Camp 2015]異或運算 可持久化01Trie)

:監控隊列狀態)

![[JSOI2008]最小生成樹計數](http://pic.xiahunao.cn/[JSOI2008]最小生成樹計數)

)